Linux Foundation will open source chips

Linux Foundation opened a new direction - the CHIPS Alliance. Within the framework of this project, the organization will develop a free system of RISC-V commands and technologies for creating processors based on it. Tell us more about what is happening in this area.

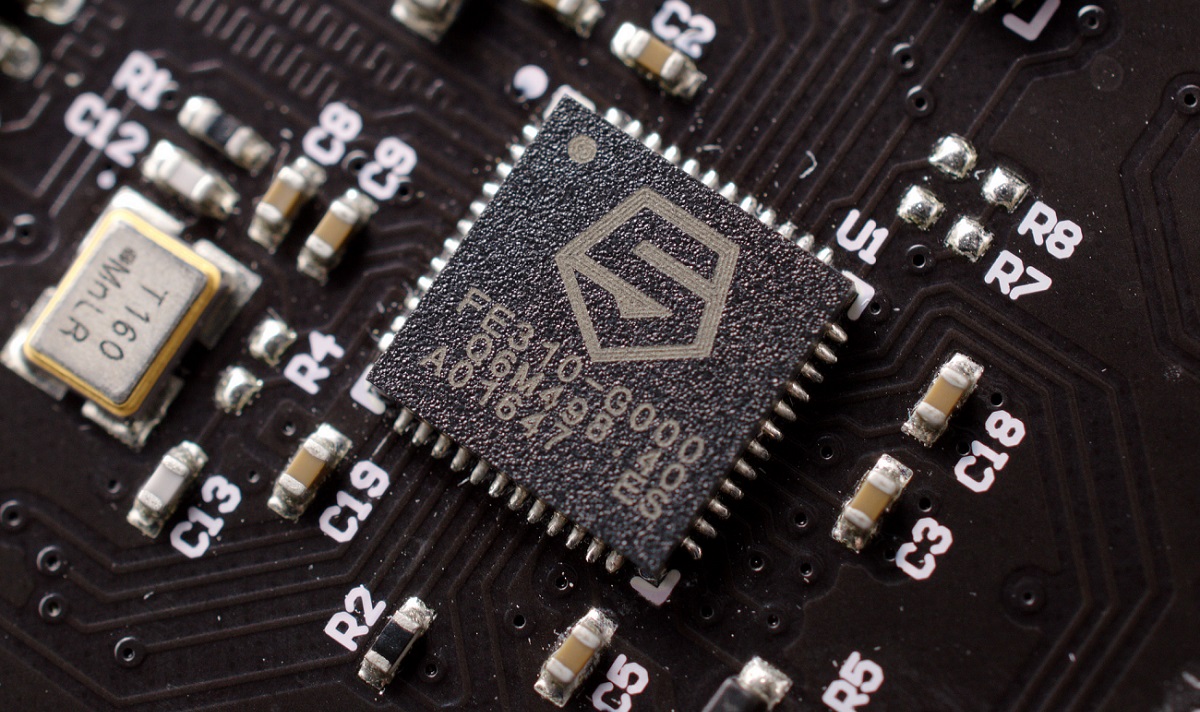

/ photo Gareth Halfacree CC BY-SA

The patches that protect against Meltdown and Specter, in some cases, reduce server performance by 50%. At the same time, new variations of vulnerabilities associated with speculative execution of commands still appear. One of them became known in early March - the information security specialists dubbed it Spoiler. This situation influences the discussion of the need to revise existing hardware solutions and approaches to their development. In particular, Intel is already preparing a new architecture for its processors, not subject to Meltdown and Specter.

')

Do not stand aside and in the Linux Foundation. The organization launched its own initiative - the CHIPS Alliance - whose members will be engaged in the development of processors based on RISC-V.

The search IT giant has transferred to open source a platform for testing processors based on RISC-V. The solution randomly generates commands that allow you to check the performance of the device: test the transition processes, the call stack, CSR registers, etc.

For example, this is the class that is responsible for conducting a simple test of arithmetic instructions:

According to the developers, the platform differs from the analogs in that it allows to successively check all the components of the chip, including the memory block.

This is a network protocol from WD that provides cache coherence when transferring data over Ethernet. OmniXtend allows you to exchange messages directly with the processor's cache and is used to connect various kinds of accelerators: GPU or FPGA. It is also suitable for building systems based on several RISC-V chips.

The protocol is already supported by SweRV chips , focused on data processing in data centers. SweRV is a 32-bit dual-pipeline superscalar processor, made on 28-nanometer process technology. Each pipeline has nine levels, which makes it possible to load and execute several commands simultaneously. The device operates at a frequency of 1.8 GHz.

The solution from the company SiFive, which was founded by developers of technology RISC-V. Rocket Chip is a Chisel RISC-V core generator. It is a set of parameterized libraries that are used to create SoC .

As for Chisel , this is Scala based hardware description language. It generates low-level code on Verilog, which is suitable for processing on ASIC and FPGA. Thus, it allows you to use the principles of OOP in the development of RTL .

Experts say the Linux Foundation initiative will make the processor market more democratic and open to new players. IDC notes that the growing popularity of such projects will have a positive impact on the development of machine learning technologies and AI systems as a whole.

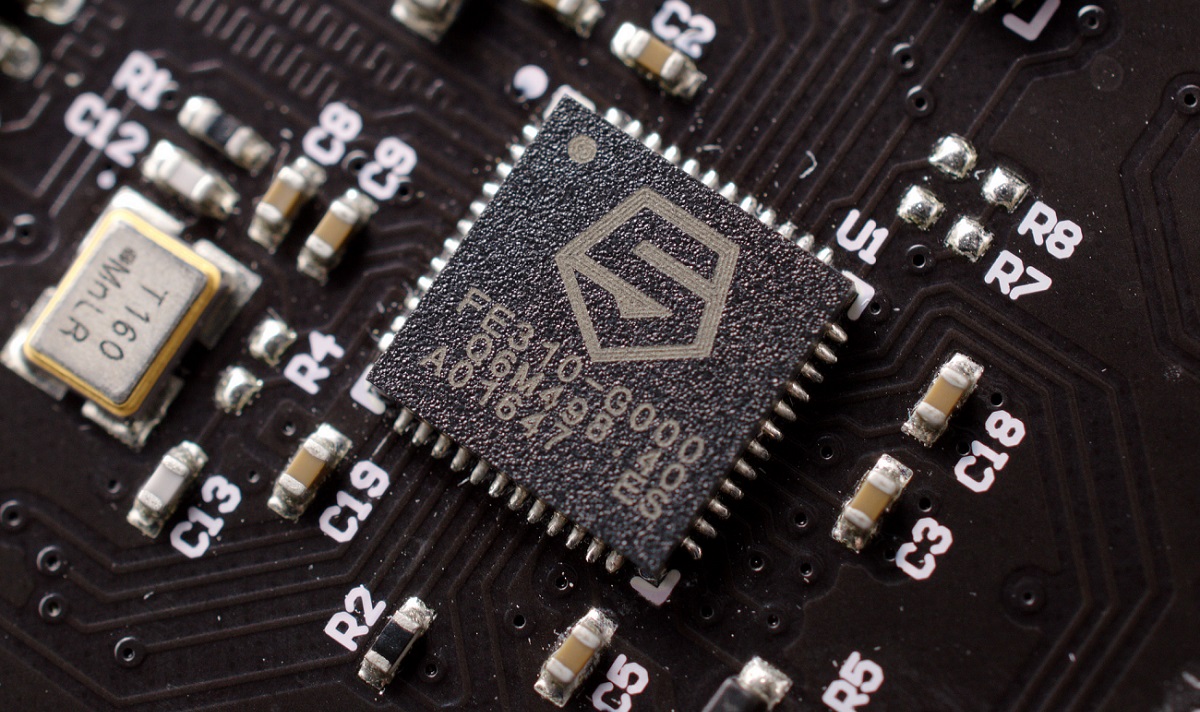

/ photo Fritzchens Fritz PD

The development of open source processors will also reduce the cost of designing custom chips. However, this will only happen if the Linux Foundation community succeeds in attracting a sufficient number of developers.

Other organizations are also involved in developing projects related to open source hardware. An example would be the CXL consortium, which introduced Compute Express Link in mid-March. The technology is similar to OmniXtend and also connects the CPU, GPU, FPGA. For data exchange, the standard uses a PCIe 5.0 bus.

Another project dealing with the development of processor technology is the MIPS Open, which appeared in December 2018. The initiative was created by the startup Wave Computing. Developers plan to open access to the latest 32-bit and 64-bit MIPS instruction sets for the IT community. Start of the project is expected in the coming months.

In general, open source approach is becoming common not only for software, but also for hardware. Such projects are supported by large companies. Therefore, it can be expected that in the near future more devices will appear on the market based on open hardware standards.

Recent posts from our corporate blog:

Posts from our Telegram channel:

/ photo Gareth Halfacree CC BY-SA

Why did the CHIPS Alliance

The patches that protect against Meltdown and Specter, in some cases, reduce server performance by 50%. At the same time, new variations of vulnerabilities associated with speculative execution of commands still appear. One of them became known in early March - the information security specialists dubbed it Spoiler. This situation influences the discussion of the need to revise existing hardware solutions and approaches to their development. In particular, Intel is already preparing a new architecture for its processors, not subject to Meltdown and Specter.

')

Do not stand aside and in the Linux Foundation. The organization launched its own initiative - the CHIPS Alliance - whose members will be engaged in the development of processors based on RISC-V.

What projects are already developing

In the list of participants of the CHIPS Alliance - Google, Western Digital (WD) and SiFive. Each of them presented their own development. We will tell about some of them.

RISCV-DV

The search IT giant has transferred to open source a platform for testing processors based on RISC-V. The solution randomly generates commands that allow you to check the performance of the device: test the transition processes, the call stack, CSR registers, etc.

For example, this is the class that is responsible for conducting a simple test of arithmetic instructions:

class riscv_arithmetic_basic_test extends riscv_instr_base_test; `uvm_component_utils(riscv_arithmetic_basic_test) `uvm_component_new virtual function void randomize_cfg(); cfg.instr_cnt = 10000; cfg.num_of_sub_program = 0; cfg.no_fence = 1; cfg.no_data_page = 1'b1; cfg.no_branch_jump = 1'b1; `DV_CHECK_RANDOMIZE_WITH_FATAL(cfg, init_privileged_mode == MACHINE_MODE; max_nested_loop == 0;) `uvm_info(`gfn, $sformatf("riscv_instr_gen_config is randomized:\n%0s", cfg.sprint()), UVM_LOW) endfunction endclass According to the developers, the platform differs from the analogs in that it allows to successively check all the components of the chip, including the memory block.

OmniXtend protocol

This is a network protocol from WD that provides cache coherence when transferring data over Ethernet. OmniXtend allows you to exchange messages directly with the processor's cache and is used to connect various kinds of accelerators: GPU or FPGA. It is also suitable for building systems based on several RISC-V chips.

The protocol is already supported by SweRV chips , focused on data processing in data centers. SweRV is a 32-bit dual-pipeline superscalar processor, made on 28-nanometer process technology. Each pipeline has nine levels, which makes it possible to load and execute several commands simultaneously. The device operates at a frequency of 1.8 GHz.

Rocket Chip Generator

The solution from the company SiFive, which was founded by developers of technology RISC-V. Rocket Chip is a Chisel RISC-V core generator. It is a set of parameterized libraries that are used to create SoC .

As for Chisel , this is Scala based hardware description language. It generates low-level code on Verilog, which is suitable for processing on ASIC and FPGA. Thus, it allows you to use the principles of OOP in the development of RTL .

Alliance perspectives

Experts say the Linux Foundation initiative will make the processor market more democratic and open to new players. IDC notes that the growing popularity of such projects will have a positive impact on the development of machine learning technologies and AI systems as a whole.

/ photo Fritzchens Fritz PD

The development of open source processors will also reduce the cost of designing custom chips. However, this will only happen if the Linux Foundation community succeeds in attracting a sufficient number of developers.

Similar projects

Other organizations are also involved in developing projects related to open source hardware. An example would be the CXL consortium, which introduced Compute Express Link in mid-March. The technology is similar to OmniXtend and also connects the CPU, GPU, FPGA. For data exchange, the standard uses a PCIe 5.0 bus.

Another project dealing with the development of processor technology is the MIPS Open, which appeared in December 2018. The initiative was created by the startup Wave Computing. Developers plan to open access to the latest 32-bit and 64-bit MIPS instruction sets for the IT community. Start of the project is expected in the coming months.

In general, open source approach is becoming common not only for software, but also for hardware. Such projects are supported by large companies. Therefore, it can be expected that in the near future more devices will appear on the market based on open hardware standards.

Recent posts from our corporate blog:

- What you need to know about PCI DSS: standard review

- The world before and after. How life has changed with the advent of DNS Flag Day

- Disaster recovery as a service: what you need to know

Posts from our Telegram channel:

Source: https://habr.com/ru/post/444664/

All Articles