Intel acquired eASIC - developer of "structural ASIC"

Last week, Intel announced the acquisition of eASIC, which is developing FPGA-shaped development tools for “structural ASICs”. Structural ASICs are a cross between normal FPGAs and regular ASICs; they allow you to reduce the time to market a product and reduce its cost. EASIC technologies have been used by Intel since 2015 in custom versions of Xeon processors; Now the eASIC team (120 people) will join the Intel Programmable Solutions Group (PSG).

Even those who have long and mutually "introduced friends" FPGA and ASIC, will not refuse to explain what is "structural ASIC". Computer computing power is not limited to a CPU or a GPU, there are other classes of processors, such as FPGA, for example, Altera, acquired by Intel, is developing them. In the FPGA, millions of logic elements can be flexibly programmed to implement the necessary functionality. In fact, most CPUs and GPUs are initially simulated on FPGAs for testing. FPGA is a simple way to model interacting circuits, and their area of application is wide. FPGAs can also contain ready-made hardware units, for example, ARM cores or transceivers for external communications.

Another example is ASIC (Application Specific Integrated Circuit), a chip designed to perform a well-defined set of tasks. ASIC is maximally optimized for its tasks, and the logic of its work cannot be changed. Often, CPU and GPU are classified as ASIC in the sense that their micro-architecture is also fixed, but they are designed to solve various problems and are universal, while ASIC is created for well-defined types of calculations. Features ASIC: they are fast, economical, but relatively expensive and difficult to manufacture.

')

EASIC's “Structural ASIC” can be called a half-way solution. Engineers create a prototype using FPGA, but do not waste time on optimizing its circuit design, but fabricate a chip with a fixed architecture based on it. Because of this, it works faster than the sample with custom blocks, although it loses the advantage of energy efficiency. However, the time for its development is comparable to the FPGA, and not ASIC - it saves up to 6 months. The contribution of eASIC is that one-screen optimization of the layer is used to replace SRAM routing with end-to-end, which significantly reduces production costs. eASIC also provides single-layer fixed libraries for cells, which further reduces consumption, chip size, and time to market. Also, designers can skip standard procedures for creating ASICs, such as synchronization balancing, signal integrity analysis, power loss test, and others. Thus, “structural ASICs” can be described as FPGAs, which can no longer be programmed, possessing the best qualities of both FPGAs and ASICs.

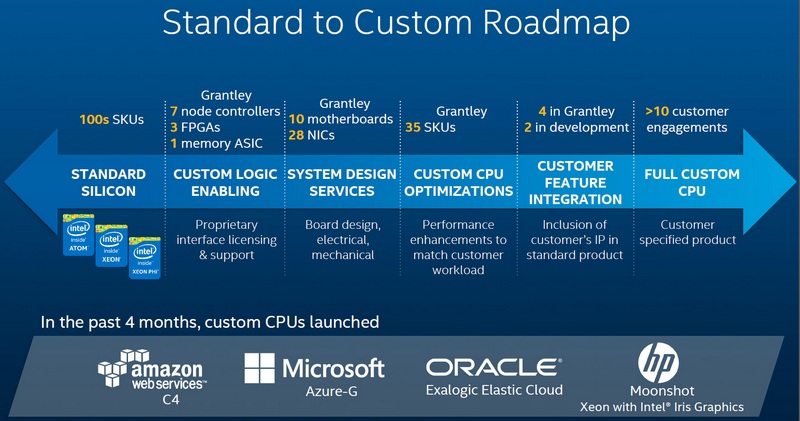

The graph shows the current state of affairs and prospects in the field of custom processors Intel Xeon

EASIC technology needs Intel to integrate programmable logic into Xeon processors to improve performance, power consumption, and price. Along with the standard Xeon, Intel is already releasing custom options for its largest customers. As we see from the scheme, the depth of customization will increase. With the acquisition of eASIC, this process will accelerate and expand. It seems that the approach "CPU as ASIC" can bring us a lot of interesting things.

Source: https://habr.com/ru/post/417511/

All Articles