To systems on a chip through FPGAs: the week of digital microelectronics in Kiev - April 24-29, 2017

On April 24-29, Kiev will host a series of seminars for schoolchildren who do not look like regular classes with embedded processors that use Lego / Arduino / Rasberry Pie as standard. The main focus of the seminars is not to teach how to program processors, but to show principles how processors are designed inside. It's like the difference between “learn to drive a car” and “teach how to design an engine.” At the seminars, students will use the language of the description of the device Verilog and logic synthesis - technologies that are used by developers of digital microcircuits in Apple, Samsung and other electronic companies.

The main official page of the seminar, the same registration .

For exercises, FPGA boards are used - matrices of logic elements with variable function (this is not the usual “processor + memory”). FPGAs have long been used to teach students to design electronics at Stanford and MIT, and more recently in Russian and Ukrainian universities. Using FPGAs for teaching schoolchildren is an experiment, and you have a chance to participate in it. To facilitate entry into Verilog and FPGA, we will first take up exercises with small-scale integrated circuits on bezpeechnyh development boards. Then we will deal with the FPGA and on the last day of the seminars we will compare the FPGA design with the programming of the microprocessor for the Internet of things.

You will finally see what happens between the transistor and the Arduino, in an area where schoolchildren rarely drop in!

')

Program for older students and younger students

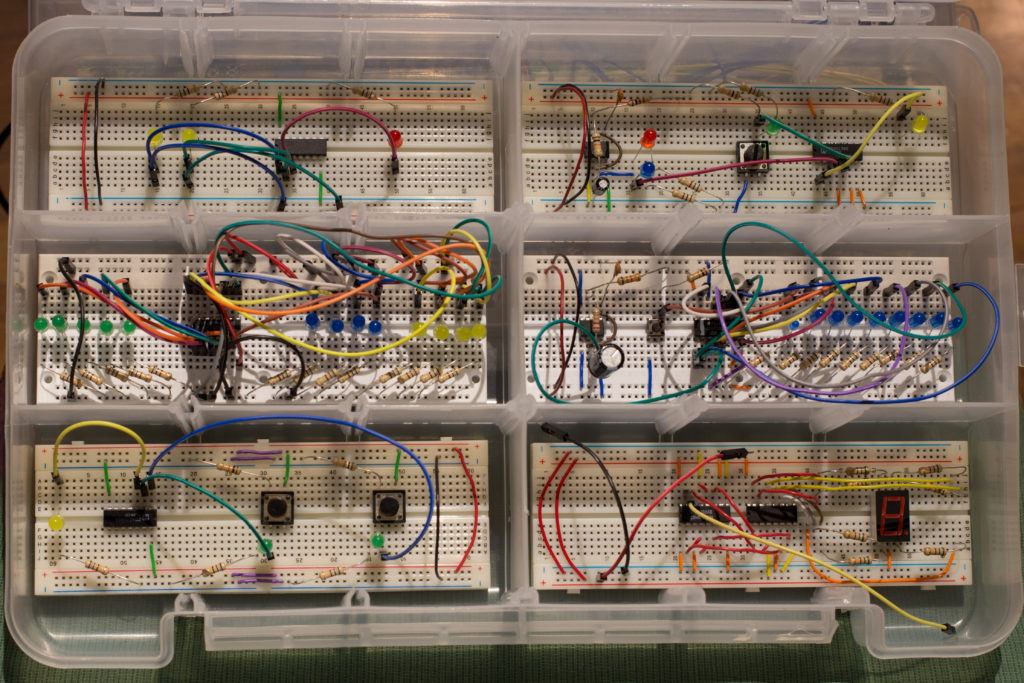

Monday April 24th. Getting the path to the FPGA: combinational logic and binary arithmetic on chips of low degree of integration

Location: Belka Student Space KPI

- 16: 00-17: 00 Alexander Barabanov, KNU. From physics to logic.

- What is current, voltage and resistance.

- How is the breadboard.

- Exercise 1. The first circuit with a battery, LED and a resistor. Why include a resistor in the circuit with LED.

- What are transistors and how logical elements are built from them.

- Exercise 2. Observe the work of the transistor.

- What is current, voltage and resistance.

- 17: 00-18: 00 Yuri Panchul, Imagination Technologies. Boolean algebra of logic, AND-OR-NOT logical elements.

- Exercise 3. Each student is given a personal logic chip series CMOS 4000, with a technical description from the manufacturer, with the task to draw a truth table, demonstrate its work and verbally describe the function. Logic elements AND, OR, XOR, NOR, NAND with different numbers of inputs.

- Exercise 4. We study what the pull-up resistors are and why they are needed. Add to the Exercise 3 buttons and pull-up resistors.

- Exercise 3. Each student is given a personal logic chip series CMOS 4000, with a technical description from the manufacturer, with the task to draw a truth table, demonstrate its work and verbally describe the function. Logic elements AND, OR, XOR, NOR, NAND with different numbers of inputs.

- 18: 00-19: 00 Binary arithmetic, addition and multiplication.

- Exercise 5. Each student is given an adder CMOS 4008. Demonstration of the adder on the breadboard.

- Exercise 5. Each student is given an adder CMOS 4008. Demonstration of the adder on the breadboard.

- 19: 00-21: 00 Additional exercises for those who have mastered exercises 1-5 and do not want to go home.

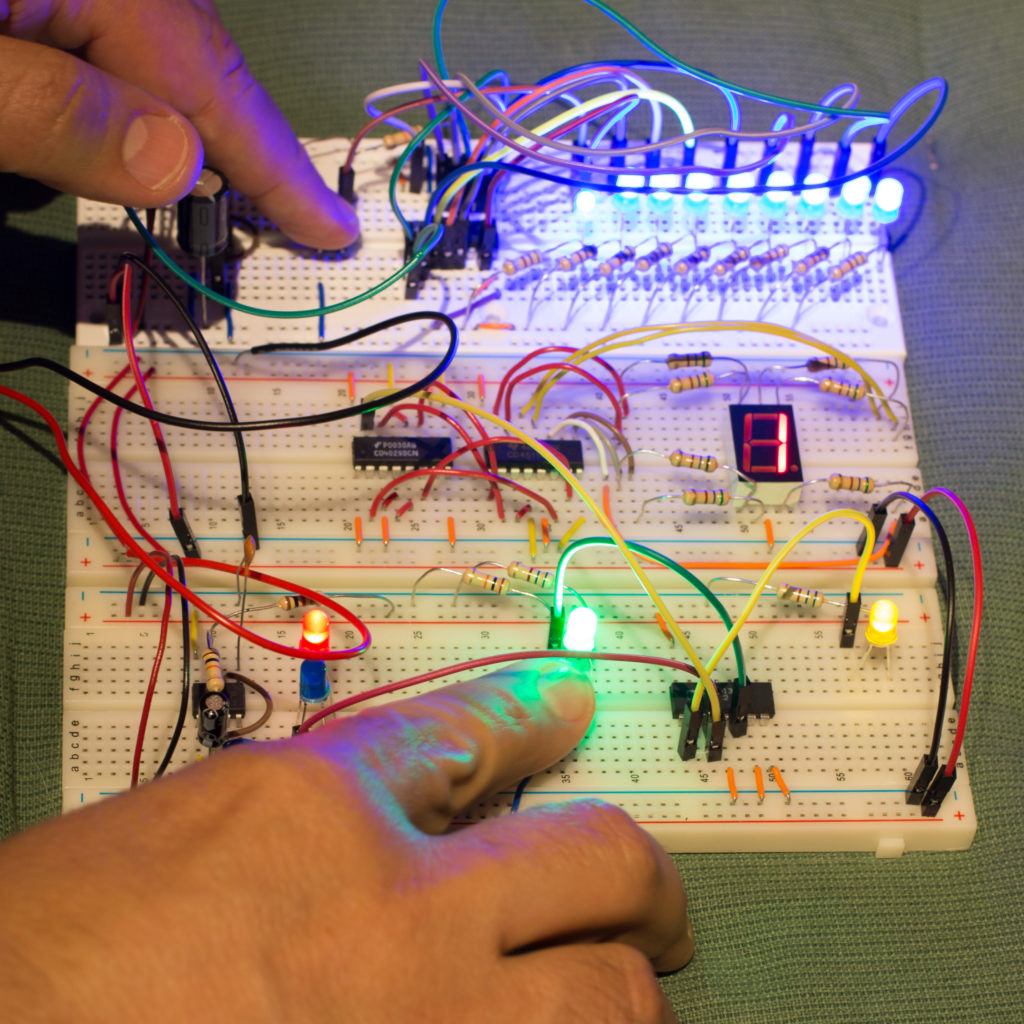

- Exercise 6. Seven-segment indicator and its driver, as an example of combinational circuit. The output of the result of the adder on the seven-segment indicator.

- Exercise 6. Seven-segment indicator and its driver, as an example of combinational circuit. The output of the result of the adder on the seven-segment indicator.

Tuesday April 25th. We add memory: Sequential logic on chips of low degree of integration.

- 16: 00-16: 30 Yuri Panchul. Sequential logic is what makes a computer “smart,” it gives it memory and the ability to repeat operations.

- 16: 30-17: 00 Yuri Panchul and KPI instructors.

- What is a D-trigger.

- Exercise 7. Connect the clock signal generator based on the 555 timer in the D-flip-flop and examine the work of the circuit.

- What is a D-trigger.

- 17: 00-19: 00 More complex elements of sequential logic.

- Exercise 8. The shift register and moving lights.

- Exercise 9. The counter with a conclusion of a condition on the seven-segment indicator.

- Exercise 8. The shift register and moving lights.

- 19: 00-21: 00 Yevgeny Korotky, KPI. Additional exercises for those who have mastered exercises 6-8 and do not want to go home.

- Exercise 10. Investigate the clock signal generator based on the chip 555 timer. We observe how the period of the clock frequency varies depending on the resistances of the resistors and the capacitance of the capacitor.

- Exercise 10. Investigate the clock signal generator based on the chip 555 timer. We observe how the period of the clock frequency varies depending on the resistances of the resistors and the capacitance of the capacitor.

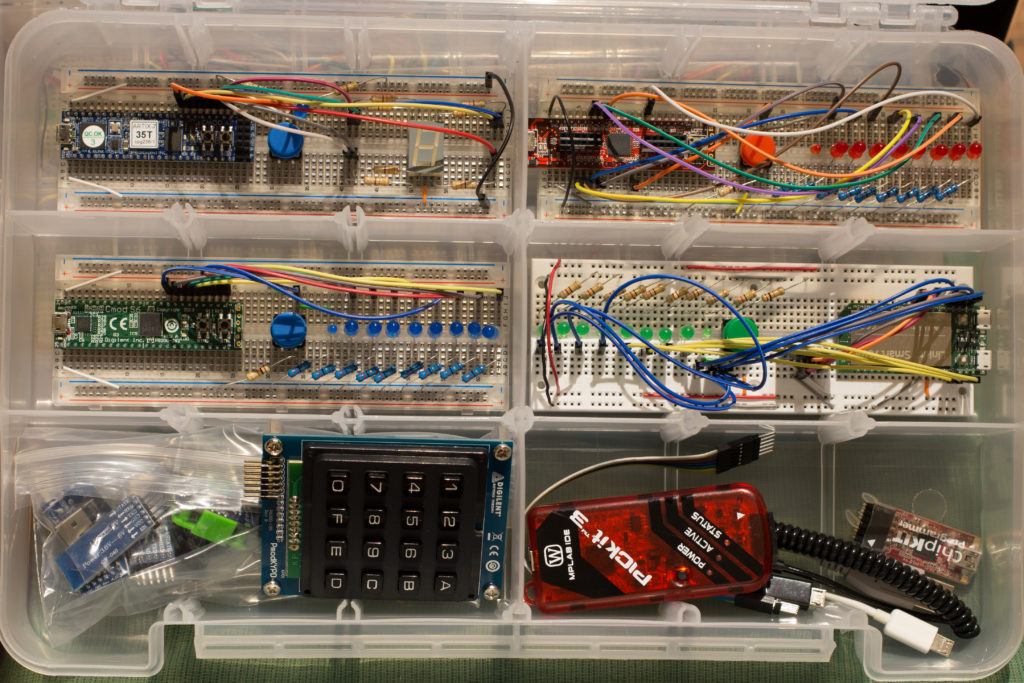

Wednesday April 26th. Combination logic and binary arithmetic on Verilog and FPGA.

Location: Belka Student Space KPI.

- 16: 00-16: 30 Yuri Panchul, as well as instructors from the KPI, KNU. A quick introduction to the Verilog hardware description language and the use of logic synthesis for FPGA / FPGA. We consider only combinational logic.

- 16: 30-17: 00 Instructors from KPI, KNU. Combination logic on Verilog.

- Exercise 11. Repeat exercise 2 (logic elements) on the FPGA using the Digilent CMOD A7 35T: Breadboardable Artix-7 FPGA Module.

- Exercise 12. Deduce the first letters of your first and last name on a seven-segment indicator, switching between them using the button.

- Exercise 13. Repeat Exercise 3 (adder) on the FPGA. The result is displayed on a seven-segment indicator.

- Exercise 11. Repeat exercise 2 (logic elements) on the FPGA using the Digilent CMOD A7 35T: Breadboardable Artix-7 FPGA Module.

- 19: 00-21: 00. Additional exercises for those who have mastered exercises 9-11 and do not want to go home.

- Exercise 14. The hierarchy of modules. Construction of multiplexers with submodules.

- Exercise 15. Simulation Verilog code without FPGA. Create an environment to test the operation of the circuit described in Verilog. We use the simulator Icarus Verilog for modeling and the program GTKWave to view the time diagrams.

- Exercise 14. The hierarchy of modules. Construction of multiplexers with submodules.

An example of code in the Verilog hardware description language, which is translated (synthesized) into the schema:

module counter ( input clock, input reset_n, output reg [31:0] count ); always @(posedge clock or negedge reset_n) begin if (! reset_n) count <= 32'b0; else count <= count + 32'b1; end endmodule //---------------------------------------------------------------------------- module seven_segment_display_driver ( input [3:0] number, output reg [6:0] abcdefg ); // abcdefg dp // 7 6 4 2 1 9 10 5 7- // 7 6 5 4 3 2 1 pio // --a-- // | | // fb // | | // --g-- // | | // ec // | | // --d-- always @* case (number) 4'h0: abcdefg = 7'b1111110; 4'h1: abcdefg = 7'b0110000; 4'h2: abcdefg = 7'b1101101; 4'h3: abcdefg = 7'b1111001; 4'h4: abcdefg = 7'b0110011; 4'h5: abcdefg = 7'b1011011; 4'h6: abcdefg = 7'b1011111; 4'h7: abcdefg = 7'b1110000; 4'h8: abcdefg = 7'b1111111; 4'h9: abcdefg = 7'b1111011; 4'ha: abcdefg = 7'b1110111; 4'hb: abcdefg = 7'b0011111; 4'hc: abcdefg = 7'b1001110; 4'hd: abcdefg = 7'b0111101; 4'he: abcdefg = 7'b1001111; 4'hf: abcdefg = 7'b1000111; endcase endmodule //---------------------------------------------------------------------------- module top ( input CLK, // 12 MHz inout [48:1] pio // GPIO, General-Purpose Input/Output ); wire reset_n = ! pio [8]; wire [31:0] count; counter counter_i ( .clock ( CLK ), .reset_n ( reset_n ), .count ( count ) ); seven_segment_display_driver display_driver_i ( .number ( count [26:23] ), .abcdefg ( pio [ 7: 1] ) ); endmodule Thursday April 27th. Sequential logic and finite automata on Verilog and FPGA.

Location: Belka Student Space KPI.

- 16: 00-17: 00. Yuri Panchul. Verilog sequence logic, state machines, concept of RTL methodology (register transfer level), signal propagation delays and restrictions on the procedure for synthesizing digital circuits, determining the maximum possible clock frequency of the digital circuit.

- 17: 00-19: 00. Instructors from KPI, KNU. Verilog sequential logic.

- Exercise 16. The counter with a conclusion of a condition on the seven-segment indicator. Implementation of Exercise 9 on the FPGA.

- Exercise 17. Register shift and moving lights. Implementation of Exercises 8 on the FPGA.

- Exercise 18. Generation of sound tones of different frequencies and their overlay.

- Exercise 16. The counter with a conclusion of a condition on the seven-segment indicator. Implementation of Exercise 9 on the FPGA.

- 19: 00-21: 00. Additional exercises for those who have mastered exercises 17-18 and want to work further.

- Exercise 19. "The snail smiles": an example of a finite state machine.

- Exercise 20. Build an arithmetic conveyor. We use the simulator Icarus Verilog to improve the operation of sequential schemes.

- Exercise 19. "The snail smiles": an example of a finite state machine.

Friday April 28th. Comparison of circuit design with embedded microprocessor programming.

Location: Belka Student Space KPI.

- 16: 00-16: 30. Yuri Panchul. How programming differs from circuitry. Von Neumann's machine is a special case of an electronic circuit. Programs like instruction chains for von Neumann's machine. Overview of the microprocessor core used in MediaTek MT7688 and Microchip PIC32MZ.

- 16: 30-19: 00 Yevgeny Korotky. Example: LinkIt Smart 7688 Internet platform based on MediaTek MT7688.

- Exercise 21. flashes the LED using a Python program.

- Exercise 22. reads data from the light sensor Digilent PMOD ALS using the SPI protocol.

- Exercise 23. Introduction to the concept of interruptions.

- Exercise 21. flashes the LED using a Python program.

- 19: 00-21: 00. Additional exercises for those who have mastered the exercises on LinkIt Smart 7688 and want to continue working. Example: Microchip PIC32 microcontroller.

- Exercise 24. LED flashes using C program.

- Exercise 25. reads data from the light sensor Digilent PMOD ALS using the SPI protocol.

- Exercise 26. Unload the main program using interrupts. The timer interrupt starts the SPI transaction, the SPI interrupt signals that the packet has been received.

- Exercise 24. LED flashes using C program.

Saturday April 29th. Hackathon

Place: National University "Kyiv-Mohyla Academy"

- Projects with microcircuits of low degree of integration: "Soil moisture detector", "Police siren"

- Projects with FPGAs: interfaces for sensors, finite state machines of the type “code lock”

- Projects with microcontrollers and embedded microprocessors for the Internet of Things: connecting with sensors and actuators

Program for younger students

April intensive "Introduction to Electronics"

Monday April 24th. Familiarity with the basics: Ohm's law, passive electronic elements (resistors and capacitors)

Venue: Office of Radiomag Ukraine LLC, Chokolovsky Boulevard, 42-A

Time: 17: 00-19: 00

Lecturer: Sergey Chenash

- What is current, voltage and resistance, Ohm's law

- How is the breadboard

- How to work with a multimeter

- Resistors and their application

- Capacitor as an electric charge accumulator and its application

Tuesday April 25th. Active electronic components: the structure and principles of operation of diodes and transistors

Venue: Office of Radiomag Ukraine LLC, Chokolovsky Boulevard, 42-A

Time: 17: 00-19: 00

Lecturer: Sergey Chenash

- Characteristics of semiconductors, the structure of the pn junction

- How do diodes and their classification

- Principles of operation of transistors and their application

Thursday April 27th. Studies of the elements of optoelectronics: LEDs, photoresistors, phototransistors, optocouplers

Venue: Office of Radiomag Ukraine LLC, Chokolovsky Boulevard, 42-A

Time: 17: 00-19: 00

Lecturer: Sergey Chenash

- Elements of optoelectronics, principles of operation and application

Friday April 28th. Introducing the NE555 Chip

Venue: Office of Radiomag Ukraine LLC, Chokolovsky Boulevard, 42-A

Time: 17: 00-19: 00

Lecturer: Sergey Chenash

- What are chips and their classifications

- Types of signals in electronics

- Introducing the NE555 chip, creating a generator

- Work with the oscilloscope

Saturday April 29th. Bonus rations

Venue: Office of Radiomag Ukraine LLC, Chokolovsky Boulevard, 42-A

Time: 11: 00-12: 30

See you at the seminars!

- Lampa Electronics Open Lab and Belka Student Space, National Technical University of Ukraine “Igor Sikorsky Kyiv Polytechnic Institute”

- Kyiv National Taras Shevchenko University

- National University "Kyiv-Mohyla Academy"

- Small Academy of Sciences of Ukraine

- LLC Radiomag of Ukraine

- Imagination Technologies

The main official page of the seminar, the same registration .

Source: https://habr.com/ru/post/403267/

All Articles