Porting MIPSfpga to Terasic DE0-CV with Altera Cyclone V FPGA

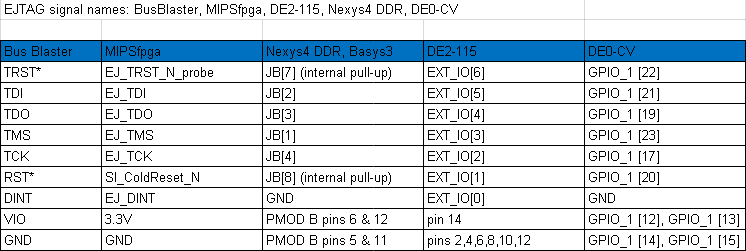

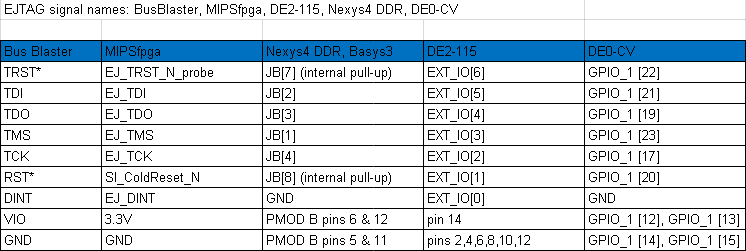

The other day, together with Alex and Vladimir (on the photo), we had a MIPSfpga (package for an introduction to designing systems on a chip) onto a Terasic DE0-CV board with Altera Cyclone V FPGA. This fee is a pretty good solution for the educational Russian market, since it is cheap ($ 150) and simply bought on the website of the Taiwanese company Terasic, which delivers fees to Russia without unnecessary bureaucracy. We will try to use it at seminars at Moscow State University, MEPI, MIET and ITMO (see the end of the post).

The porting process included creating a project in Altera Quartus II with the necessary parameters, cutting the size of the memory used inside the FPGA (in the future you just need to use external memory - it is on the board), and selecting the right pins to connect to the BusBlaster debug adapter card. BusBlaster is used not for debugging a hardware, but for loading into the memory inside the system and debugging software running on the MIPS microAptiv UP processor core in the MIPSfpga system. (MIPS microAptiv UP is the same kernel that stands inside the Microchip PIC32MZ microcontroller, but with open source on Verilog)

To do this at home, you first need to cooperate with any university, since Imagination Technologies licenses MIPSfpga for free only to universities for educational and research purposes. Application for MIPSfpga can be done on the website of educational programs Imagination Technologies:

')

community.imgtec.com/downloads/mipsfpga-getting-started-material-version-1-1

Next you need to get a BusBlaster debug adapter from Imagination Technologies or buy it at www.seeedstudio.com/depot/Bus-Blaster-V3c-for-MIPS-Kit-p-2258.html

Finally, you need to have an account on GitHub and join the github.com/MIPSfpga organization, after which you can download the code from the github.com/MIPSfpga/boards/tree/master/de0_cv directory

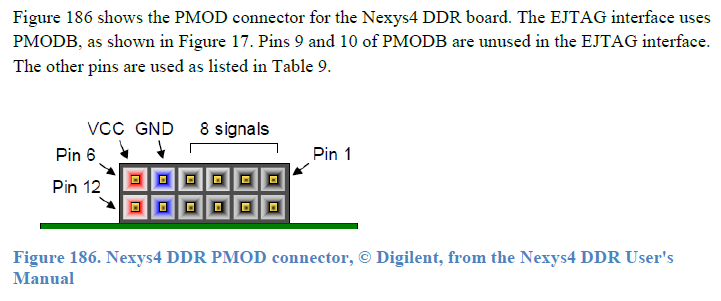

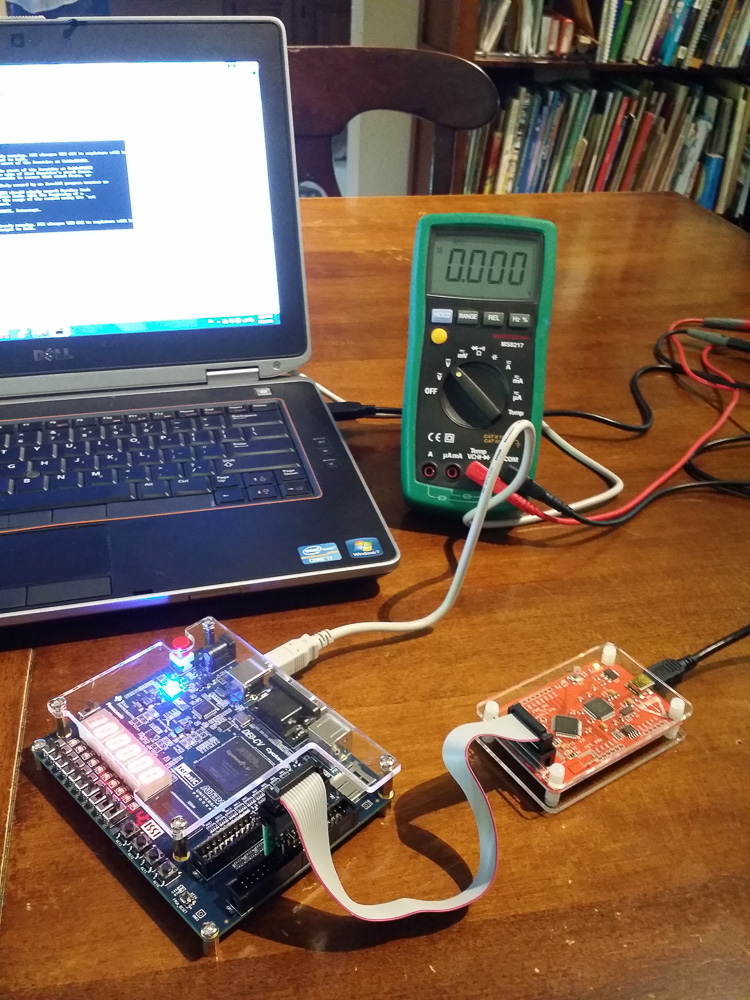

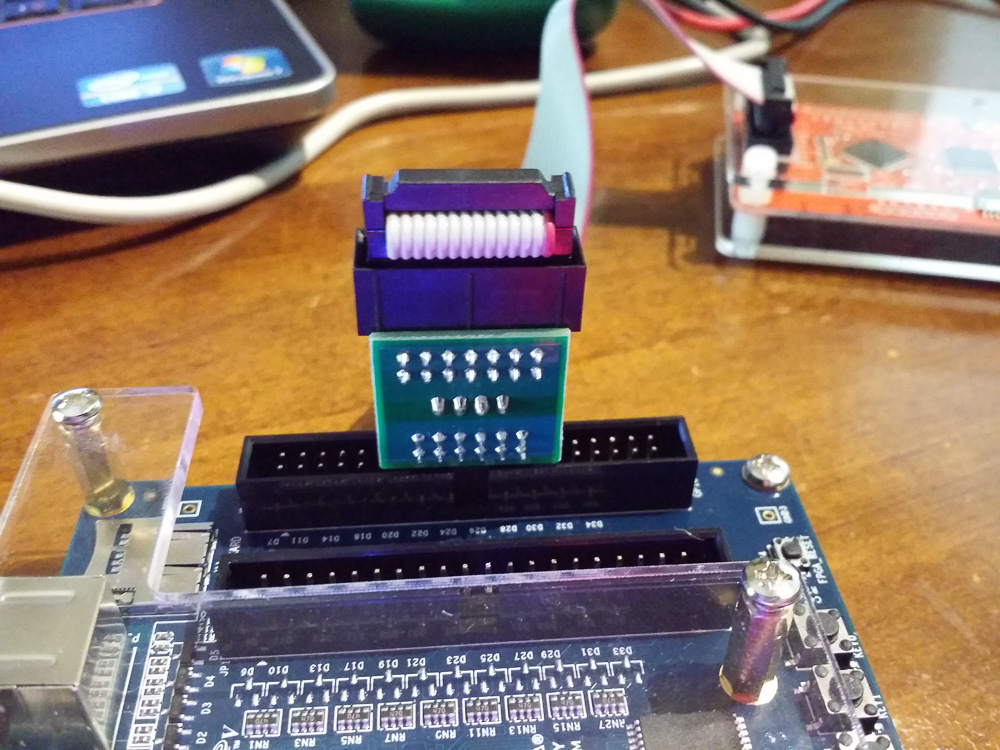

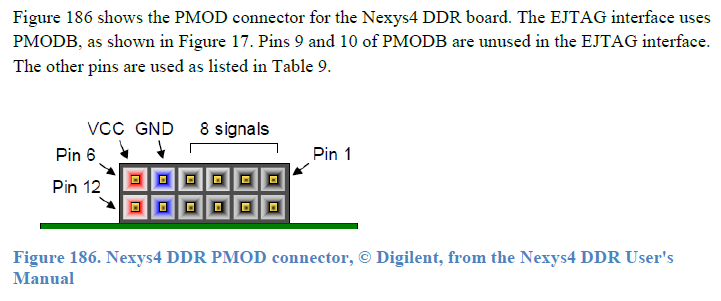

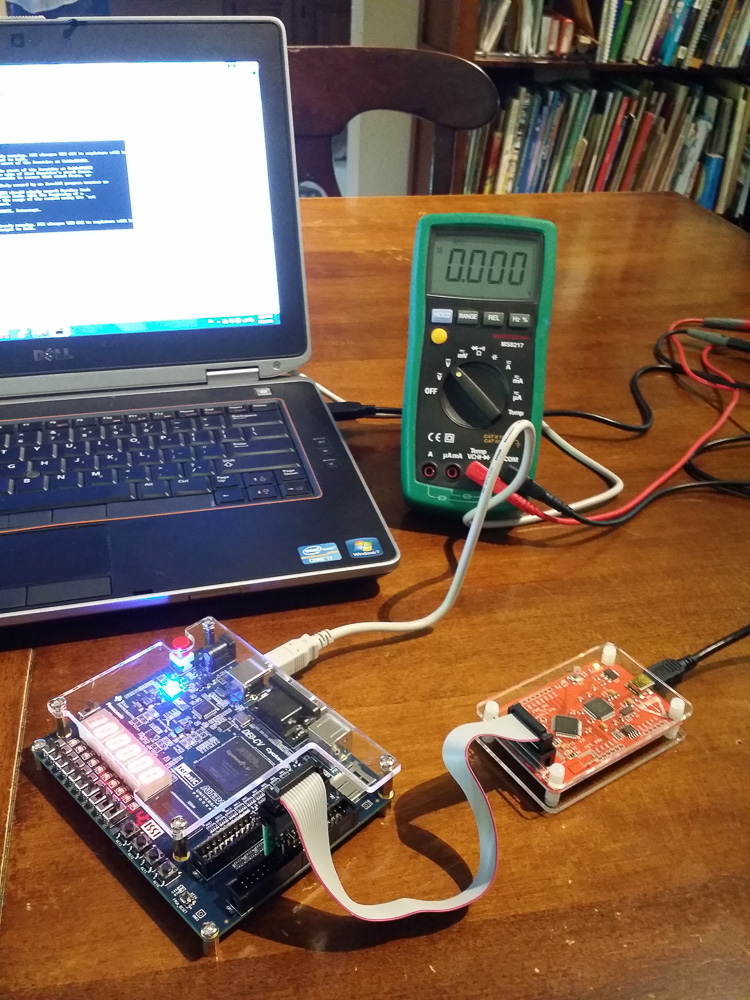

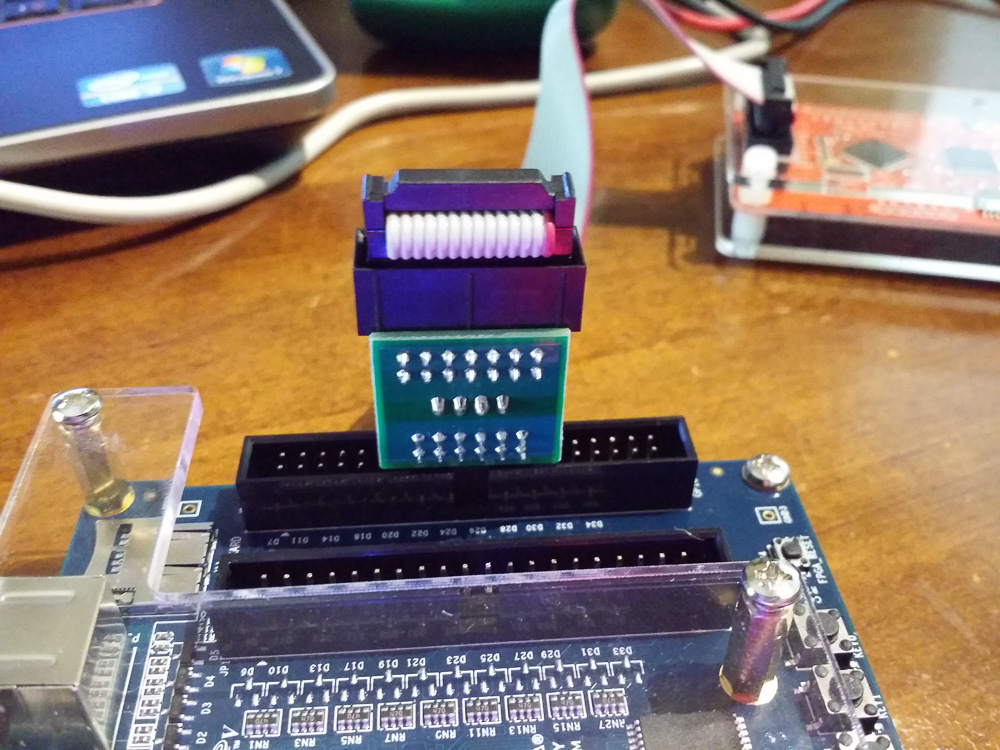

Explanatory pictures about connecting the GPIO 1 pins of the Terasic DE0-CV board and adapter for Bus Blaster. The adapter was originally designed to connect to the Basys3, Nexys4 and Nexys4 DDR boards from digilentinc.com

The adapter had to be placed exactly in the middle to avoid unwanted power and ground connections.

The output of the adapter which was originally intended for connection to the boards from Digilent:

Connection label:

Compound:

Recommended BusBlaster sample connection with Terasic DE0-CV FPGA card

Recommended BusBlaster sample connection with Terasic DE0-CV FPGA card

Recommended BusBlaster sample connection with Terasic DE0-CV FPGA card

Recommended BusBlaster sample connection with Terasic DE0-CV FPGA card

Recommended BusBlaster sample connection with Terasic DE0-CV FPGA card

Recommended BusBlaster sample connection with Terasic DE0-CV FPGA card

Now you can load / configure the MIPSfpga harver into the Altera Terasic DE0-CV, and download the software for the MIPS microAptiv UP kernel inside the system into this system.

A description of what can be done with such a system is in a post about seminars on MIPSfpga, which will be held at Moscow State University, MEPI, MIET, ITMO and Microchip Masters Russia this fall - see habrahabr.ru/post/265045 :

The porting process included creating a project in Altera Quartus II with the necessary parameters, cutting the size of the memory used inside the FPGA (in the future you just need to use external memory - it is on the board), and selecting the right pins to connect to the BusBlaster debug adapter card. BusBlaster is used not for debugging a hardware, but for loading into the memory inside the system and debugging software running on the MIPS microAptiv UP processor core in the MIPSfpga system. (MIPS microAptiv UP is the same kernel that stands inside the Microchip PIC32MZ microcontroller, but with open source on Verilog)

To do this at home, you first need to cooperate with any university, since Imagination Technologies licenses MIPSfpga for free only to universities for educational and research purposes. Application for MIPSfpga can be done on the website of educational programs Imagination Technologies:

')

community.imgtec.com/downloads/mipsfpga-getting-started-material-version-1-1

Next you need to get a BusBlaster debug adapter from Imagination Technologies or buy it at www.seeedstudio.com/depot/Bus-Blaster-V3c-for-MIPS-Kit-p-2258.html

Finally, you need to have an account on GitHub and join the github.com/MIPSfpga organization, after which you can download the code from the github.com/MIPSfpga/boards/tree/master/de0_cv directory

Explanatory pictures about connecting the GPIO 1 pins of the Terasic DE0-CV board and adapter for Bus Blaster. The adapter was originally designed to connect to the Basys3, Nexys4 and Nexys4 DDR boards from digilentinc.com

The adapter had to be placed exactly in the middle to avoid unwanted power and ground connections.

The output of the adapter which was originally intended for connection to the boards from Digilent:

Connection label:

Compound:

Recommended BusBlaster sample connection with Terasic DE0-CV FPGA card

Recommended BusBlaster sample connection with Terasic DE0-CV FPGA card Recommended BusBlaster sample connection with Terasic DE0-CV FPGA card

Recommended BusBlaster sample connection with Terasic DE0-CV FPGA card Recommended BusBlaster sample connection with Terasic DE0-CV FPGA card

Recommended BusBlaster sample connection with Terasic DE0-CV FPGA cardNow you can load / configure the MIPSfpga harver into the Altera Terasic DE0-CV, and download the software for the MIPS microAptiv UP kernel inside the system into this system.

A description of what can be done with such a system is in a post about seminars on MIPSfpga, which will be held at Moscow State University, MEPI, MIET, ITMO and Microchip Masters Russia this fall - see habrahabr.ru/post/265045 :

- Students can build their own prototypes of systems on a chip, connecting the microprocessor core, memory and their input / output devices

- Internal registers can be connected to output ports and output information about the current state of the processor pipeline, caches and memory management devices. After that, the processor can be started at a low clock frequency and observe its operation “in slow motion”.

- Students can experiment with their own variants of caches, design multi-core systems with specialized coprocessors, experiment with the division of the task into hardware and software.

Source: https://habr.com/ru/post/366219/

All Articles