Severe Siberian and Kazakh microelectronics 2017: Verilog, ASIC and FPGA in Tomsk, Novosibirsk and Astana

The year 2017 was a year of major changes in the nascent ecosystem of Russian microelectronics. These changes were noticed even by the society that was previously indifferent to the Russian gland. The Russian ELISE chip for smart cameras from ELVIS-NeoTech was released on a convenient board for developers . This fee was shown on Channel One of Russian television. With the Russian processor Baikal-T, any programmer can now work through access to the servers of the remote laboratory that the Baikal team created with Moscow State University. The Russian processors from NIISI began to be used for telecommunication equipment .

To move from individual successes to a developed ecosystem, it is necessary to twist the formation. In September , a meeting was held in Tomsk , where teachers and engineers from Moscow, Siberia, the Volga region, California and other places shared their experience in teaching microelectronics. At the same time, a training seminar on SystemVerilog, VHDL, FPGA, CPU IP was held there, which was attended not only by Russians, but also by students from China and Vietnam, among whom information was quickly spread that they were teaching something useful for their career. Under the cut - a report on this and related events. Actors: Tomsk and Novosibirsk universities, Moscow State University, MIPT and MIET, Novosibirsk Lyceums, Russian company MCST, American MIPS, AMD and National Instruments, British Imagination and Kazakh Nazarbayev University.

Before you see photos of pretty diners at a seminar in a Siberian restaurant, let's say a few words about the position of the technologies discussed in the universe, for those who came to this post from another part of the technological universe.

')

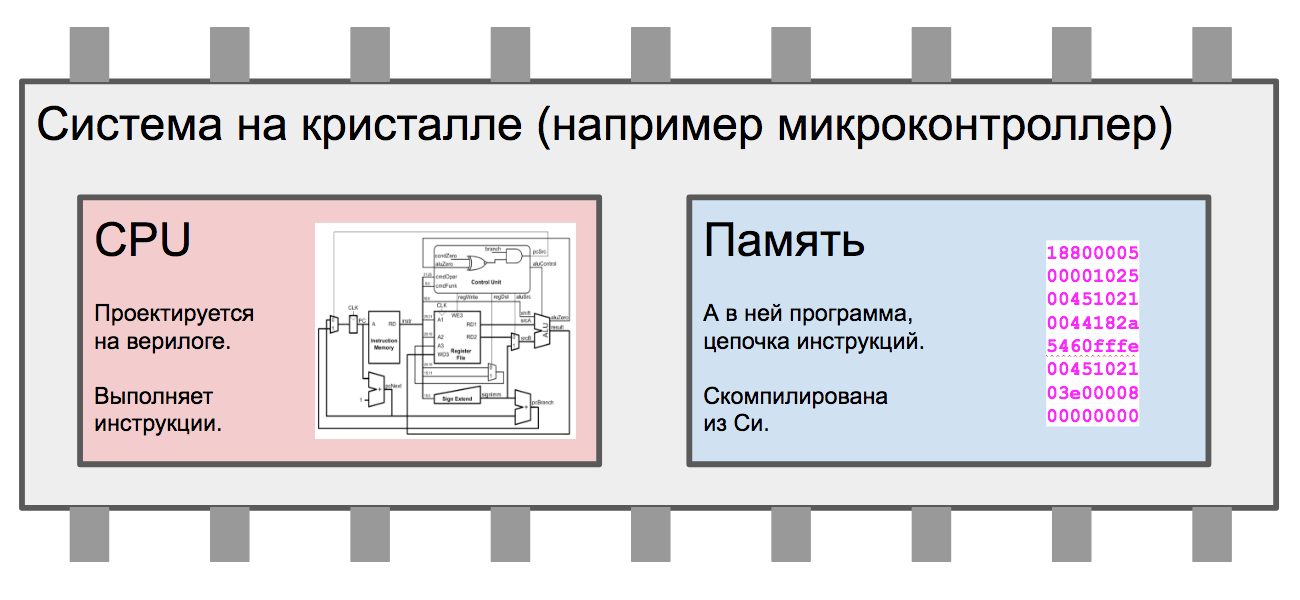

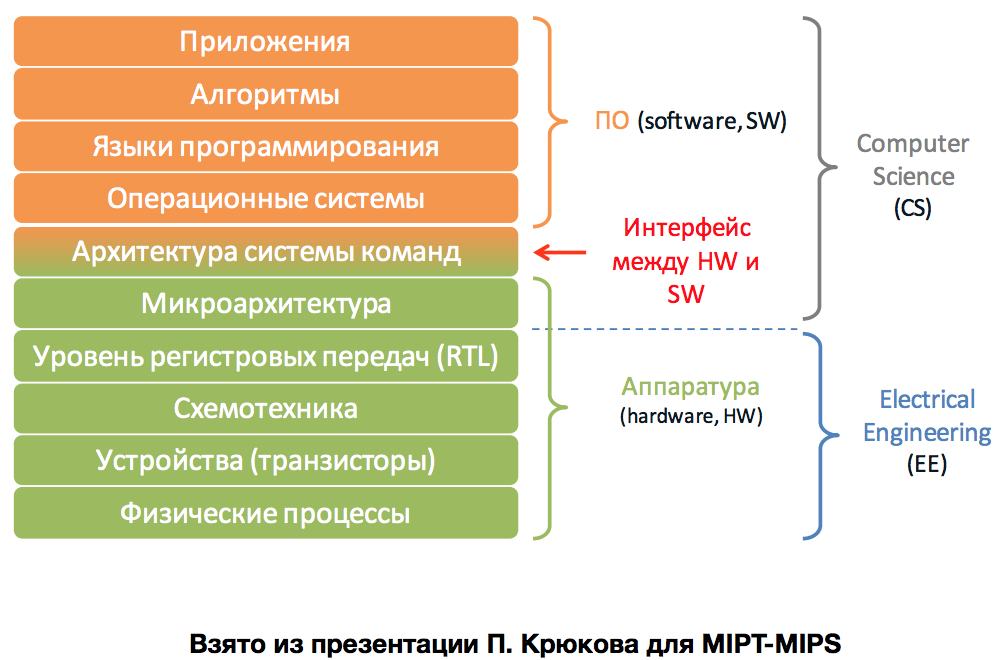

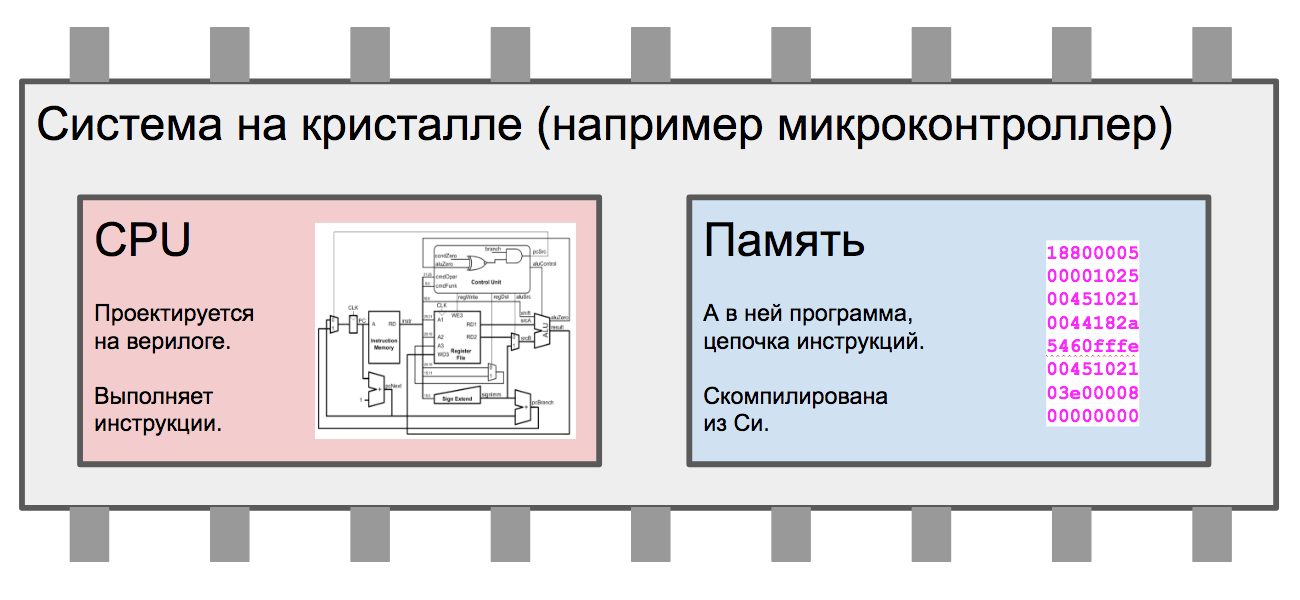

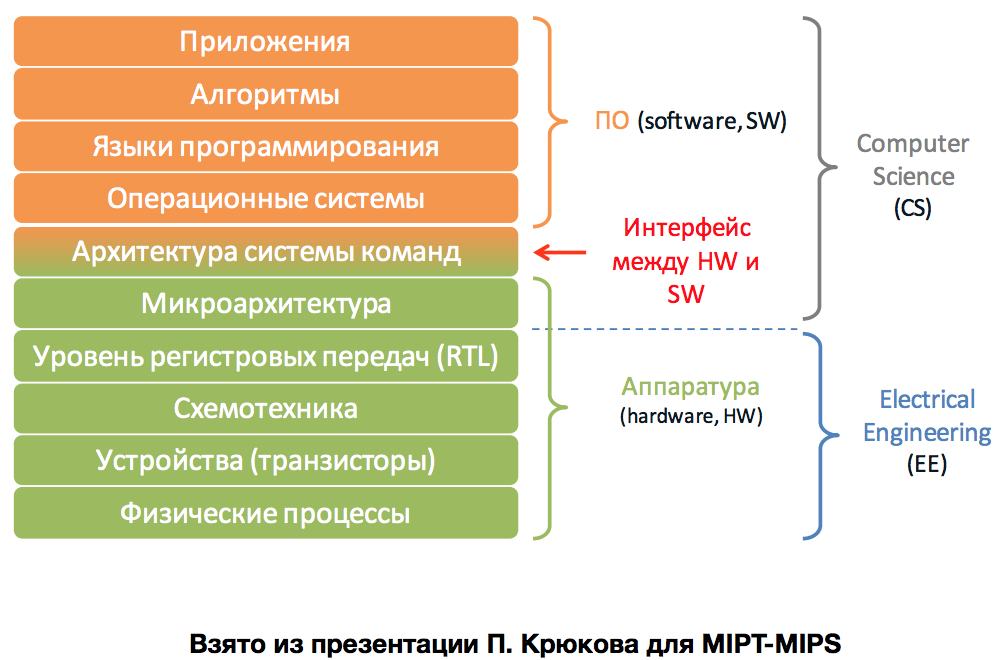

In any serious modern electronic device there is a hardware-software dualism:

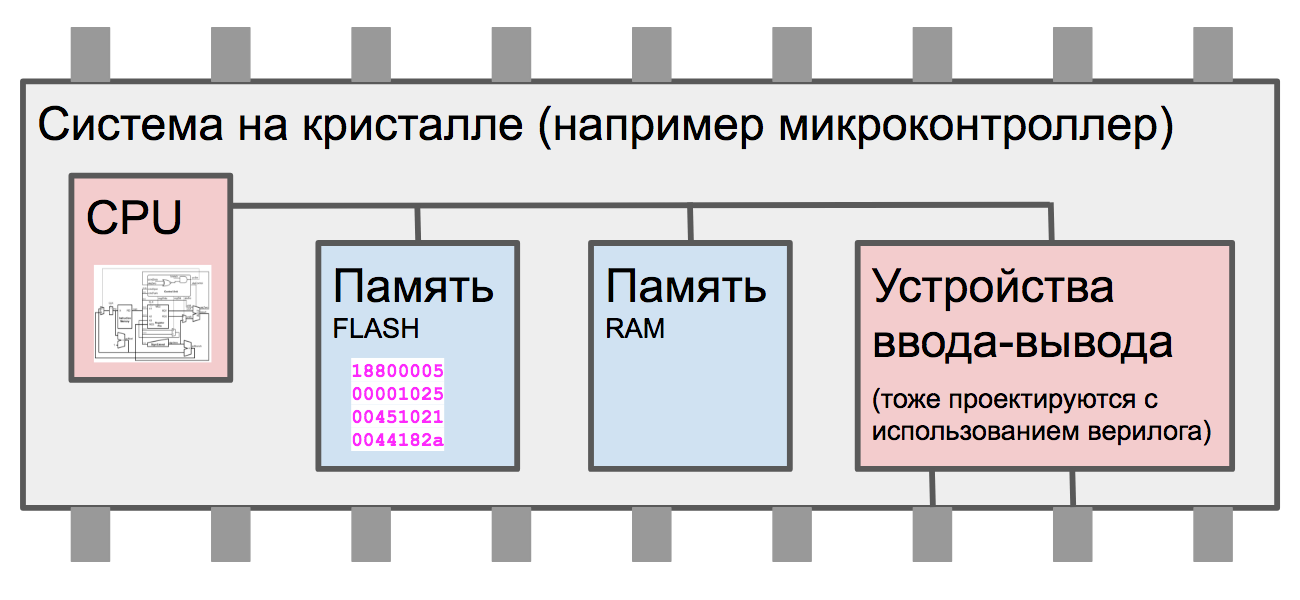

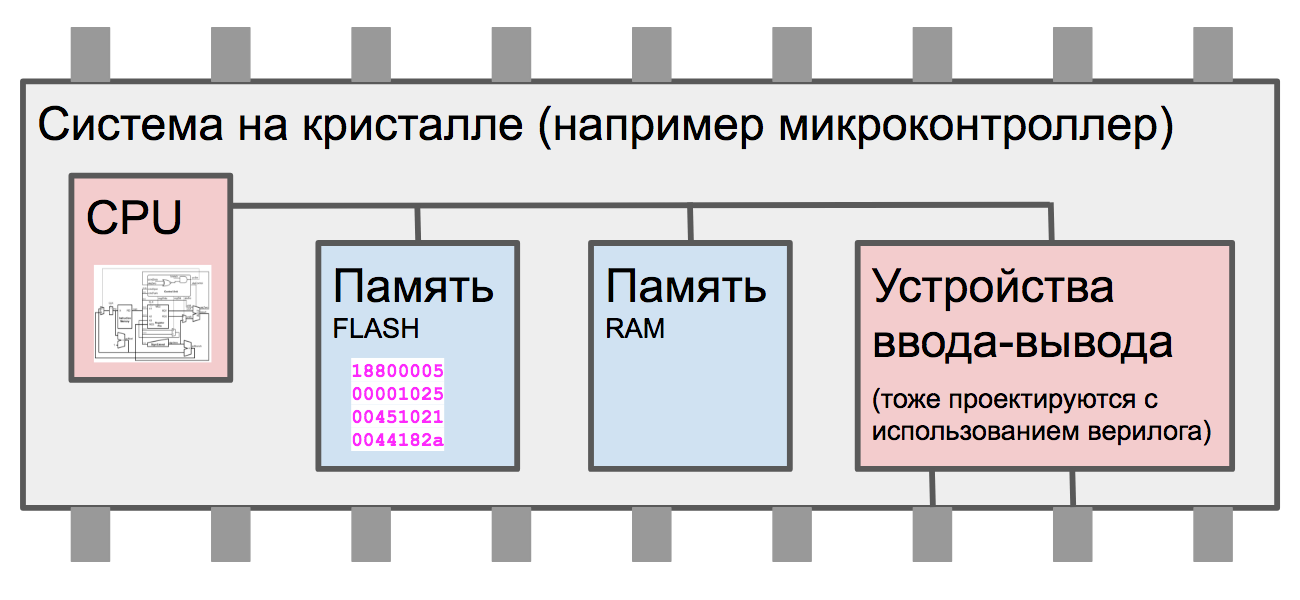

Not only the processor is designed in hardware description languages, but also peripheral device controllers and their connections in the system:

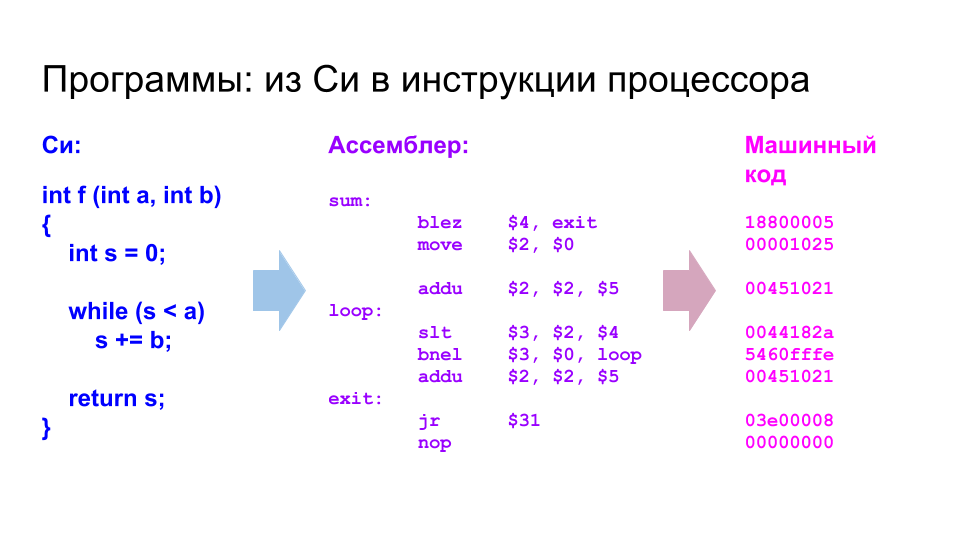

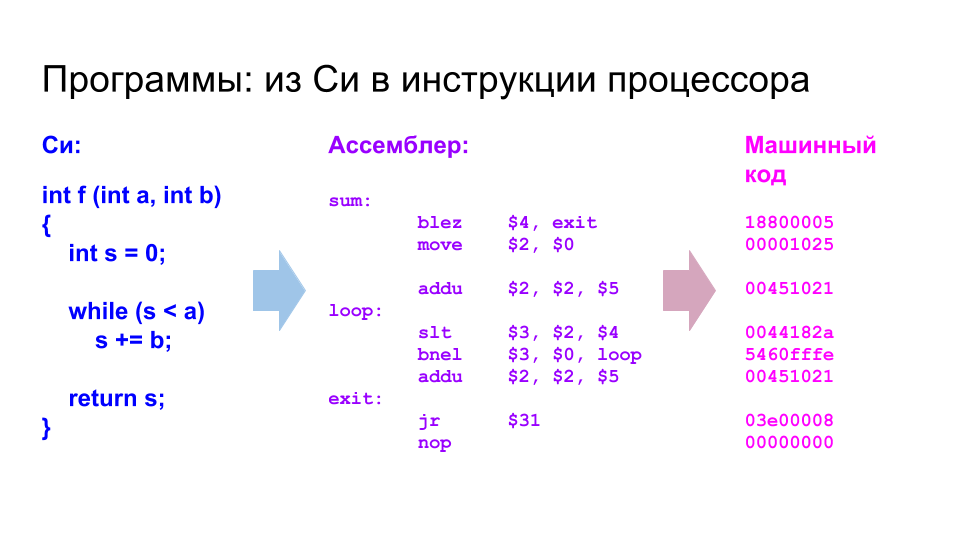

You all know how programs are compiled - in the instructions that the processor executes:

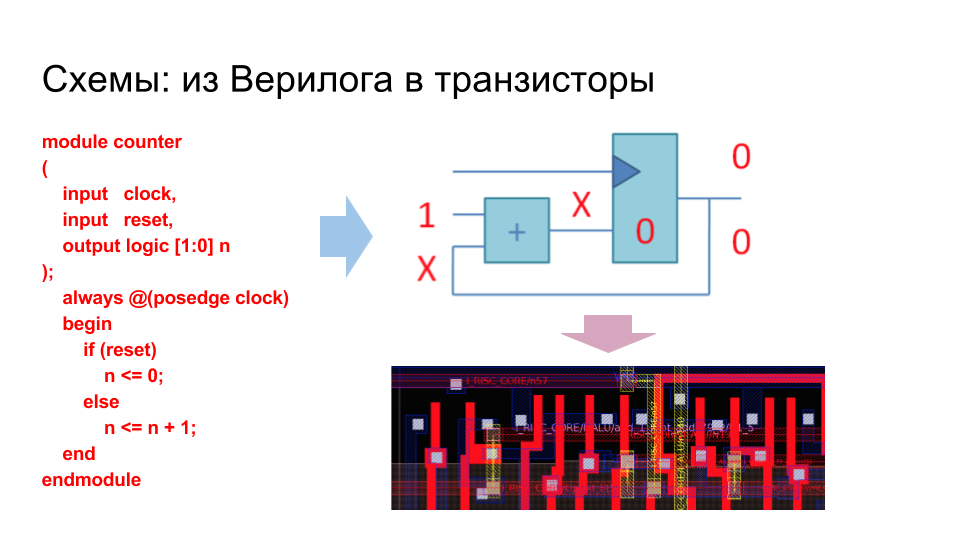

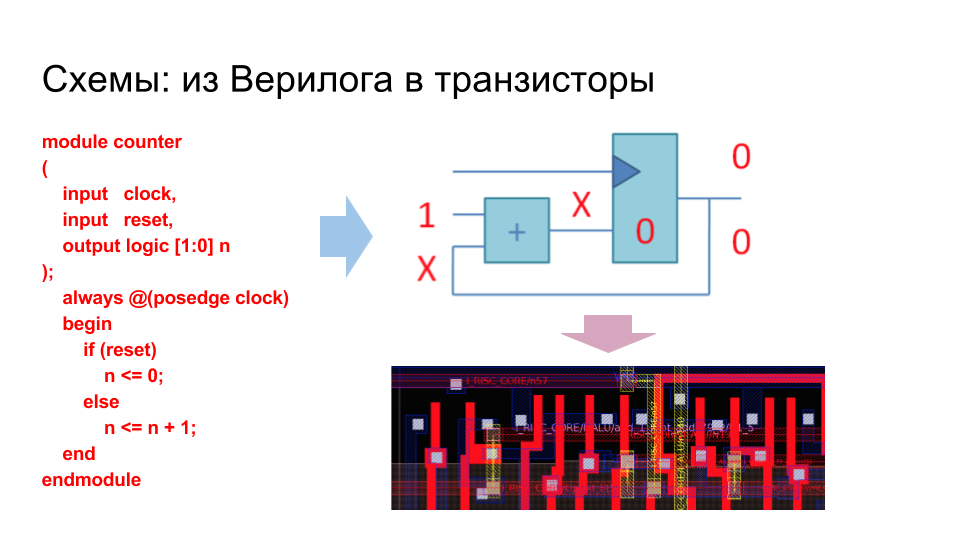

But the schema descriptions in the Verilog hardware description language are compiled (synthesized) not into instructions, but into schemas. As a special case - in the processor circuit which takes from memory and executes instructions. In the end, the description on the chain turns into microcircuit tracks and transistors. This is not a “microcode”, honestly (“microcode” is about something else). Therefore, it is not quite correct to say “programming on the chain”, it’s like saying “HTML programming” Programs are chains of instructions for the von Neumann machine, not a scheme (although you can use the verification to program how to fly an airplane on the highway). It is correct to say “design the circuits on the chain at the register transfer level” or simply “write code on the chain”.

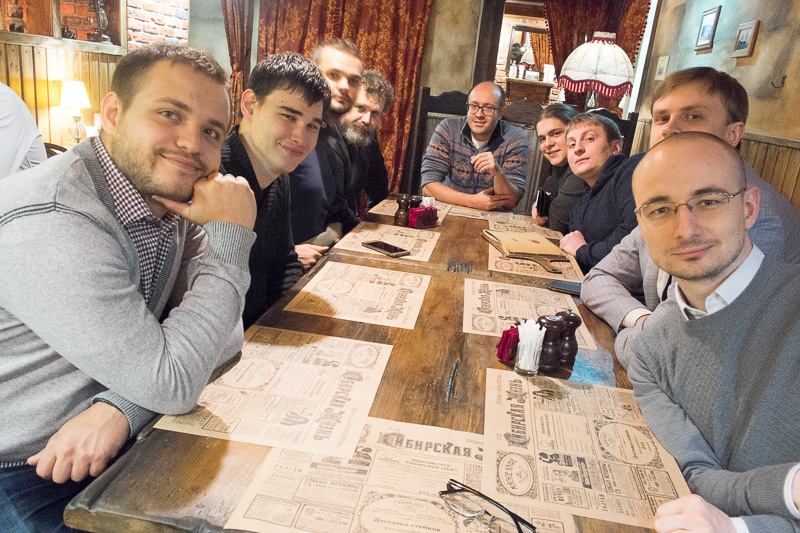

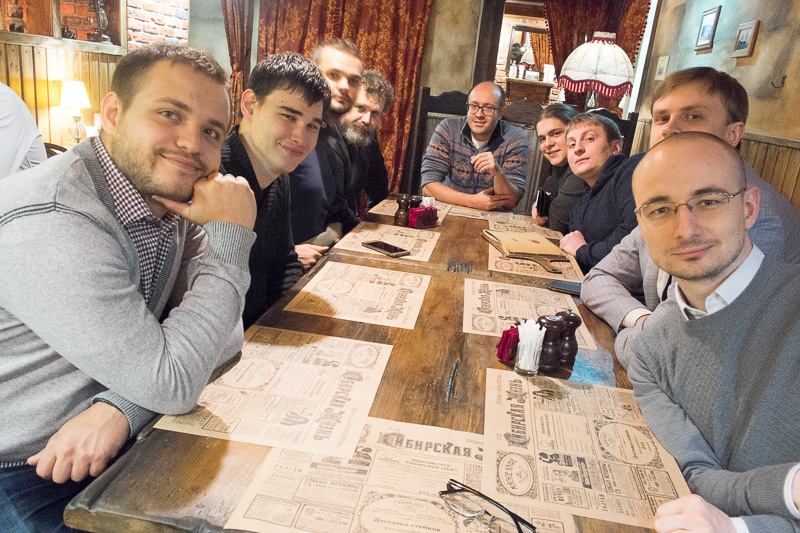

We now turn to the event in Tomsk. The idea to make a workshop on the development of digital microchips was born in December 2016 right here at this table in the beer garden in the middle of Silicon Valley, California. Physicist / chemist Anatoly Korkin (second from left) initially planned to make a purely conference in Tomsk for physicists and chemists, including those who create production technologies in the semiconductor industry. Anatoly himself once worked at Motorola in Arizona, and some of his colleagues, whom he invited to the conference, developed technologies for the production of memory chips.

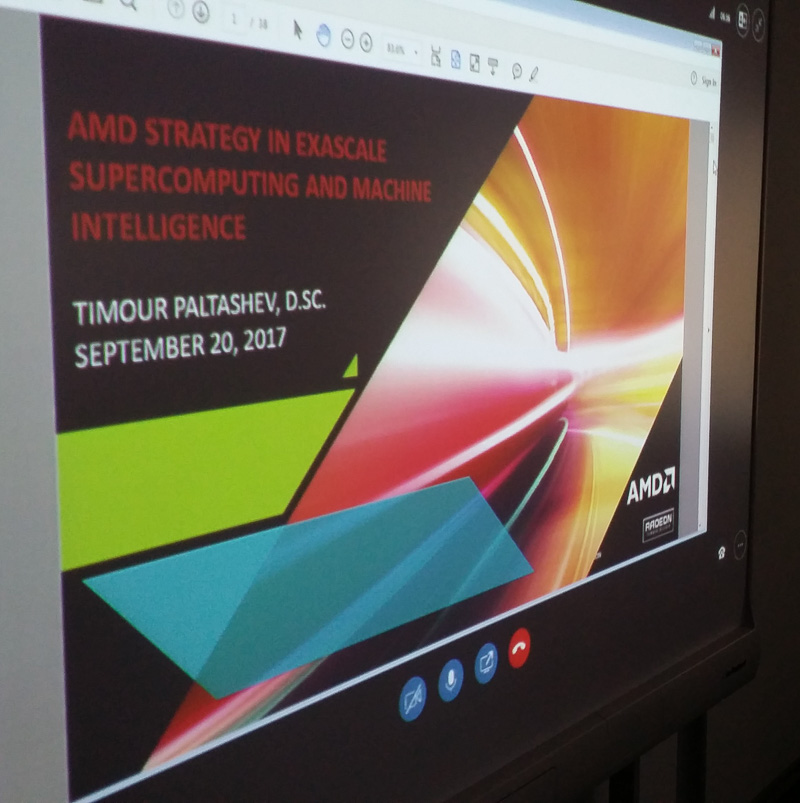

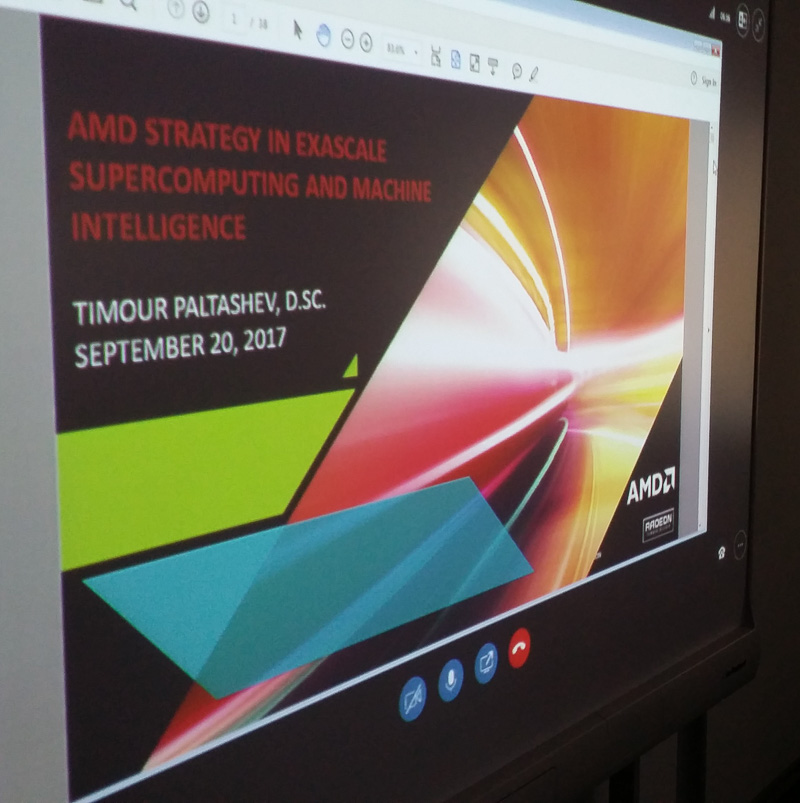

The problem is that physicists without programmers themselves will not build a computer system. Worse, physicists will not build this system with programmers either. For a computer or gadget to work, between physics and programming there must be a bridge from a chain of technologies that includes microarchitecture, logical hardware design at the register transfer level (RTL), design automation using logical and physical synthesis (logic synthesis, floorplanning , place & route). Therefore, Anatoly met with a professor from the University of California, Charles Danchek, who last year gave very popular lectures at MISiS with an overview of the chip design chain (first left), as well as AMD manager Timur Paltashev (first right), and your humble servant. And it was decided to do a seminar in Siberia (although Timur and Charles could only participate remotely).

Tomsk turned out to be a visually interesting city, with a cozy center and a large number of buildings, very different from the architecture of Silicon Valley:

The city has a high percentage of residents - students, as there are several universities in Tomsk, including Tomsk State University (where we held a seminar), Tomsk Polytechnic University (from which students came to us) and Tomsk University of Control Systems and Radio Electronics (TUSUR ), from which listeners came to us:

On the first day, students were taught by Nikita Polyakov from the MCST and MIPT (with a beard on the left — he taught Verilog) and Ilya Kudryavtsev from Samara University (with a beard on the right — he taught VHDL). VHDL is also a hardware description language, it is loved by the military of all countries and some groups of some companies (Texas Instruments, IBM, Imagination Technologies). PoverVR inside Apple iPhone is written in VHDL.

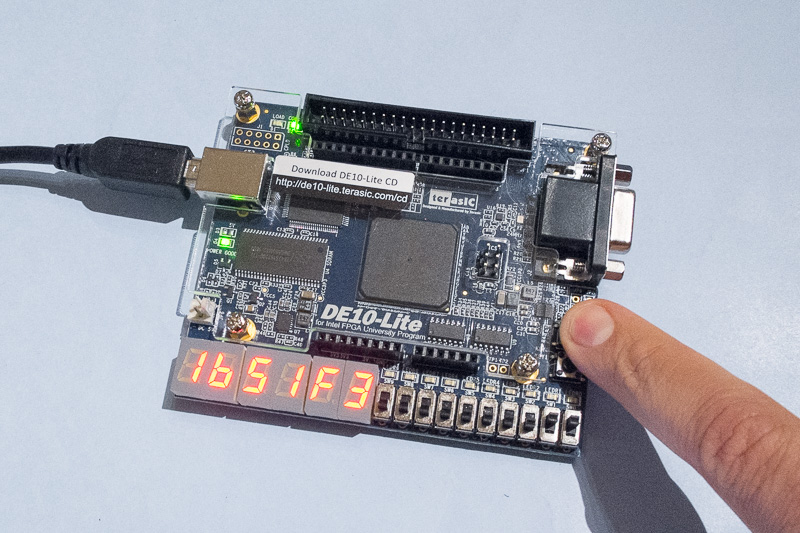

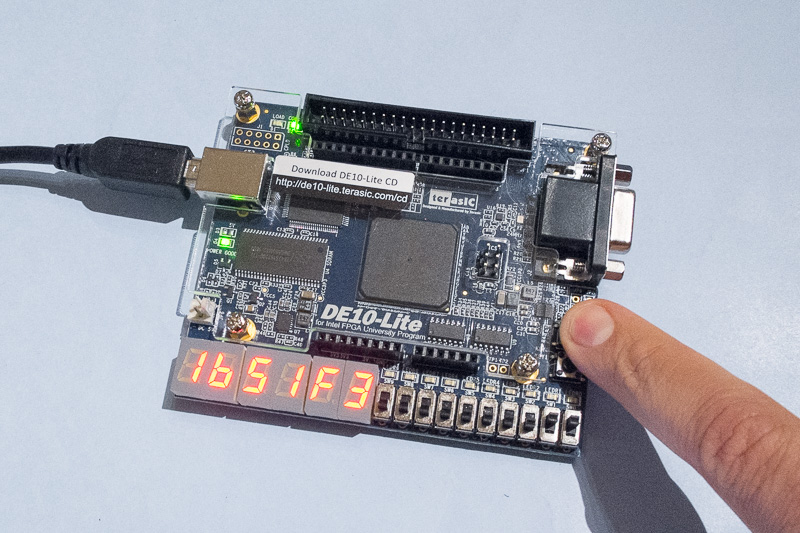

Please note that the students on the tables are such fees:

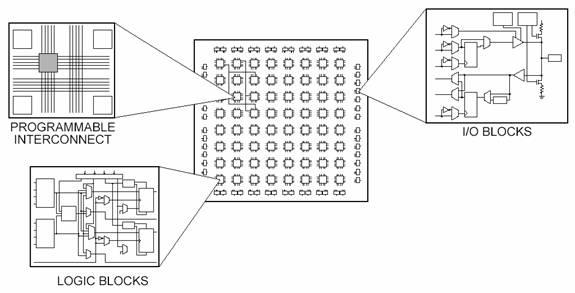

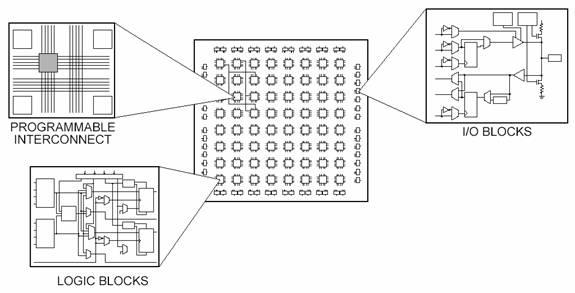

The central chip on this board is an FPGA “Variable Iron” chip (Programmable Logic Integrated Circuit) or FPGA (Field Programmable Gate Array) in English. FPGA / FPGA - a matrix of cells with variable logic function. One cell can be And, the other - OR, the third - a bit of memory. There is no processor in this FPGA, but it can be created on the fly, by changing the contents of the special configuration memory, the bits that are connected to the multiplexers, which change the function of the cell:

At a meeting in another room, it was interesting to observe that when it comes to teaching electronics, each Russian university has its own face:

1. The Moscow Institute of Electronic Technology (MIET), as you can see in the photograph of Alexander Silantyev with his slide below, is remarkable for its connections with Zelenograd electronic companies ( http://multicore.ru , http://milandr.ru , http: // km211 .ru ), Micron and Angstrom factories, and other companies surrounding them.

2. Moscow Institute of Physics and Technology (MIPT) rests on the processor architecture and micro-architecture. This happened because of the cooperation of MIPT with the MCST (the Elbrus developer) and Intel.

3. Moscow State University (MGU) focuses on algorithms for electronic design automation (Electronic Design Automation - EDA).

4. Regional universities - Nizhny Novgorod NSTU, Samara University (formerly Samara State Aerospace University - SSAU), Novosibirsk NSTU - look no longer at chip design, but at the system level, offering courses on microcontrollers, DSP and FPGA, with demand orientation from Russian equipment manufacturers.

In addition to Timur Paltashev from AMD and me from MIPS, representatives of other development companies also spoke at the meeting, in particular:

1. Sergey Brazhnikov (NPK Technological Center) spoke about their programs for designing semi-custom-made VLSI using CAD “Ark” tools.

2. Alexander Kamkin, a leading researcher at the Institute for System Programming of the Russian Academy of Sciences (ISP RAS), told about verification. He made a report “General methodology for verification of microprocessors: test programs, execution traces, co-simulation of RTL-model and architecture model. Automation of the generation of test programs for microprocessors with MIPS architecture using the MicroTESK tool ” .

3. Representatives of National Instruments talked about their means of prototyping monitoring devices, in particular LabVIEW .

As I have already mentioned, some of the reports at the seminar were deleted. Charles Danchek, author of the popular distance course from eNano (educational department of RUSNANO) and Timur Paltashev, manager of AMD, spoke on Skype from California.

In the gray cap in the top row is Stanislav Zhelio, the creator of the schoolMIPS project - the simplest RISC processor in the Universe.

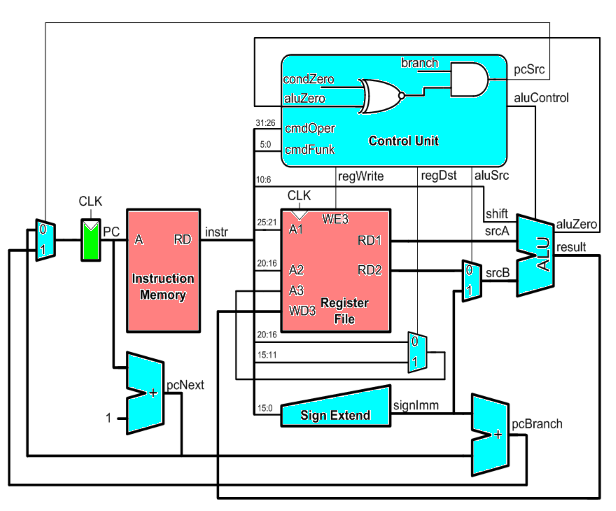

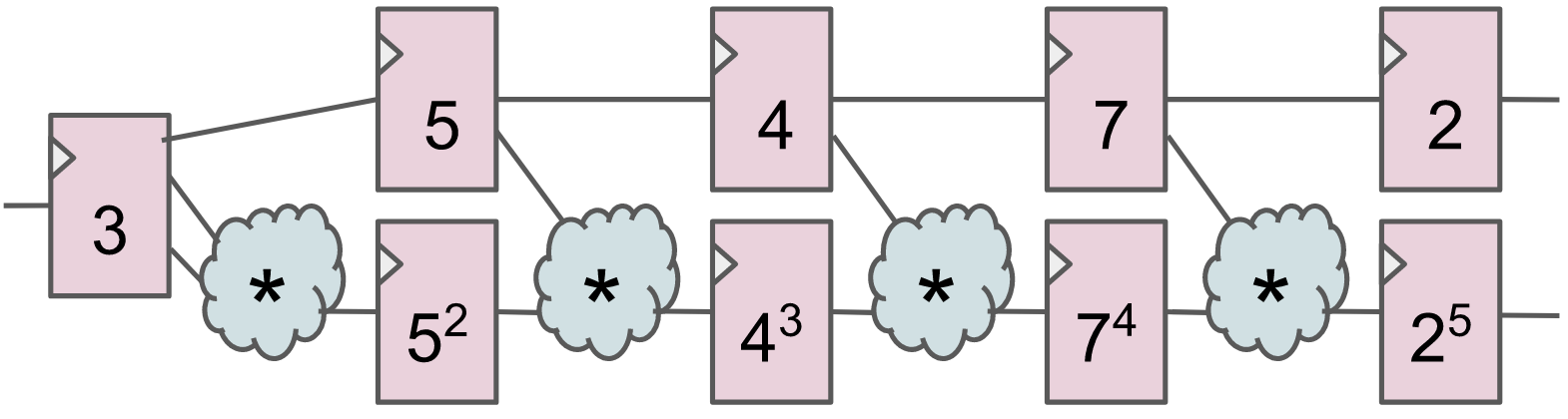

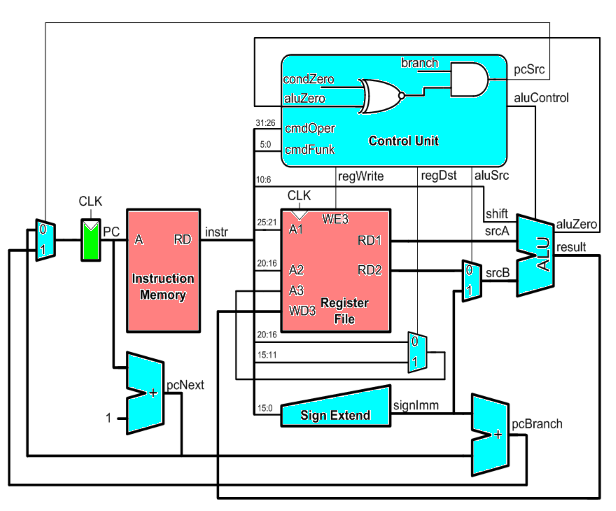

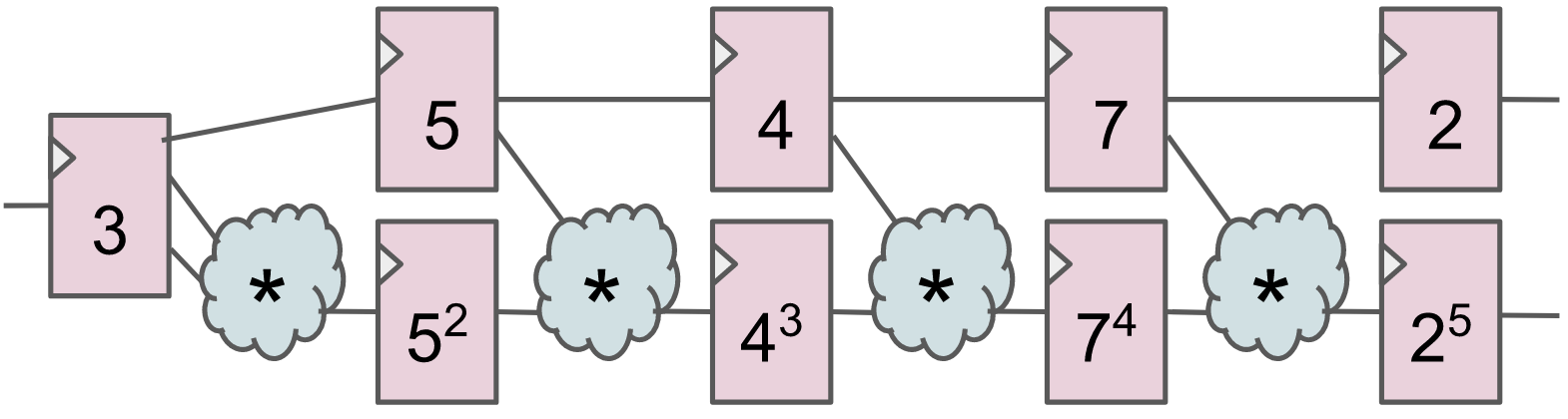

Even schoolchildren can understand the structure of schoolMIPS, its description takes only a few hundred lines on the chain. But at the same time, you can run programs compiled with the standard GCC toolchain on schoolMIPS:

Stanislav Zhelio also significantly expanded the MIPSfpga processor - a variant of the industrial processor core MIPS microAptiv UP, licensed free of charge by university researchers for projects such as creating their own co-processors and observing the operation of the pipeline. Stanislav is now leading the MIPSfpga + project, to which he added an interrupt controller, an interface from external SDRAM, and sorted Linux on it on an Altera / IntelFPGA board.

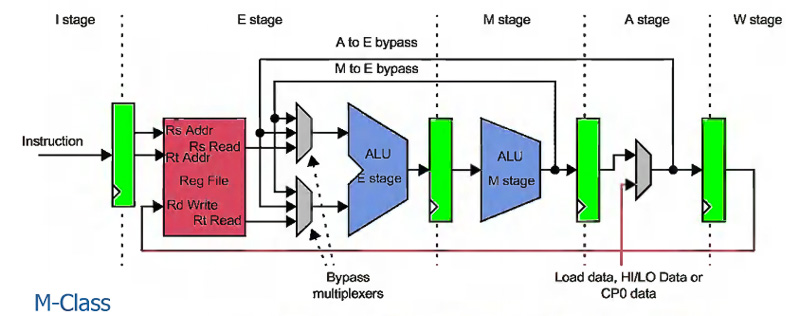

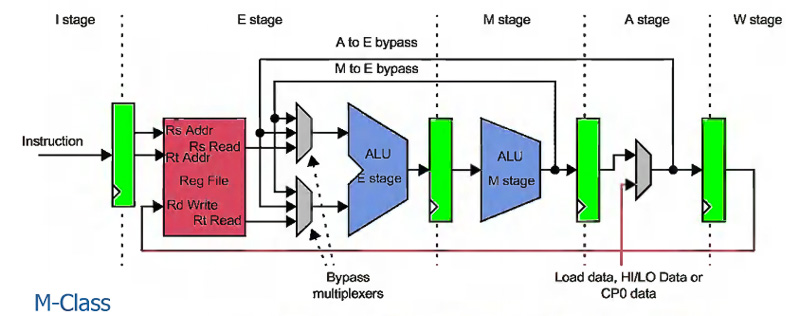

Although MIPSfpga is considered a small, economical core, it is hundreds of times larger in the number of lines on the chain than schoolMIPS, it implements the full MIPS32 architecture and executes instructions using a five-stage bypass pipeline, includes a cache and a memory management device:

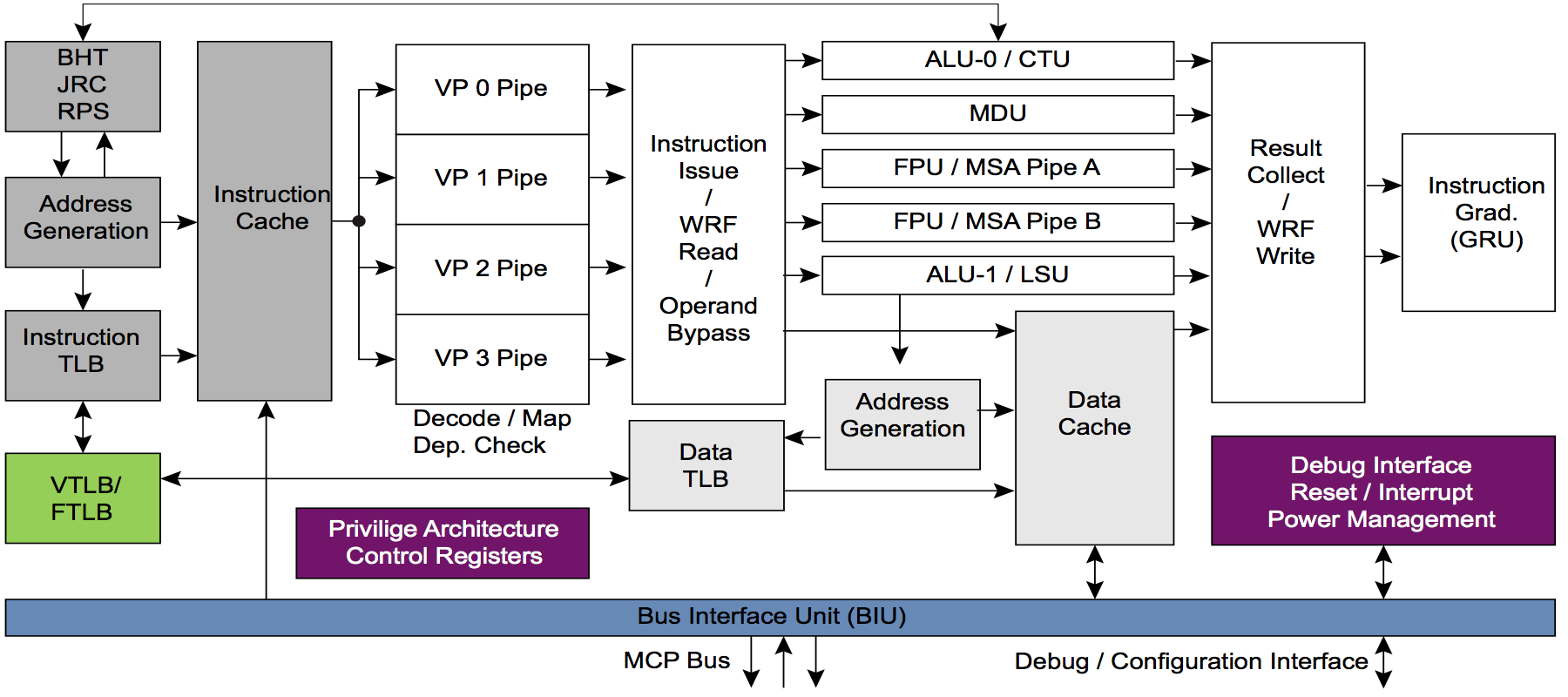

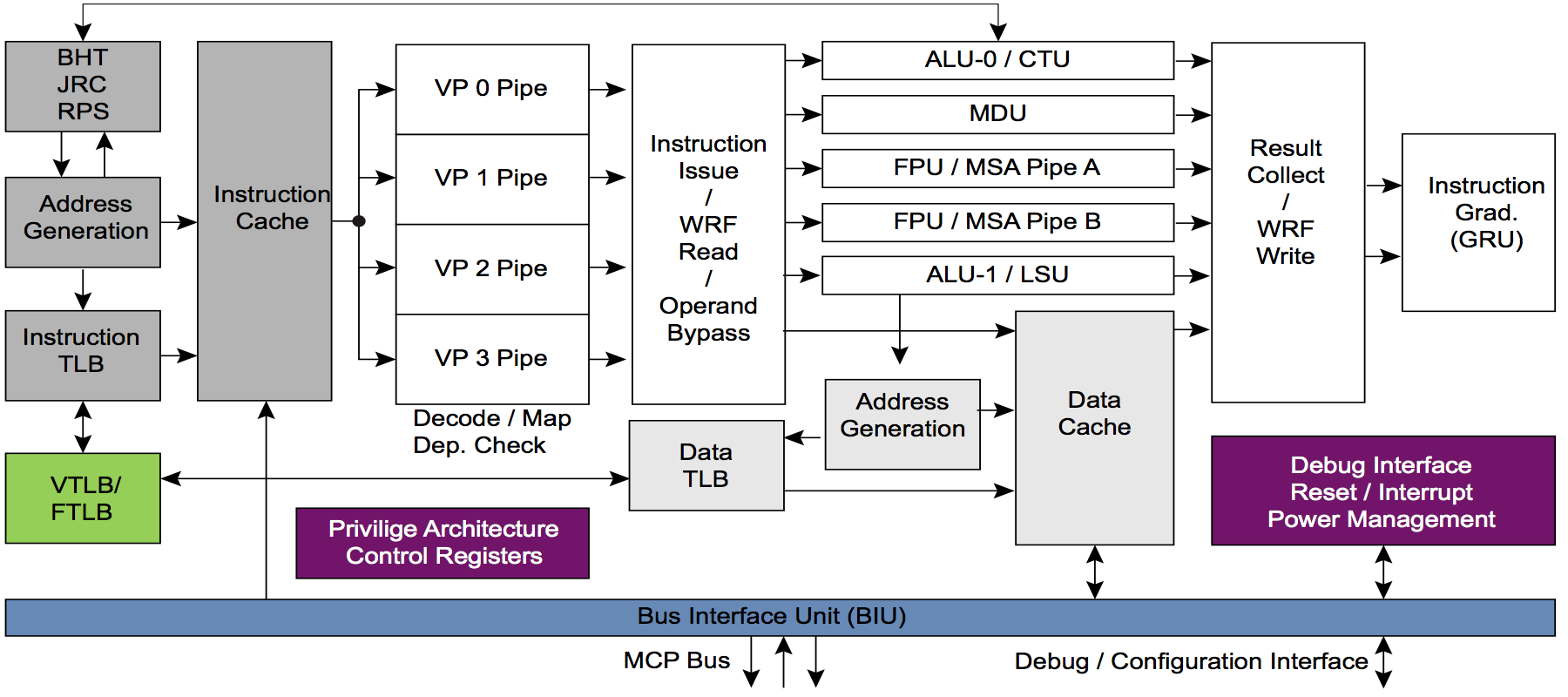

But for comparison, the pipeline of the MIPS I6400 processor core, which contains an order of magnitude more lines of verification, than MIPSfpga. The 64-bit MIPS I6400 is built around a superscalar pipeline with hardware support for multithreading and virtualization, vector registers and an interface with a coherence manager that provides a consistent state of caches in a multi-core system.

Here the seminar participants talk about the integration of schoolMIPS in the simplest system on a chip with a light sensor:

But on the left - schoolgirl Dasha Krivoruchko, who also mastered schoolMIPS, and on the right - severe Chelyabinsk woman-chemist Katerina Polutina, the conference organizer:

Here Dasha tells how she added multiplication instruction to schoolMIPS:

Dasha also performed at Tomsk Lyceum number 8, where she spoke about what she was doing:

But another schoolboy, Arseny Chegodaev, shows his project. He also came to Tomsk to give a report on a special section for schoolchildren, but we made the video at the Summer School for Young Programmers in Novosibirsk:

At the end, our company of speakers and teachers at the seminar dined in refined restaurants of Siberian cuisine:

in which there are sliced fish, frozen taiga berries and other local specialties:

A series of short, unedited videos from the conference phone and courses from the phone:

Long unedited entries total:

Verdict : Tomsk is a great place for organizing meetings of teachers, visiting brainstorming sessions and other similar events. This is an opportunity to change the atmosphere for Muscovites and St. Petersburg people, and the collection of museums (local lore with Kulay culture, the GULAG museum, and others) are interesting also for guests from Silicon Valley and other distant places. I want to go back there. A serious microelectronics development center will not be in Tomsk soon, but Harris & Harris textbooks are already used in universities there, people are smart there, so the appearance of such a focus there may be a question of the amount of effort involved.

The biggest gap in the current Russian microelectronics training programs that I noticed is a severe lack of materials and instructors for verification (unit-level and system-level) using SystemVerilog, coverage-based constrained-random, assertions, formal, etc. - without this group real chip technology is not done.

After Tomsk there was Novosibirsk, where a two-day seminar / hackathon of students of a dozen (or more?) Novosibirsk lyceums under the guidance of Tatyana Kolesnikova , the head of a technopark for schoolchildren, took place . The Technopark itself is located in a building that residents of the Novosibirsk Academgorodok call “Geese”. There is also a restaurant "Geese":

Here is a photo of this building from LJ (my photos of this building are less impressive):

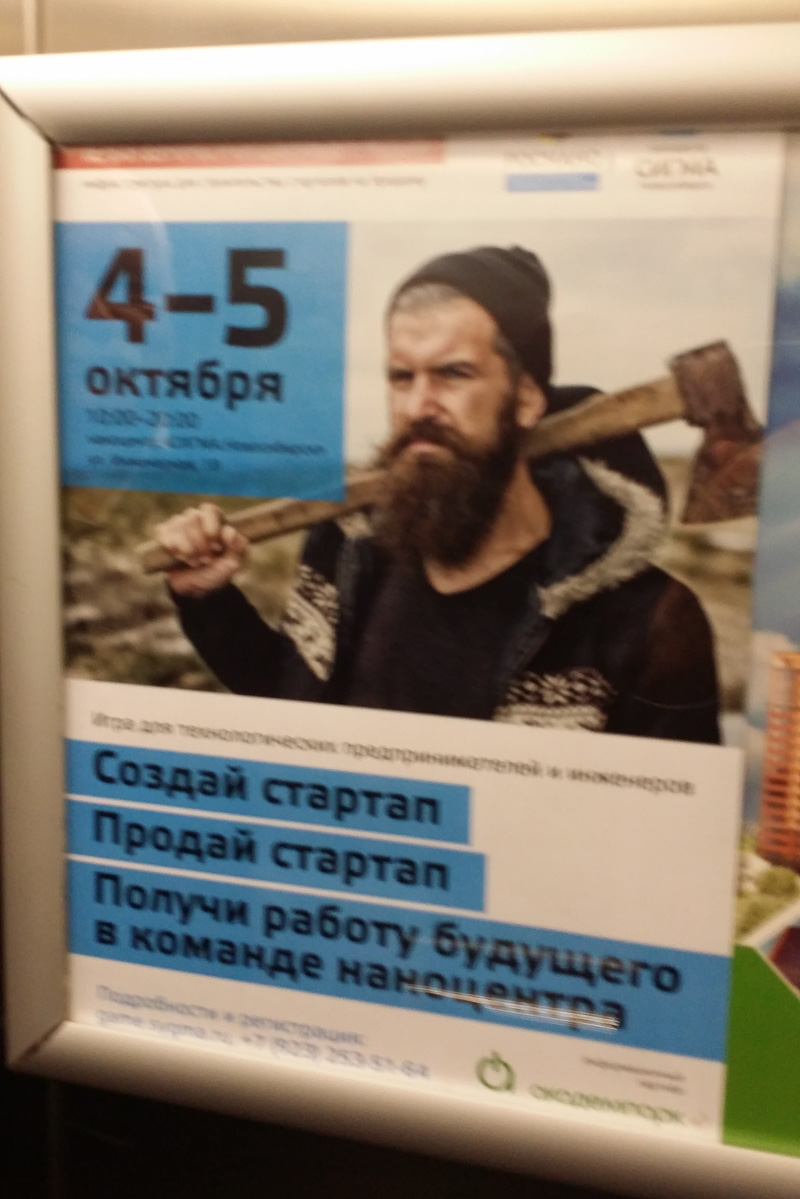

At the entrance was a poster depicting a stern Siberian man:

The workshop and hackathon for schoolchildren consisted of two parts - an exercise with microcircuits of a small degree of integration and an exercise with FPGA / FPGA. For exercises with FPGAs , such a set was used as a basis.

Chips of a small degree of integration (we used CMOS 4000) - this is old (produced from the 1970s), but still the most visual way to show the logic elements, the D-flip-flop and simple counters. This helps to prepare for working with FPGAs and Verilog, as it helps to build a mental model of the circuit in the student's brain. Otherwise, the student will treat the chain as something like a strange version of Python, and as a result will make inefficient schemes.

Lecture at a seminar / hackathon:

Results :

Until the two-day seminar / hakaton in Novosibirsk Academgorodsk, there was a week-long seminar / hakaton in Kiev and in the two-week Summer School for Young Programmers in the Novosibirsk Region . Comparison of all three seminars is in the presentation at the round table at Moscow State University , which was held on October 8. Here are his materials . This round table was organized by eNano, the educational department of RUSNANO.

The next stop after Novosibirsk was Nazarbayevsky University in Astana, Republic of Kazakhstan. From the main entrance the university looks like this:

Go inside:

We work with FPGA boards:

The Republic of Kazakhstan is a rather interesting place. On the one hand, this is a country whose economy is built on natural resources (ore, gas, oil, uranium). On the other hand, the society of Kazakhstan is very similar to the Russian, both in the organization of the state and in respect for culture - in Kazakhstan, for example, there are good museums. For example, in Abu Dhabi (through which I flew from Kazakhstan) the society was richer, but the museums were built (or, more precisely, bought) quite recently.

Timur Paltashev (who is from AMD) told me that in the 1970s, the Kazakh Polytechnic University had laboratory work with the creation of microcode for EC computers (IBM 360/370), and closer to the present, the familiar Dzholdas Dzhuruntayev (right) wrote a decent course in basic digital circuitry, though covering only part of the area, which is not enough now:

But Kazakhstan is now of course at a very early stage of development of the ecosystem in the microelectronic region. The management of Nazarbayevsky University (in which there are people from MIPT) and other Kazakh organizations are now puzzled how to optimize development. They invited several teachers from abroad who are familiar with the VLSI theme. The instructors have introduced a course on VHDL and are now starting to enter labs on the FPGA. They live in a high-quality apartment complex at the university, which is similar to the Marriott Residence Inn hotel.

At Nazarbayev University there was a girl (sorry, I forgot to take a picture of her) who makes an instrument for collecting information from a telescope using FPGA / FPGA data processing.

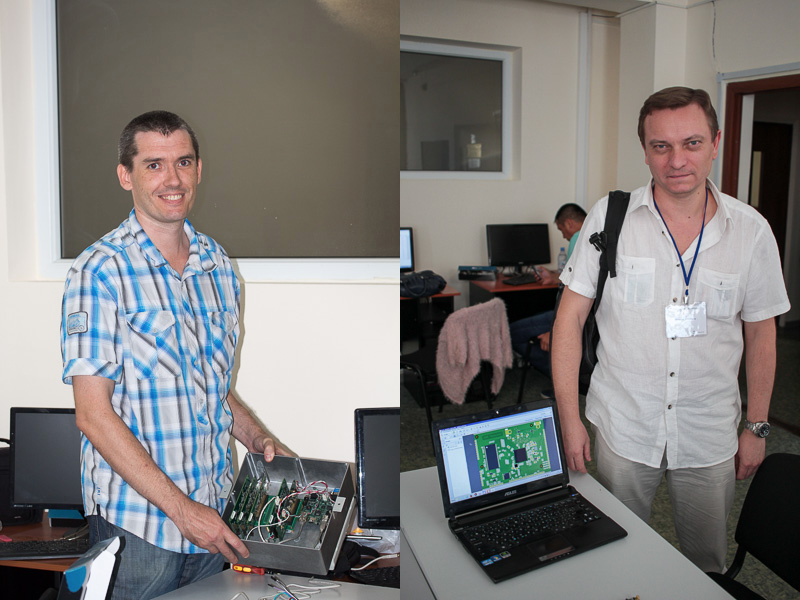

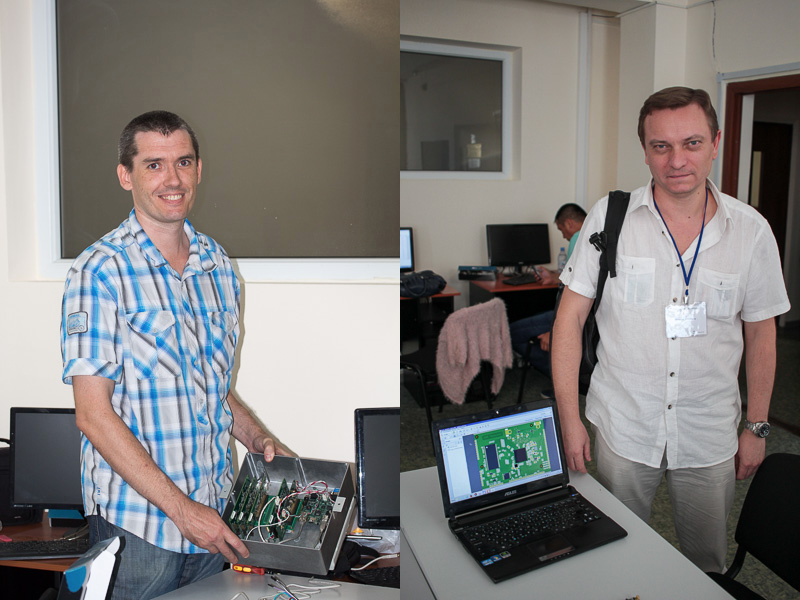

The university is also trying to spread the culture of make-up among the people of Kazakhstan and think how to establish cooperation with local Kazakh companies. There are such companies. For example, there is the manufacturer of switches Eltex Alatau, or these two gentlemen: on the left, Konstantin Malishich with a seismic analyzer designed in Kazakhstan, based on several microcontrollers and embedded processors, and on the right, Vladimir Makhonin, the developer of a network of Kazakh miners. Vladimir Makhonin has an idea to make the first ASIC in Kazakhstan (in cooperation with Russian colleagues in Zelenograd):

In the end, to consolidate the material, I will show two more slides with the theory - from the presentation of Amir Ayupov, a Russian engineer who works at Intel in Santa Clara, California, where he is engaged in modeling the microarchitecture of Intel processors and analyzing their performance. In October, Amir and I made a joint lecture on Skype to increase the morale of students at the Samara University, at the request of their dean, Ilya Kudryavtsev, one of the participants in the seminar in Tomsk. The lecture with all the slides of the two presentations and the sound is here . Amir took these slides from the presentation of his colleague, MIPT teacher Pavel Kryukov:

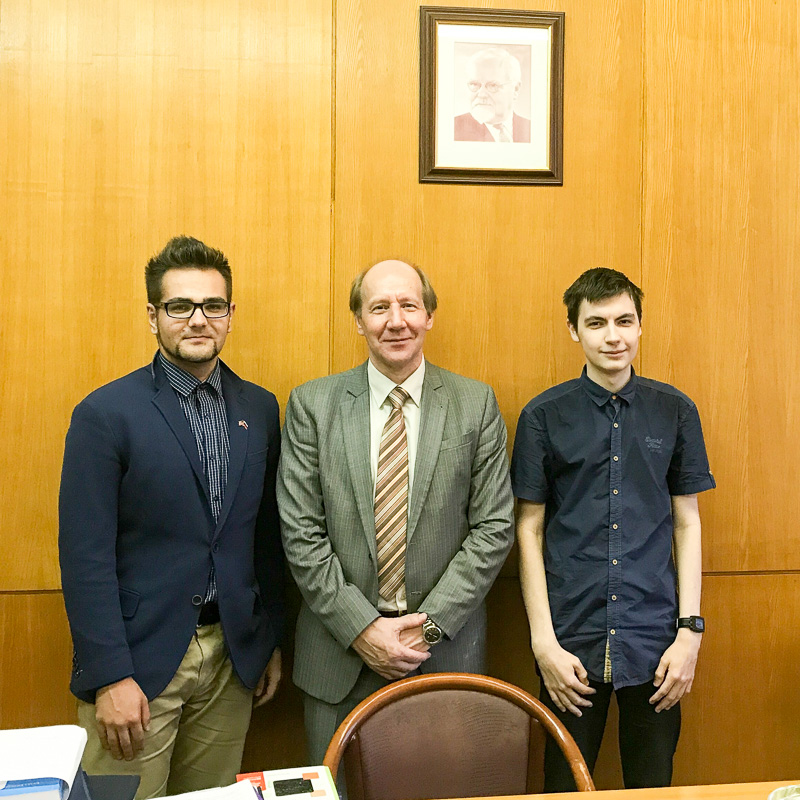

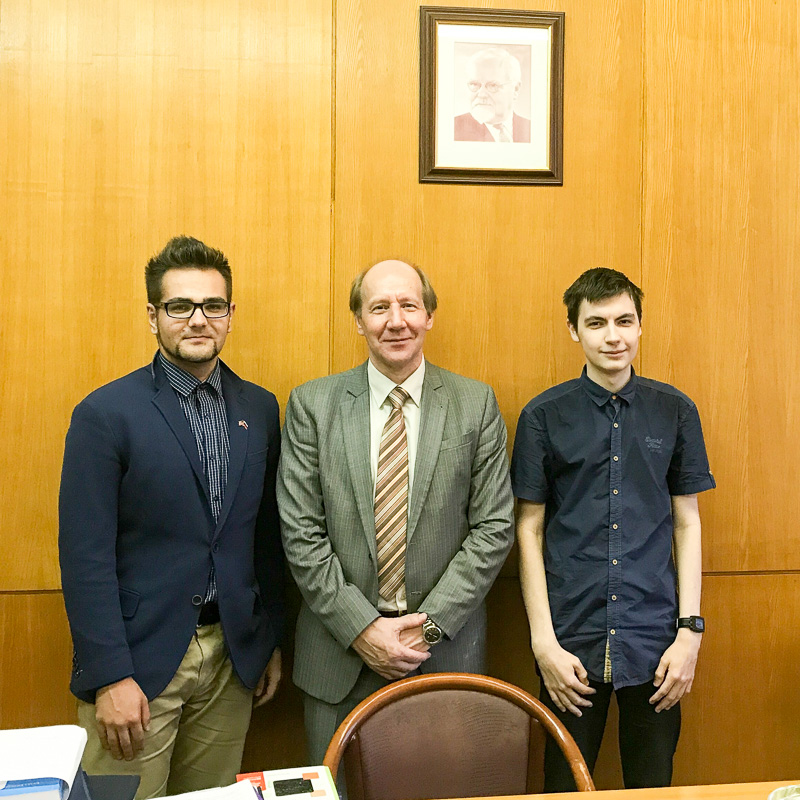

In September, Amir went to VMK MSU, where labs with Verilog and FPGA are now rapidly developing, even designed their own small MIPS-compatible processor core for educational purposes. Here Amir (left), along with Deputy Dean of the CMC of Moscow State University Sergei Lozhkin and the VMC student Vladimir Zhukov.

To which I led Amir and the staff of the UMC MSU: we are with them, as well as with the participants of the seminar in Tomsk, we are all working together on methodological manuals on Verilog and FPGA, in order to make a manual that is superior to, for example , the course materials from MIT . On this occasion, we will meet on Monday, January 25 at Moscow State University, and then there will be another meeting in St. Petersburg, also during the pre-Christmas week. Ahead of the New Year holidays, during which many participants in this project will write these labs. Here is a picture from the labs on the principles of pipelining, the code for which we keep on the githaba (but not the text - the text will appear when everyone has written and the course beta testing begins):

Summary: The next stage in the development of an electronics ecosystem is expansion. For Russia, it is not enough to have only a few teams to develop specialized chips for the domestic market.For everything to become like in Silicon Valley, universities need to release an order of magnitude more young engineers who have the skills to develop logical blocks in Verilog and VHDL hardware description languages, use a software for physical design like Synopsys IC Compiler and Cadence Innovus, knowledge of algorithms for creating your own Russian programs for automating chip design, etc. The first steps in the design of smart chips using the register transfer level (RTL) methodology can be made by already advanced students of physical schools using variable-iron projects based on FPGA / FPGA (Field Programmable Gate Arrays) chips.

After meetings in Moscow and St. Petersburg - to be continued.

To move from individual successes to a developed ecosystem, it is necessary to twist the formation. In September , a meeting was held in Tomsk , where teachers and engineers from Moscow, Siberia, the Volga region, California and other places shared their experience in teaching microelectronics. At the same time, a training seminar on SystemVerilog, VHDL, FPGA, CPU IP was held there, which was attended not only by Russians, but also by students from China and Vietnam, among whom information was quickly spread that they were teaching something useful for their career. Under the cut - a report on this and related events. Actors: Tomsk and Novosibirsk universities, Moscow State University, MIPT and MIET, Novosibirsk Lyceums, Russian company MCST, American MIPS, AMD and National Instruments, British Imagination and Kazakh Nazarbayev University.

Before you see photos of pretty diners at a seminar in a Siberian restaurant, let's say a few words about the position of the technologies discussed in the universe, for those who came to this post from another part of the technological universe.

')

In any serious modern electronic device there is a hardware-software dualism:

Not only the processor is designed in hardware description languages, but also peripheral device controllers and their connections in the system:

You all know how programs are compiled - in the instructions that the processor executes:

But the schema descriptions in the Verilog hardware description language are compiled (synthesized) not into instructions, but into schemas. As a special case - in the processor circuit which takes from memory and executes instructions. In the end, the description on the chain turns into microcircuit tracks and transistors. This is not a “microcode”, honestly (“microcode” is about something else). Therefore, it is not quite correct to say “programming on the chain”, it’s like saying “HTML programming” Programs are chains of instructions for the von Neumann machine, not a scheme (although you can use the verification to program how to fly an airplane on the highway). It is correct to say “design the circuits on the chain at the register transfer level” or simply “write code on the chain”.

We now turn to the event in Tomsk. The idea to make a workshop on the development of digital microchips was born in December 2016 right here at this table in the beer garden in the middle of Silicon Valley, California. Physicist / chemist Anatoly Korkin (second from left) initially planned to make a purely conference in Tomsk for physicists and chemists, including those who create production technologies in the semiconductor industry. Anatoly himself once worked at Motorola in Arizona, and some of his colleagues, whom he invited to the conference, developed technologies for the production of memory chips.

The problem is that physicists without programmers themselves will not build a computer system. Worse, physicists will not build this system with programmers either. For a computer or gadget to work, between physics and programming there must be a bridge from a chain of technologies that includes microarchitecture, logical hardware design at the register transfer level (RTL), design automation using logical and physical synthesis (logic synthesis, floorplanning , place & route). Therefore, Anatoly met with a professor from the University of California, Charles Danchek, who last year gave very popular lectures at MISiS with an overview of the chip design chain (first left), as well as AMD manager Timur Paltashev (first right), and your humble servant. And it was decided to do a seminar in Siberia (although Timur and Charles could only participate remotely).

Tomsk turned out to be a visually interesting city, with a cozy center and a large number of buildings, very different from the architecture of Silicon Valley:

The city has a high percentage of residents - students, as there are several universities in Tomsk, including Tomsk State University (where we held a seminar), Tomsk Polytechnic University (from which students came to us) and Tomsk University of Control Systems and Radio Electronics (TUSUR ), from which listeners came to us:

On the first day, students were taught by Nikita Polyakov from the MCST and MIPT (with a beard on the left — he taught Verilog) and Ilya Kudryavtsev from Samara University (with a beard on the right — he taught VHDL). VHDL is also a hardware description language, it is loved by the military of all countries and some groups of some companies (Texas Instruments, IBM, Imagination Technologies). PoverVR inside Apple iPhone is written in VHDL.

Please note that the students on the tables are such fees:

The central chip on this board is an FPGA “Variable Iron” chip (Programmable Logic Integrated Circuit) or FPGA (Field Programmable Gate Array) in English. FPGA / FPGA - a matrix of cells with variable logic function. One cell can be And, the other - OR, the third - a bit of memory. There is no processor in this FPGA, but it can be created on the fly, by changing the contents of the special configuration memory, the bits that are connected to the multiplexers, which change the function of the cell:

At a meeting in another room, it was interesting to observe that when it comes to teaching electronics, each Russian university has its own face:

1. The Moscow Institute of Electronic Technology (MIET), as you can see in the photograph of Alexander Silantyev with his slide below, is remarkable for its connections with Zelenograd electronic companies ( http://multicore.ru , http://milandr.ru , http: // km211 .ru ), Micron and Angstrom factories, and other companies surrounding them.

2. Moscow Institute of Physics and Technology (MIPT) rests on the processor architecture and micro-architecture. This happened because of the cooperation of MIPT with the MCST (the Elbrus developer) and Intel.

3. Moscow State University (MGU) focuses on algorithms for electronic design automation (Electronic Design Automation - EDA).

4. Regional universities - Nizhny Novgorod NSTU, Samara University (formerly Samara State Aerospace University - SSAU), Novosibirsk NSTU - look no longer at chip design, but at the system level, offering courses on microcontrollers, DSP and FPGA, with demand orientation from Russian equipment manufacturers.

In addition to Timur Paltashev from AMD and me from MIPS, representatives of other development companies also spoke at the meeting, in particular:

1. Sergey Brazhnikov (NPK Technological Center) spoke about their programs for designing semi-custom-made VLSI using CAD “Ark” tools.

2. Alexander Kamkin, a leading researcher at the Institute for System Programming of the Russian Academy of Sciences (ISP RAS), told about verification. He made a report “General methodology for verification of microprocessors: test programs, execution traces, co-simulation of RTL-model and architecture model. Automation of the generation of test programs for microprocessors with MIPS architecture using the MicroTESK tool ” .

3. Representatives of National Instruments talked about their means of prototyping monitoring devices, in particular LabVIEW .

As I have already mentioned, some of the reports at the seminar were deleted. Charles Danchek, author of the popular distance course from eNano (educational department of RUSNANO) and Timur Paltashev, manager of AMD, spoke on Skype from California.

In the gray cap in the top row is Stanislav Zhelio, the creator of the schoolMIPS project - the simplest RISC processor in the Universe.

Even schoolchildren can understand the structure of schoolMIPS, its description takes only a few hundred lines on the chain. But at the same time, you can run programs compiled with the standard GCC toolchain on schoolMIPS:

Stanislav Zhelio also significantly expanded the MIPSfpga processor - a variant of the industrial processor core MIPS microAptiv UP, licensed free of charge by university researchers for projects such as creating their own co-processors and observing the operation of the pipeline. Stanislav is now leading the MIPSfpga + project, to which he added an interrupt controller, an interface from external SDRAM, and sorted Linux on it on an Altera / IntelFPGA board.

Although MIPSfpga is considered a small, economical core, it is hundreds of times larger in the number of lines on the chain than schoolMIPS, it implements the full MIPS32 architecture and executes instructions using a five-stage bypass pipeline, includes a cache and a memory management device:

But for comparison, the pipeline of the MIPS I6400 processor core, which contains an order of magnitude more lines of verification, than MIPSfpga. The 64-bit MIPS I6400 is built around a superscalar pipeline with hardware support for multithreading and virtualization, vector registers and an interface with a coherence manager that provides a consistent state of caches in a multi-core system.

Here the seminar participants talk about the integration of schoolMIPS in the simplest system on a chip with a light sensor:

But on the left - schoolgirl Dasha Krivoruchko, who also mastered schoolMIPS, and on the right - severe Chelyabinsk woman-chemist Katerina Polutina, the conference organizer:

Here Dasha tells how she added multiplication instruction to schoolMIPS:

Dasha also performed at Tomsk Lyceum number 8, where she spoke about what she was doing:

But another schoolboy, Arseny Chegodaev, shows his project. He also came to Tomsk to give a report on a special section for schoolchildren, but we made the video at the Summer School for Young Programmers in Novosibirsk:

At the end, our company of speakers and teachers at the seminar dined in refined restaurants of Siberian cuisine:

in which there are sliced fish, frozen taiga berries and other local specialties:

A series of short, unedited videos from the conference phone and courses from the phone:

Long unedited entries total:

Verdict : Tomsk is a great place for organizing meetings of teachers, visiting brainstorming sessions and other similar events. This is an opportunity to change the atmosphere for Muscovites and St. Petersburg people, and the collection of museums (local lore with Kulay culture, the GULAG museum, and others) are interesting also for guests from Silicon Valley and other distant places. I want to go back there. A serious microelectronics development center will not be in Tomsk soon, but Harris & Harris textbooks are already used in universities there, people are smart there, so the appearance of such a focus there may be a question of the amount of effort involved.

The biggest gap in the current Russian microelectronics training programs that I noticed is a severe lack of materials and instructors for verification (unit-level and system-level) using SystemVerilog, coverage-based constrained-random, assertions, formal, etc. - without this group real chip technology is not done.

After Tomsk there was Novosibirsk, where a two-day seminar / hackathon of students of a dozen (or more?) Novosibirsk lyceums under the guidance of Tatyana Kolesnikova , the head of a technopark for schoolchildren, took place . The Technopark itself is located in a building that residents of the Novosibirsk Academgorodok call “Geese”. There is also a restaurant "Geese":

Here is a photo of this building from LJ (my photos of this building are less impressive):

At the entrance was a poster depicting a stern Siberian man:

The workshop and hackathon for schoolchildren consisted of two parts - an exercise with microcircuits of a small degree of integration and an exercise with FPGA / FPGA. For exercises with FPGAs , such a set was used as a basis.

Chips of a small degree of integration (we used CMOS 4000) - this is old (produced from the 1970s), but still the most visual way to show the logic elements, the D-flip-flop and simple counters. This helps to prepare for working with FPGAs and Verilog, as it helps to build a mental model of the circuit in the student's brain. Otherwise, the student will treat the chain as something like a strange version of Python, and as a result will make inefficient schemes.

Lecture at a seminar / hackathon:

Results :

- Schoolchildren have figured out CMOS 4000 in less than a day, with time constraints, this material can be omitted.

- In one day, you can only deal with Verilog with an example of combinational logic.

- For sequential logic on Verilog need a second day or better prepared examples

Until the two-day seminar / hakaton in Novosibirsk Academgorodsk, there was a week-long seminar / hakaton in Kiev and in the two-week Summer School for Young Programmers in the Novosibirsk Region . Comparison of all three seminars is in the presentation at the round table at Moscow State University , which was held on October 8. Here are his materials . This round table was organized by eNano, the educational department of RUSNANO.

The next stop after Novosibirsk was Nazarbayevsky University in Astana, Republic of Kazakhstan. From the main entrance the university looks like this:

Go inside:

We work with FPGA boards:

The Republic of Kazakhstan is a rather interesting place. On the one hand, this is a country whose economy is built on natural resources (ore, gas, oil, uranium). On the other hand, the society of Kazakhstan is very similar to the Russian, both in the organization of the state and in respect for culture - in Kazakhstan, for example, there are good museums. For example, in Abu Dhabi (through which I flew from Kazakhstan) the society was richer, but the museums were built (or, more precisely, bought) quite recently.

Timur Paltashev (who is from AMD) told me that in the 1970s, the Kazakh Polytechnic University had laboratory work with the creation of microcode for EC computers (IBM 360/370), and closer to the present, the familiar Dzholdas Dzhuruntayev (right) wrote a decent course in basic digital circuitry, though covering only part of the area, which is not enough now:

But Kazakhstan is now of course at a very early stage of development of the ecosystem in the microelectronic region. The management of Nazarbayevsky University (in which there are people from MIPT) and other Kazakh organizations are now puzzled how to optimize development. They invited several teachers from abroad who are familiar with the VLSI theme. The instructors have introduced a course on VHDL and are now starting to enter labs on the FPGA. They live in a high-quality apartment complex at the university, which is similar to the Marriott Residence Inn hotel.

At Nazarbayev University there was a girl (sorry, I forgot to take a picture of her) who makes an instrument for collecting information from a telescope using FPGA / FPGA data processing.

The university is also trying to spread the culture of make-up among the people of Kazakhstan and think how to establish cooperation with local Kazakh companies. There are such companies. For example, there is the manufacturer of switches Eltex Alatau, or these two gentlemen: on the left, Konstantin Malishich with a seismic analyzer designed in Kazakhstan, based on several microcontrollers and embedded processors, and on the right, Vladimir Makhonin, the developer of a network of Kazakh miners. Vladimir Makhonin has an idea to make the first ASIC in Kazakhstan (in cooperation with Russian colleagues in Zelenograd):

In the end, to consolidate the material, I will show two more slides with the theory - from the presentation of Amir Ayupov, a Russian engineer who works at Intel in Santa Clara, California, where he is engaged in modeling the microarchitecture of Intel processors and analyzing their performance. In October, Amir and I made a joint lecture on Skype to increase the morale of students at the Samara University, at the request of their dean, Ilya Kudryavtsev, one of the participants in the seminar in Tomsk. The lecture with all the slides of the two presentations and the sound is here . Amir took these slides from the presentation of his colleague, MIPT teacher Pavel Kryukov:

In September, Amir went to VMK MSU, where labs with Verilog and FPGA are now rapidly developing, even designed their own small MIPS-compatible processor core for educational purposes. Here Amir (left), along with Deputy Dean of the CMC of Moscow State University Sergei Lozhkin and the VMC student Vladimir Zhukov.

To which I led Amir and the staff of the UMC MSU: we are with them, as well as with the participants of the seminar in Tomsk, we are all working together on methodological manuals on Verilog and FPGA, in order to make a manual that is superior to, for example , the course materials from MIT . On this occasion, we will meet on Monday, January 25 at Moscow State University, and then there will be another meeting in St. Petersburg, also during the pre-Christmas week. Ahead of the New Year holidays, during which many participants in this project will write these labs. Here is a picture from the labs on the principles of pipelining, the code for which we keep on the githaba (but not the text - the text will appear when everyone has written and the course beta testing begins):

Summary: The next stage in the development of an electronics ecosystem is expansion. For Russia, it is not enough to have only a few teams to develop specialized chips for the domestic market.For everything to become like in Silicon Valley, universities need to release an order of magnitude more young engineers who have the skills to develop logical blocks in Verilog and VHDL hardware description languages, use a software for physical design like Synopsys IC Compiler and Cadence Innovus, knowledge of algorithms for creating your own Russian programs for automating chip design, etc. The first steps in the design of smart chips using the register transfer level (RTL) methodology can be made by already advanced students of physical schools using variable-iron projects based on FPGA / FPGA (Field Programmable Gate Arrays) chips.

After meetings in Moscow and St. Petersburg - to be continued.

Source: https://habr.com/ru/post/345286/

All Articles