Network JTAG programmer for Altera Quartus Prime from Raspberry Pi3

A software has been released that allows the Raspberry Pi3 to make a JTAG network programmer for Altera Quartus Prime CAD software. This solution allows you to remotely load Altera / Intel FPGAs and even remotely debug using the SignalTap tool. Next, tell

how to use this software.

In fact, all this software was created for the Mars Rover 2RPI expansion card, which is shown above in the photo. The board has onboard Intel Cyclone IV FPGA and can be connected via an adapter to the Raspberry Pi3 / Pi2 / Pi-Zero. I probably won't describe the fee in detail here, I have already written about it in geektimes . However, nothing prevents you from using the same software on your own with other FPGA cards - all you need to do is to make a simple JTAG wire and connect it to the GPIO microcomputer raster. There only need four signals tck → GPIO7, tms → GPIO0, tdi → GPIO11 and tdo ← GPIO1, and, of course, a good “Earth” / GND.

To be honest, using the Raspberry Pi as a JTAG programmer was possible before. Quartus Prime CAD software allows you to generate SVF files when compiling projects, and the OpenOCD server can load SVF files into FPGA via GPIO pins of the parser.

However, unfortunately, OpenOCD cannot be used in conjunction with the Quartus CAD system itself.

Now we have other software where possible. The software can be downloaded for free without registration and without SMS here on the project website .

')

The archive contains two files.

The nw_jtag_srv file is the executable file for the raspberry pi. It is a JTAG server managed over a UDP / TCP network.

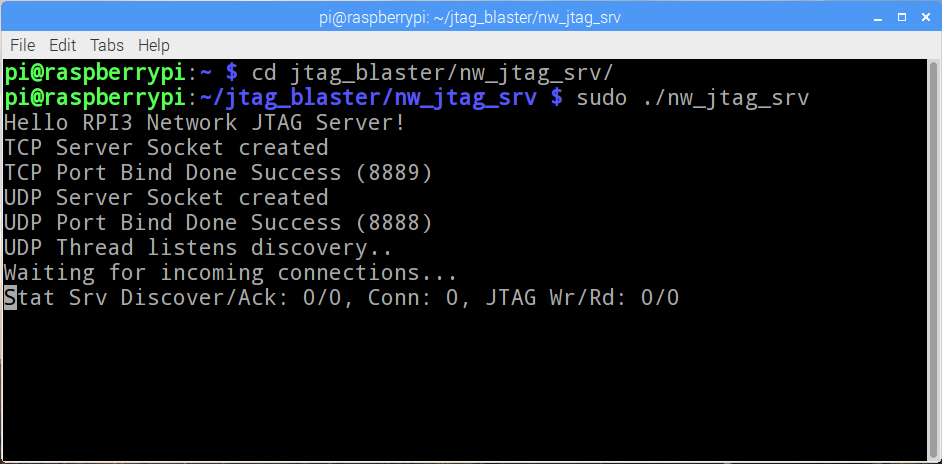

This is how nw_jtag_srv is run on the display in the console of the terminal. I use sudo, as I need access to GPIO:

The second file from the jtag_hw_net_blaster64.dll archive is the driver for Altera Quartus Prime. It needs to be copied to the c: \ altera \ 17.0 \ quartus \ bin64 folder or a different folder depending on the version of the quarter used.

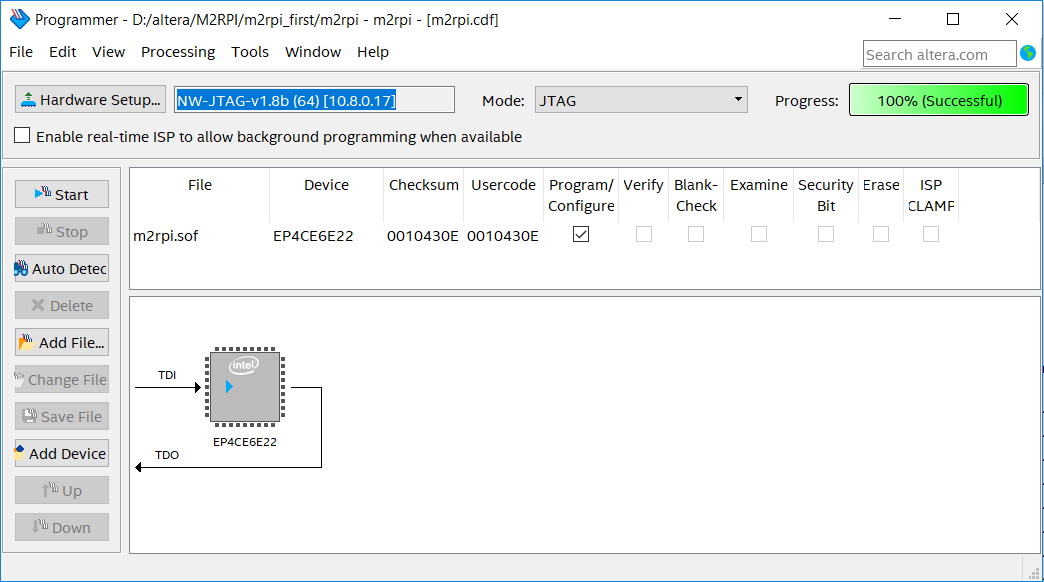

After that, launching the “programmer” from the environment of the quarter can detect a new network programmer (of course, if there is a network / connection between your computer and the control panel). The name of the detected network programmer contains the IP address of the parser:

Then everything is as usual. You can make the definition of a connected chip, load the FPGA.

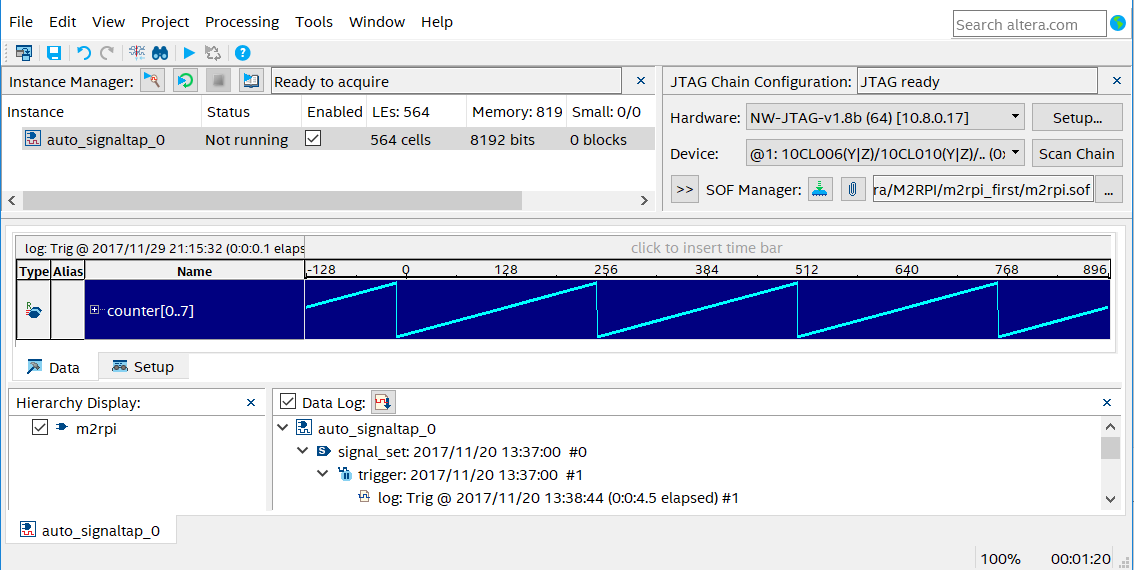

Moreover, the network programmer is detected in Altera SignalTap and you can remotely view the signals in the analyzed FPGA:

Of course, while this is the first version of the network programmer. During operation, possible bugs will be found and corrected.

I hope this tool will seem interesting to readers of Habr, and someone might want to use it in their development.

Source: https://habr.com/ru/post/343524/

All Articles