Our method of calculating the stack of printed circuit boards

While we are completing the final preparations for the serial production of the VESNIN server, I want to conduct an educational experiment - I will describe our internal methods and recommendations for calculating the stack of printed circuit boards. On the one hand, it is nice if our experience will be useful to someone. On the other hand, we ourselves are happy to receive practical comments in order to improve our practice. If it is interesting to read and discuss - welcome under cat.

Immediately to the point - this is what is written in this article:

Everything described below is not Know How, but in fact, collected and systematized data from different sources. We also do not claim absolute knowledge.

So let's go.

')

Preamble (as it usually happens).

Usually, the engineer roughly estimates the stack of the board, transfers it to the PCB manufacturer. In response, he receives a lot of Chinese forms with proposals - to which he usually agrees. They are reduced to a change in the thickness of the cores / prepregs, as well as the conductors and gaps in the CAM editor.

Usually it is normal. But there are three minuses:

Therefore, we prefer to form the stack so that its dependence on the characteristics of a particular PCB manufacturer is minimized. If you work with the same vendor, then it’s quite realistic to form a stack so that its modification by the manufacturer is not required at all. This is a saving of 1-2 weeks in preparation for production.

By the way offtopic.

Surely someone will want to ask - which is better, tightly coupled or loosely coupled differential pairs. Our opinion: better loosely coupled - they are easier to align in length. You can afford more serious bumps. There are no particular advantages of strongly coupled pairs over loosely coupled (if we do not consider strange topologies of type 5-14-5) from the point of view of SI in our opinion - no. For lovers of formal rules: one or two widths between conductors in a pair is normal. More - not so much. Less is difficult to align. Despite the fact that the EMC performance of strongly coupled pairs is much better, in absolute terms this “strongly” is not essential.

In order to more or less accurately form the stack of the printed circuit board - you need to know the parameters of specific cores and prepregs of the material used. The datasheets contain the averaged parameters for the entire group and are not suitable for accurate calculation. This information can be requested from both the material manufacturer and the PCB manufacturer. This is a table that looks like this (for each material manufacturer it has its own):

The thickness of different types of prepregs are usually the same for different manufacturers. Therefore, the information on the above image is relevant and usable without regard to the manufacturer of the material (Dk / Df, of course, everyone has different).

When designing a PCB stack, it is necessary to take into account that PCB manufacturers, as a rule, make a correction for lamination, reducing the dielectric constant (Dk) values of both prepregs and “cores” by about 0.2 relative to the values given in the documentation of the material manufacturer.

If Dk / Df values are given for different frequencies, it is recommended to use the values of these parameters for the frequency closest to the Nyquist frequency of the fastest interface on the PCB. For example, if PCI Express Gen3 is present in the PCB, then the Dk / Df values should be used for the frequency closest to 4 GHz.

Someone will argue: how, because the band of the same Gen3 extends right up to 18 GHz. This is true - but the PCIe specification regulates RL and IL before the Nyquist, and all these hellish gigahertzs do not pass through connectors, vias and the printed circuit board - will die out along the way. And if it passes, it’s a big question whether you will like the result.

In a situation where there are several different high-speed interfaces on the PCB — you should not use the Dk / Df values for different frequencies within the stack of one board. Although this approach is more accurate in terms of calculating the impedance, it will cause great difficulties in matching the stack with the PCB manufacturer (their test equipment is tuned to one specific frequency).

If the values of Dk / Df vary considerably with frequency, and impedance control is critical - it makes sense, having obtained the impedance values for the real interface frequency, recalculate it, taking Dk for some single frequency (the most critical interface). “Normalized” thus impedance value - specify as target for control by the PCB manufacturer.

For example, you make a calculation of the 100 Ohm trace for the 4 GHz frequency, use the Dk value for 4 GHz, and in accordance with the obtained data, perform the trace. Further, if you have, for example, interfaces requiring calculation for 10 GHz, substitute the value of Dk for a higher frequency into the initial calculation. Suppose that you get the impedance value of 105 Ohms. Our advice: here is 105 ohms and tell the PCB manufacturer to monitor. Do not fool him with different Dk for different frequencies on the same layer.

It also does not hurt to ask on the shore with what glass the fab works, so that there are no problems with delivery dates later. Because there are popular prepregs and not so much. Usually he always has 3-4 types in abundance, of which it is worth building a PCB stack. Low-loss materials are usually not in stock, due to the limited shelf life - therefore, the use of something special is always a question not so much of price, as of production time.

The table below shows the absolute values of changes in the thickness of one prepreg layer for different conditions of use. The tolerance for all values is 10%.

To more accurately calculate the change in prepreg thickness, you can use the following expression:

In the case when there is one layer of prepreg between the metallization layers - the values of thickness changes for the corresponding conditions should be summed up, since the change in the thickness of the prepreg is actually an indentation of a conductive pattern into it.

When forming a PCB layered description, the finishing value of the prepreg should be indicated. At the same time, the portion of prepreg pressed into the metallization pattern should not be included in the value of the final thickness in the documentation sent to the PCB manufacturer.

It is necessary to calculate the finishing thickness of the stack shown in the figure. Copper 1 oz is used on all plating layers. The initial prepreg thickness of 2116 is 5.1 mil.

The resulting stack will be:

The expression for calculating the etch factor for the process of electrical copper deposition is shown in the figure:

The table shows the Etch Factor values for different types of plating for various manufacturers. As you can see, they are very different. Therefore, the EF value is the first thing you should check with your PCB partner.

For cases when information on the value of EF from a specific production is not available - we can assume that EF takes the following values:

When calculating the metallization of the outer layers, the value of the thickness of copper weighing 1 oz, as a rule, is taken equal to 1.37 mil. It is recommended to separately set the weight of the base copper and the weight of the deposited copper. The total value is obtained by summing these two parameters. Typical values are shown in the table:

For the inner layers, the thickness value of copper weighing 1 oz, as a rule, is taken equal to 1.3 mil.

When taking into account the solder mask based on the following scheme:

In cases where it is not explicitly stated otherwise, we can assume that the solder mask has the following parameters:

Most manufacturers consider the values of C1, C2 and C3 equal to each other when considering the effect of the solder mask.

Some factories consider the values of C1 and C3 to be equal to the metallization thickness (T1), and C2 to 0.8 mil. The correctness of this approach is approximately confirmed by actual data obtained after the PCB production.

One of our PCB partners considers the solder mask thickness on solid sections of copper 0.79 - 1.18 mil, on the edges of conductors 0.2 mil. Also, this manufacturer recommends not including a solder mask when calculating the stack, since etching the outer layers results in the slightest overtravel (i.e. an increase in the impedance value), which is compensated by the mask in the face value of the theoretical impedance measurement of the outer layers without a mask.

This, by the way, is a good example of the fact that when working with this production - the thickness of the tracks on your PCB will be less than what is in the PCB pattern.

These are our internal recommendations and rules with which we must necessarily introduce all the engineers who design printed circuit boards. I hope that this article will be useful to those who scour the expanses of the Internet in search of scattered recommendations and trying to guess how it will turn out in his particular product. I invite you to share your experience in the comments - we will be happy to add your own. If there is interest, I will lay out a few more similar internal instructions.

Immediately to the point - this is what is written in this article:

- Materials for the production of printed circuit boards

- Accounting for changes in prepreg thickness during PCB manufacturing

- Accounting Etch Factor

- Features of the calculation of the thickness of metallization

- Accounting solder mask

Everything described below is not Know How, but in fact, collected and systematized data from different sources. We also do not claim absolute knowledge.

So let's go.

')

Materials for the production of printed circuit boards

Preamble (as it usually happens).

Usually, the engineer roughly estimates the stack of the board, transfers it to the PCB manufacturer. In response, he receives a lot of Chinese forms with proposals - to which he usually agrees. They are reduced to a change in the thickness of the cores / prepregs, as well as the conductors and gaps in the CAM editor.

Usually it is normal. But there are three minuses:

- The final product is different from what is described in your CD (sometimes a little more than full).

- Repeatability of the result when switching to another manufacturer is not. For example, we have a board that runs on two different fabs with completely different stacks (the source data in both cases were the same).

- If the thickness of the conductors on the printed circuit board is in the 4 mil zone, then any change in their width downwards seriously affects the loss. If the difference between a conductor of 6 mil and 5 mil is insignificant, then between 5 mil and 4 mil is very significant, and 4 mil and 3 mil are different universes in terms of losses. (In general, in our opinion, the ideal topologies of a differential pair are 6-6-6 or 7-7-7).

Therefore, we prefer to form the stack so that its dependence on the characteristics of a particular PCB manufacturer is minimized. If you work with the same vendor, then it’s quite realistic to form a stack so that its modification by the manufacturer is not required at all. This is a saving of 1-2 weeks in preparation for production.

By the way offtopic.

Surely someone will want to ask - which is better, tightly coupled or loosely coupled differential pairs. Our opinion: better loosely coupled - they are easier to align in length. You can afford more serious bumps. There are no particular advantages of strongly coupled pairs over loosely coupled (if we do not consider strange topologies of type 5-14-5) from the point of view of SI in our opinion - no. For lovers of formal rules: one or two widths between conductors in a pair is normal. More - not so much. Less is difficult to align. Despite the fact that the EMC performance of strongly coupled pairs is much better, in absolute terms this “strongly” is not essential.

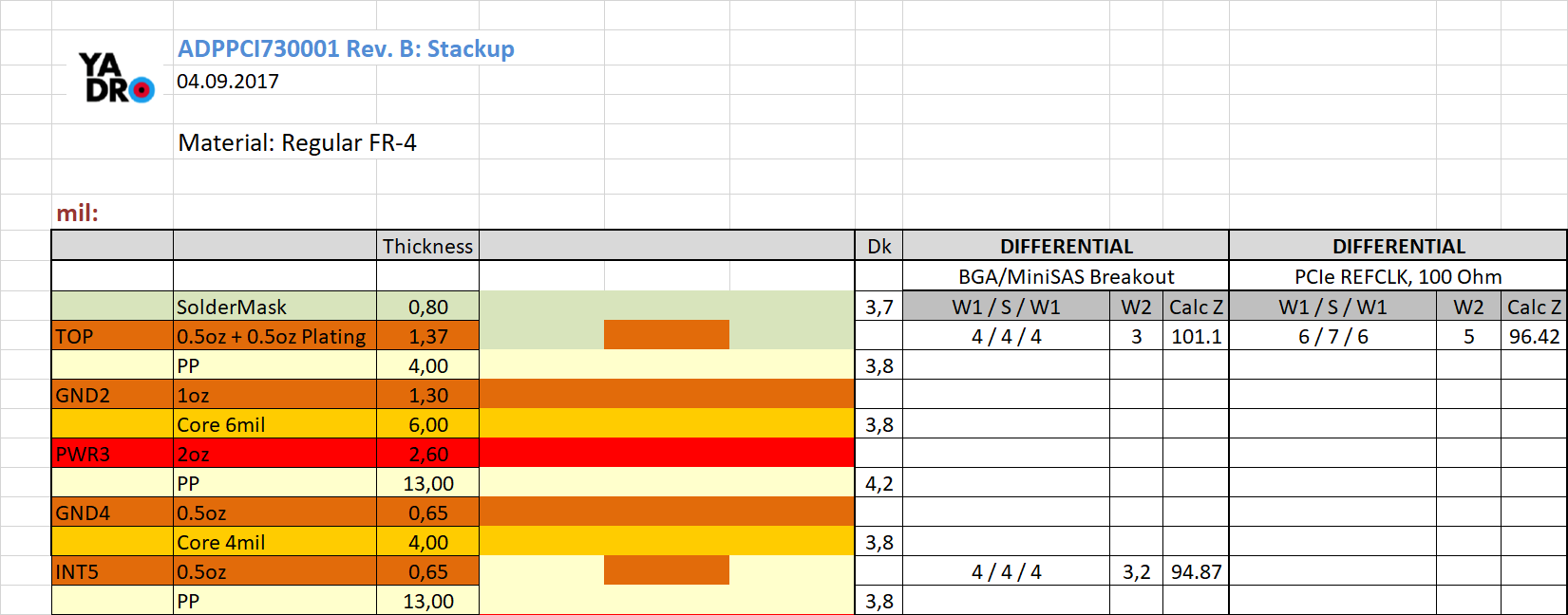

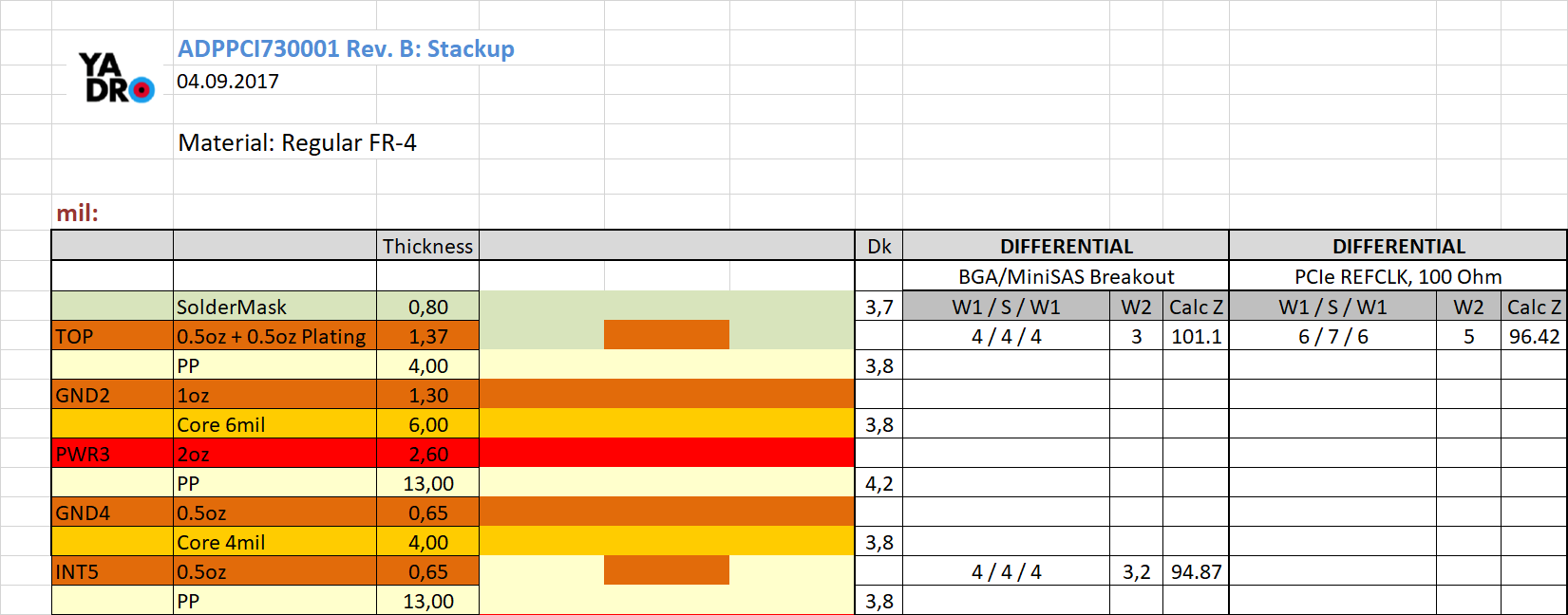

In order to more or less accurately form the stack of the printed circuit board - you need to know the parameters of specific cores and prepregs of the material used. The datasheets contain the averaged parameters for the entire group and are not suitable for accurate calculation. This information can be requested from both the material manufacturer and the PCB manufacturer. This is a table that looks like this (for each material manufacturer it has its own):

The thickness of different types of prepregs are usually the same for different manufacturers. Therefore, the information on the above image is relevant and usable without regard to the manufacturer of the material (Dk / Df, of course, everyone has different).

When designing a PCB stack, it is necessary to take into account that PCB manufacturers, as a rule, make a correction for lamination, reducing the dielectric constant (Dk) values of both prepregs and “cores” by about 0.2 relative to the values given in the documentation of the material manufacturer.

If Dk / Df values are given for different frequencies, it is recommended to use the values of these parameters for the frequency closest to the Nyquist frequency of the fastest interface on the PCB. For example, if PCI Express Gen3 is present in the PCB, then the Dk / Df values should be used for the frequency closest to 4 GHz.

Someone will argue: how, because the band of the same Gen3 extends right up to 18 GHz. This is true - but the PCIe specification regulates RL and IL before the Nyquist, and all these hellish gigahertzs do not pass through connectors, vias and the printed circuit board - will die out along the way. And if it passes, it’s a big question whether you will like the result.

In a situation where there are several different high-speed interfaces on the PCB — you should not use the Dk / Df values for different frequencies within the stack of one board. Although this approach is more accurate in terms of calculating the impedance, it will cause great difficulties in matching the stack with the PCB manufacturer (their test equipment is tuned to one specific frequency).

If the values of Dk / Df vary considerably with frequency, and impedance control is critical - it makes sense, having obtained the impedance values for the real interface frequency, recalculate it, taking Dk for some single frequency (the most critical interface). “Normalized” thus impedance value - specify as target for control by the PCB manufacturer.

For example, you make a calculation of the 100 Ohm trace for the 4 GHz frequency, use the Dk value for 4 GHz, and in accordance with the obtained data, perform the trace. Further, if you have, for example, interfaces requiring calculation for 10 GHz, substitute the value of Dk for a higher frequency into the initial calculation. Suppose that you get the impedance value of 105 Ohms. Our advice: here is 105 ohms and tell the PCB manufacturer to monitor. Do not fool him with different Dk for different frequencies on the same layer.

It also does not hurt to ask on the shore with what glass the fab works, so that there are no problems with delivery dates later. Because there are popular prepregs and not so much. Usually he always has 3-4 types in abundance, of which it is worth building a PCB stack. Low-loss materials are usually not in stock, due to the limited shelf life - therefore, the use of something special is always a question not so much of price, as of production time.

Accounting for changes in prepreg thickness during PCB manufacturing

The table below shows the absolute values of changes in the thickness of one prepreg layer for different conditions of use. The tolerance for all values is 10%.

| Conditions | Changing the thickness of the prepreg at the initial value | |

|---|---|---|

| No more than 2.3 mil | More than 2.3 mil | |

| Fit to copper 0.5 oz with 30% filling | 0.4 mil | 0.4 mil |

| Fit to copper 0.5 oz with 70% filling | 0.1 mil | 0.2 mil |

| Fit to copper 1 oz with 30% filling | 0.8 mil | 0.9 mil |

| Fit to copper 1 oz with 70% filling | 0.3 mil | 0.4 mil |

| Fit to copper 2 oz with 30% filling | 1.8 mil | 1.9 mil |

| Fit to copper 2 oz with 70% filling | 0.8 mil | 0.8 mil |

| Located between two prepreg layers | 9% | ten% |

| Fit to the outer layer | does not change | does not change |

To more accurately calculate the change in prepreg thickness, you can use the following expression:

In the case when there is one layer of prepreg between the metallization layers - the values of thickness changes for the corresponding conditions should be summed up, since the change in the thickness of the prepreg is actually an indentation of a conductive pattern into it.

When forming a PCB layered description, the finishing value of the prepreg should be indicated. At the same time, the portion of prepreg pressed into the metallization pattern should not be included in the value of the final thickness in the documentation sent to the PCB manufacturer.

Example

It is necessary to calculate the finishing thickness of the stack shown in the figure. Copper 1 oz is used on all plating layers. The initial prepreg thickness of 2116 is 5.1 mil.

The resulting stack will be:

| Layer type | Initial thickness | Thickness variation | Finishing thickness |

|---|---|---|---|

| External | 1.35 mil | - | 1.35 mil |

| Layer 2116 | 5.1 mil | - | 5.1 mil |

| Layer 2116 | 5.1 mill | 0.9 mil | 4.2 mil |

| Internal signal | 1.35 mil | - | 1.35 mil |

| Core | 39 mil | - | 39 mil |

| Inner Plane | 1.35 mil | - | 1.35 mil |

| Layer 2116 | 5.1 mil | 0.4 mil | 4.7 mil |

| Layer 2116 | 5.1 mil | - | 5.1 mil |

| External | 1.35 mil | - | 1.35 mil |

| Total: | 63.5 mil ± 10% |

Accounting Etch Factor

The expression for calculating the etch factor for the process of electrical copper deposition is shown in the figure:

The table shows the Etch Factor values for different types of plating for various manufacturers. As you can see, they are very different. Therefore, the EF value is the first thing you should check with your PCB partner.

| Layer type | Factory 1 | Factory 2 | Factory 3 | Factory 4 | ||||

|---|---|---|---|---|---|---|---|---|

| EF | W2-W1 | EF | W2-W1 | EF | W2-W1 | EF | W2-W1 | |

| External 0.5 oz | 3.4 - 4 | 1 mil | 3.4 - 4 | 1 mi | 3.4 - 2 | 1.5 mil | 2.6 | - |

| External 1 oz | - | - | - | - | 1.66 | 2.4 mil | 2.6 | - |

| Internal 0.5 oz | 1.75 | 0.8 mil | 4.33 | 0.3 mil | 1.73 | 1.75 mil | 3 | - |

| Internal 1 oz | 2.4 | 1 mil | 4.33 | 0.6 mil | 2.6 | 1 mil | 3 | - |

| Internal 2 oz | - | 1.5 - 2 mil | 4.33 | 1.2 mil | 2.6 | 2 mil | 3 | - |

| Internal 3 oz | - | - | - | - | 2.6 | 3 mil | 3 | - |

| Internal 4 oz | - | - | - | - | 2.3 | 4.5 mil | 3 | - |

For cases when information on the value of EF from a specific production is not available - we can assume that EF takes the following values:

- outer layers - 2.6

- inner layers - 3.7

Features of the calculation of the thickness of metallization

Metallization of outer layers

When calculating the metallization of the outer layers, the value of the thickness of copper weighing 1 oz, as a rule, is taken equal to 1.37 mil. It is recommended to separately set the weight of the base copper and the weight of the deposited copper. The total value is obtained by summing these two parameters. Typical values are shown in the table:

| Base copper | Plating copper | ||

|---|---|---|---|

| 0.7oz | 1oz | 2oz | |

| 0.5oz | 1.644 mil | 2.055 mil | 3.425 mil |

| 1oz | 2.329 mil | 2.74 mil | 4.11 mil |

| 2oz | 3.699 mil | 4.11 mil | 5.48 mil |

| 3oz | 5.069 mil | 5.48 mil | 6.85 mil |

Metallization of the inner layers

For the inner layers, the thickness value of copper weighing 1 oz, as a rule, is taken equal to 1.3 mil.

Accounting solder mask

When taking into account the solder mask based on the following scheme:

In cases where it is not explicitly stated otherwise, we can assume that the solder mask has the following parameters:

- Dk - 3.7

- Df - 0.025

- Thickness - 0.8 mil

Most manufacturers consider the values of C1, C2 and C3 equal to each other when considering the effect of the solder mask.

Some factories consider the values of C1 and C3 to be equal to the metallization thickness (T1), and C2 to 0.8 mil. The correctness of this approach is approximately confirmed by actual data obtained after the PCB production.

One of our PCB partners considers the solder mask thickness on solid sections of copper 0.79 - 1.18 mil, on the edges of conductors 0.2 mil. Also, this manufacturer recommends not including a solder mask when calculating the stack, since etching the outer layers results in the slightest overtravel (i.e. an increase in the impedance value), which is compensated by the mask in the face value of the theoretical impedance measurement of the outer layers without a mask.

This, by the way, is a good example of the fact that when working with this production - the thickness of the tracks on your PCB will be less than what is in the PCB pattern.

Results

These are our internal recommendations and rules with which we must necessarily introduce all the engineers who design printed circuit boards. I hope that this article will be useful to those who scour the expanses of the Internet in search of scattered recommendations and trying to guess how it will turn out in his particular product. I invite you to share your experience in the comments - we will be happy to add your own. If there is interest, I will lay out a few more similar internal instructions.

Source: https://habr.com/ru/post/338382/

All Articles