Excursion to the Museum of Computer History in California, with the benefit of the development. Part 1. ENIAC, Stretch, CDC6600, IBM / 360

Lord Today we will walk with a Siberian girl Irina on the Museum of the History of Computers in Mountain View, California. And let's go not as tourists, but for the benefit of Russia. I already wrote in a previous post that one of the most effective ways for a student to study processor design is to take some ancient, but instructive processor, find documentation on its architecture (and some information on its micro-architecture), and design an analogue of this processor in the language of the hardware description of SystemVerilog (or VHDL, if you like it more), then implement the processor on the FPGA / FPGA board (which one does not matter - Altera / Intel FPGA, Xilinx or Lattice). As a textbook for such an exercise, you can start with Harris & Harris , then continue with books for a more advanced stage of study, such as Shen-Lipasti .

How does all this benefit Russia? For such projects we are going to distribute FPGA boards at a conference to be held September 18-22 in Tomsk . There will arrive representatives of Moscow State University, MIPT, MIET, MCST, Imagination Technologies, National Instruments, etc. They will discuss how to update the university curriculum so that today's students in a few years can design Russian chips at the level of advanced western companies. There will also be a workshop where they will discuss how to make learning processors - starting from the simplest schoolMIPS from Stanislav Gelno sparf .

Here is the first photo from the museum in Mountain View - on it, besides Irina and the rocket, a small box is visible in the center. This is the on-board computer of the MIR space station , which was designed by the engineers of the Soviet association “ELAS”, which was transformed into the modern Zelenograd company “ELVIS” :

')

So, topics for educational projects - starting from the dense decades of the mid-20th century:

Before us is a block for storing a table of the results of calculating the arithmetic functions of a warm lamp computer ENIAC, developed in 1943-1947 by Presper Eckert and John Mauchly from the University of Pennsylvania. At some point, their colleague John von Neumann proposed using this block to store programs. This is how the “von Neman architecture” was born. In general, it would be correct to call it "Eckert-Mauchlie-von-Neumann architecture", but Eckert and Mauchly were not lucky - their names were kept secret, and von Neumann's name was not (the computer was intended to calculate artillery tables).

If you want to implement this computer on FPGA, I google ENIAC_Operating_Manual , although turning it into a code on the chain will be nontrivial:

IBM 7030 Stretch Transistor Supercomputer. The name (stretch - “stretch”) comes from the promises of its creators to make the computer 100 times faster than the previous IBM 704. Unfortunately, Stretch turned out only 30 times faster and the business community covered the creators with disgrace and contempt. However, in the process of this “failure”, the Aybiem engineers invented pipelining, multitasking, and memory protection:

CDC 6600 (1963). The first "real" supercomputer in history and the first processor with an extraordinary execution of instructions. Till nowadays, throughout the microarchitecture lectures (see, for example, the first sloughed (albeit not very fresh) slides on the CDC 6600 from Berkeley ), is used as an example of scoreboarding. The implementation of the simplified CDC 6600 on the chain and the FPGA is one of the most obvious candidates for a student course project.

Here is an excerpt about the overall organization of the CDC 6600 from the Microprocessor Architecture book: From the Multiprocessors by Jean-Loup Baer (2009). Several functional devices operating in parallel (but without a pipeline) and a scoreboard, tracking data dependencies between instructions, and suspending the execution of an instruction until its operands are ready:

IBM 360 (1964-1978). This line of computers made such a deep impression on the Central Committee of the CPSU of the USSR that, despite the resistance of the Soviet supercomputer authorities from ITMT (BESM and Elbrus), the IBM 360/370 Soviet implementations spread across all socialist countries under the name of the EU-computer. These computers are depicted even in the drawings of Soviet children of the Brezhnev era, “I am at my mother's work”:

In principle, it was for what - the IBM / 360 line introduced the concept of “unified architecture (command system) - various micro-architectural implementations (conveyor devices and hardware block structure) that was revolutionary for its time. In other words, the same software could work on slow, cheap, and on fast expensive computers of this line - without recompiling. (True, the software for these machines was not very friendly compared to the software on the mini-computers soon to emerge, but IBM hardware engineers were not to blame for this, it was the fault of the IBM programmers and their management).

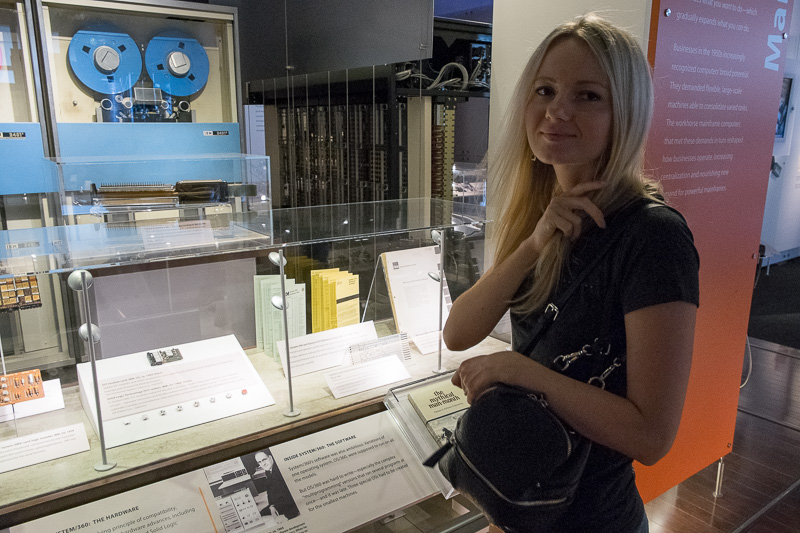

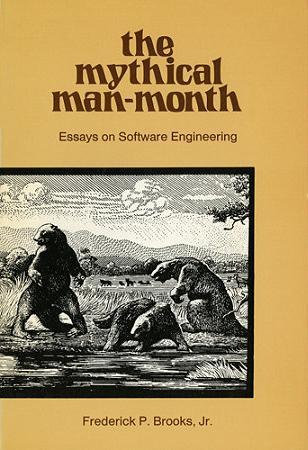

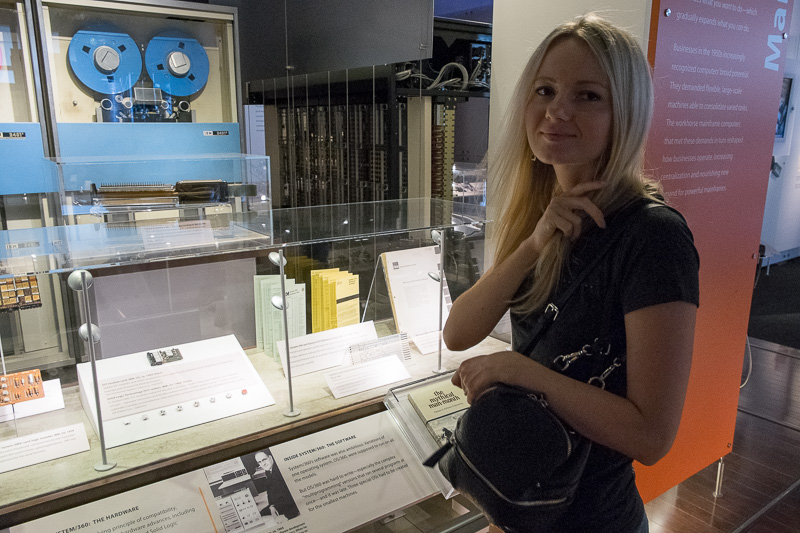

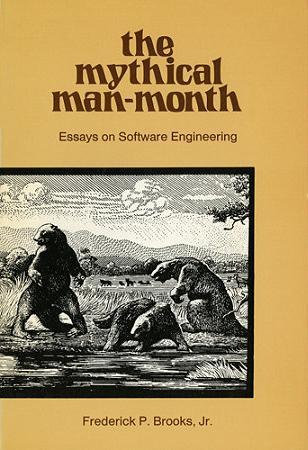

However, the IBM / 360 project has brought benefits to the programming world. Do you see the book “Mythical Man-Month” by Frederick Brooks to the left of Irina’s handbag? The author of the book is the project manager of OS / 360, who made the observation that trying to fix a broken deadline by adding new programmers to the project often leads to a worsening of the situation - the deadline will become even more broken. The book was published in 1975, immediately transferred to the USSR, and in some places it is still relevant:

Also, the IBM / 360 line introduced the concept of “microprogramming” and “microcode” into the mainstream, which became irrelevant in the process of the “RISC revolution” of the 1980s (modern microprocessors are mostly hardwired because of the need to pipe everything). However, these concepts are so firmly ate in Soviet and post-Soviet textbooks of computer architecture that people still ask the question “what is Verilog - this is microprogramming?” - after which it takes a long time to explain what it is _non microprogramming.

So why implement IBM / 360 on FPGA? It makes no sense to implement everything, but one aspect of one model, namely the IBM System / 360 Model 91, appears among modern student course projects in micro-architecture not less often than the CDC 6600 scoreboard. I’m talking about the so-called “Tomasulo algorithm”, the way of organizing extraordinary execution arithmetic operations with hardware "register renaming" and "redundancy blocks" (yes, these things are in the processors in your iPhones, these are not the remains of a mammoth). It is rather strange that there is no article on the Russian Wikipedia about the Tomasulo algorithm, although there is on the Ukrainian one:

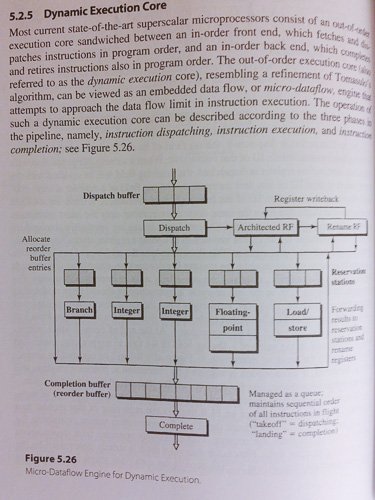

In one of the most useful modern books on the development of processors, Modern Processor Design: Fundamentals of Superscalar Processors by John Paul Shen and Mikko H. Lipasti (2013), clearly shows how a block of floating point operations looked like at IBM / 360-91 before improvement Tomasulo and after him. The same “before and after” can be done for the student project, with a comparison of performance (number of clock cycles on different sequences of operations) and maximum clock frequency (when implemented on an FPGA):

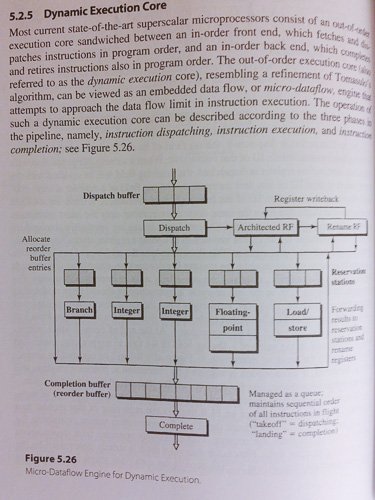

After this, the book of Shen-Lipasti describes how it is done in modern processors with a dynamic pipeline:

But the early transistor mainframe from Japan - NEAC 2203, made in 1958. He never sold outside of Japan. In general, then, the attitude towards Japanese goods in the world was frivolous, but Japanese companies suppressed idolatry of the West and engaged in capitalism in Japanese. At first, they ran into technological solutions in the domestic market (a kind of “import substitution”), and then aggressively attacked the world market. After a couple of decades, Japan ousted American companies from the market of memory chips and home electronics, and the same NEC built the most powerful supercomputer of 1992, the NEC SX-3/44. At the same time, voices began to appear in Japan about the need to reduce political dependence on the United States, and the Japanese transport minister wrote a book 「NO」 と 言 え る 日本 (“Japan can say“ NO ”!). Unfortunately, this rising from its knees was crippled by the subsequent economic crisis, but the Japanese experience of the 1950-1980s is interesting to study.

This concludes the first part of the walk through the museum. If you like the beginning, I can write more about Cray and Illiac supercomputers, HP, DEC and Data General mini-computers, first microprocessors and microcomputers, RISC-based workstations and Lisp-machines, game consoles and robots.

Now we recall for what all this:

If you are interested in open-source projects of this type to increase public education, you are ready to write them on SystemVerilog or VHDL, upload the code to GitHub and write articles about Habré (with performance analysis), but you do not have an FPGA board - you can borrow her (and get it permanently if the project is successful) in one of three places:

1. Alexander Romanov from MIEM HSE in Moscow. Alexander introduces Verilog courses for students, and he has a variegated collection of motherboards with Altera and Xilinx FPGA in addition to regular motherboards, both the frequently used Terasic and Digilent motherboards and the poorly documented Chinese motherboards are for open source projects.

2. Yaroslav Voznyuk from the Kiev-Mohyla Academy. I came to their hackathon for schoolchildren , and left there several Digilent Cmod A7 35T boards with Xilinx Artix-7 for barter „project fee with an article on Habré“.

3. Vladimir Makukha from Novosibirsk Technical State University. There is a set of boards for a weekly conference in Tomsk . Some of them (Digilent Nexys DDR4) will remain with Vladimir, some (Terasic DE0-CV) will go on such projects.

As an inspiration, you can look at existing projects with implemented on FPGA processors on Habré from SparF , Frantony , oleh_plotnikov , Kingit , VMSS , kirill90 , Boris_92 (you can add your own in the comments).

Ancient processors were made of radio tubes, transistors, microcircuits of a small degree of integration and drawing circuits with the mouse on the screen. Now this is not so. A few words for those readers who are not familiar with what Verilog, ASIC and FPGA are:

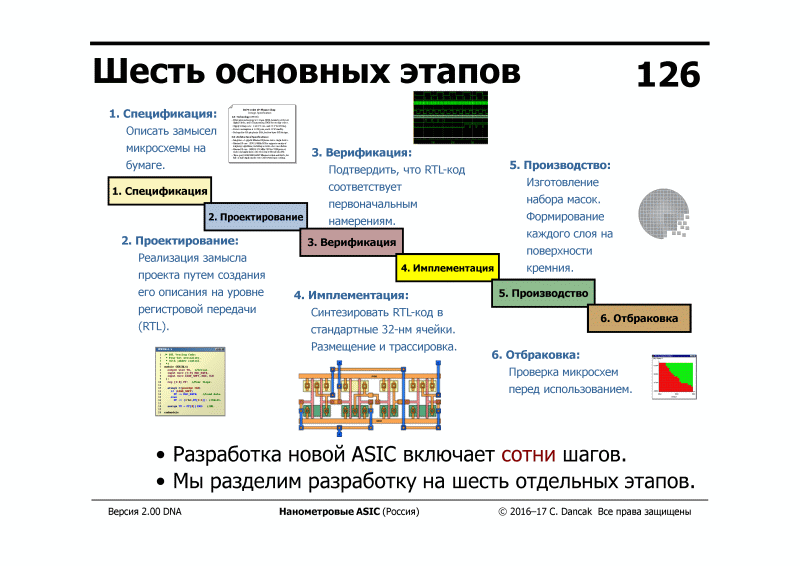

From a post on Geektimes » Armsmen of microelectronics. Video report from the San Francisco Electronics Design Conference :

From the post on Habrahabr How to start developing iron using FPGA - step by step instructions :

How does all this benefit Russia? For such projects we are going to distribute FPGA boards at a conference to be held September 18-22 in Tomsk . There will arrive representatives of Moscow State University, MIPT, MIET, MCST, Imagination Technologies, National Instruments, etc. They will discuss how to update the university curriculum so that today's students in a few years can design Russian chips at the level of advanced western companies. There will also be a workshop where they will discuss how to make learning processors - starting from the simplest schoolMIPS from Stanislav Gelno sparf .

Here is the first photo from the museum in Mountain View - on it, besides Irina and the rocket, a small box is visible in the center. This is the on-board computer of the MIR space station , which was designed by the engineers of the Soviet association “ELAS”, which was transformed into the modern Zelenograd company “ELVIS” :

')

So, topics for educational projects - starting from the dense decades of the mid-20th century:

Before us is a block for storing a table of the results of calculating the arithmetic functions of a warm lamp computer ENIAC, developed in 1943-1947 by Presper Eckert and John Mauchly from the University of Pennsylvania. At some point, their colleague John von Neumann proposed using this block to store programs. This is how the “von Neman architecture” was born. In general, it would be correct to call it "Eckert-Mauchlie-von-Neumann architecture", but Eckert and Mauchly were not lucky - their names were kept secret, and von Neumann's name was not (the computer was intended to calculate artillery tables).

If you want to implement this computer on FPGA, I google ENIAC_Operating_Manual , although turning it into a code on the chain will be nontrivial:

IBM 7030 Stretch Transistor Supercomputer. The name (stretch - “stretch”) comes from the promises of its creators to make the computer 100 times faster than the previous IBM 704. Unfortunately, Stretch turned out only 30 times faster and the business community covered the creators with disgrace and contempt. However, in the process of this “failure”, the Aybiem engineers invented pipelining, multitasking, and memory protection:

CDC 6600 (1963). The first "real" supercomputer in history and the first processor with an extraordinary execution of instructions. Till nowadays, throughout the microarchitecture lectures (see, for example, the first sloughed (albeit not very fresh) slides on the CDC 6600 from Berkeley ), is used as an example of scoreboarding. The implementation of the simplified CDC 6600 on the chain and the FPGA is one of the most obvious candidates for a student course project.

Here is an excerpt about the overall organization of the CDC 6600 from the Microprocessor Architecture book: From the Multiprocessors by Jean-Loup Baer (2009). Several functional devices operating in parallel (but without a pipeline) and a scoreboard, tracking data dependencies between instructions, and suspending the execution of an instruction until its operands are ready:

IBM 360 (1964-1978). This line of computers made such a deep impression on the Central Committee of the CPSU of the USSR that, despite the resistance of the Soviet supercomputer authorities from ITMT (BESM and Elbrus), the IBM 360/370 Soviet implementations spread across all socialist countries under the name of the EU-computer. These computers are depicted even in the drawings of Soviet children of the Brezhnev era, “I am at my mother's work”:

In principle, it was for what - the IBM / 360 line introduced the concept of “unified architecture (command system) - various micro-architectural implementations (conveyor devices and hardware block structure) that was revolutionary for its time. In other words, the same software could work on slow, cheap, and on fast expensive computers of this line - without recompiling. (True, the software for these machines was not very friendly compared to the software on the mini-computers soon to emerge, but IBM hardware engineers were not to blame for this, it was the fault of the IBM programmers and their management).

However, the IBM / 360 project has brought benefits to the programming world. Do you see the book “Mythical Man-Month” by Frederick Brooks to the left of Irina’s handbag? The author of the book is the project manager of OS / 360, who made the observation that trying to fix a broken deadline by adding new programmers to the project often leads to a worsening of the situation - the deadline will become even more broken. The book was published in 1975, immediately transferred to the USSR, and in some places it is still relevant:

Also, the IBM / 360 line introduced the concept of “microprogramming” and “microcode” into the mainstream, which became irrelevant in the process of the “RISC revolution” of the 1980s (modern microprocessors are mostly hardwired because of the need to pipe everything). However, these concepts are so firmly ate in Soviet and post-Soviet textbooks of computer architecture that people still ask the question “what is Verilog - this is microprogramming?” - after which it takes a long time to explain what it is _non microprogramming.

So why implement IBM / 360 on FPGA? It makes no sense to implement everything, but one aspect of one model, namely the IBM System / 360 Model 91, appears among modern student course projects in micro-architecture not less often than the CDC 6600 scoreboard. I’m talking about the so-called “Tomasulo algorithm”, the way of organizing extraordinary execution arithmetic operations with hardware "register renaming" and "redundancy blocks" (yes, these things are in the processors in your iPhones, these are not the remains of a mammoth). It is rather strange that there is no article on the Russian Wikipedia about the Tomasulo algorithm, although there is on the Ukrainian one:

Tomasulo algorithm - an algorithm Tse, yaky in vikoristovuєtsya komp'yuternіy arhіtekturі aparatno zabezpechennya for dinamіchnogo planuvannya teams yak peredbachaє pozachergove vikonannya, of metoyu efektivnosti vikoristannya funktsіonalnih blokіv CPU cycles. Algorithm by manufacturers of Robert Tomasulo in 1967, if he worked at IBM, first of all realizations in the IBM System / 360 Model 91 in blocks of operations with a broken log.

Headend innovations algorithm Tomasulo Je pereymenuvannya regіstrіv in aparatno zasobah blocks rezervuvannya [en] to vsіh funktsіonalnih blokіv, i spіlna tire danih (DES), for a synchronous yakіy obchislenі peredayutsya in usі blocks rezervuvannya, SSMSC mozhut machi needful therein.

In one of the most useful modern books on the development of processors, Modern Processor Design: Fundamentals of Superscalar Processors by John Paul Shen and Mikko H. Lipasti (2013), clearly shows how a block of floating point operations looked like at IBM / 360-91 before improvement Tomasulo and after him. The same “before and after” can be done for the student project, with a comparison of performance (number of clock cycles on different sequences of operations) and maximum clock frequency (when implemented on an FPGA):

After this, the book of Shen-Lipasti describes how it is done in modern processors with a dynamic pipeline:

But the early transistor mainframe from Japan - NEAC 2203, made in 1958. He never sold outside of Japan. In general, then, the attitude towards Japanese goods in the world was frivolous, but Japanese companies suppressed idolatry of the West and engaged in capitalism in Japanese. At first, they ran into technological solutions in the domestic market (a kind of “import substitution”), and then aggressively attacked the world market. After a couple of decades, Japan ousted American companies from the market of memory chips and home electronics, and the same NEC built the most powerful supercomputer of 1992, the NEC SX-3/44. At the same time, voices began to appear in Japan about the need to reduce political dependence on the United States, and the Japanese transport minister wrote a book 「NO」 と 言 え る 日本 (“Japan can say“ NO ”!). Unfortunately, this rising from its knees was crippled by the subsequent economic crisis, but the Japanese experience of the 1950-1980s is interesting to study.

This concludes the first part of the walk through the museum. If you like the beginning, I can write more about Cray and Illiac supercomputers, HP, DEC and Data General mini-computers, first microprocessors and microcomputers, RISC-based workstations and Lisp-machines, game consoles and robots.

Now we recall for what all this:

If you are interested in open-source projects of this type to increase public education, you are ready to write them on SystemVerilog or VHDL, upload the code to GitHub and write articles about Habré (with performance analysis), but you do not have an FPGA board - you can borrow her (and get it permanently if the project is successful) in one of three places:

1. Alexander Romanov from MIEM HSE in Moscow. Alexander introduces Verilog courses for students, and he has a variegated collection of motherboards with Altera and Xilinx FPGA in addition to regular motherboards, both the frequently used Terasic and Digilent motherboards and the poorly documented Chinese motherboards are for open source projects.

2. Yaroslav Voznyuk from the Kiev-Mohyla Academy. I came to their hackathon for schoolchildren , and left there several Digilent Cmod A7 35T boards with Xilinx Artix-7 for barter „project fee with an article on Habré“.

3. Vladimir Makukha from Novosibirsk Technical State University. There is a set of boards for a weekly conference in Tomsk . Some of them (Digilent Nexys DDR4) will remain with Vladimir, some (Terasic DE0-CV) will go on such projects.

As an inspiration, you can look at existing projects with implemented on FPGA processors on Habré from SparF , Frantony , oleh_plotnikov , Kingit , VMSS , kirill90 , Boris_92 (you can add your own in the comments).

Addition about the basics of modern processor design

Ancient processors were made of radio tubes, transistors, microcircuits of a small degree of integration and drawing circuits with the mouse on the screen. Now this is not so. A few words for those readers who are not familiar with what Verilog, ASIC and FPGA are:

From a post on Geektimes » Armsmen of microelectronics. Video report from the San Francisco Electronics Design Conference :

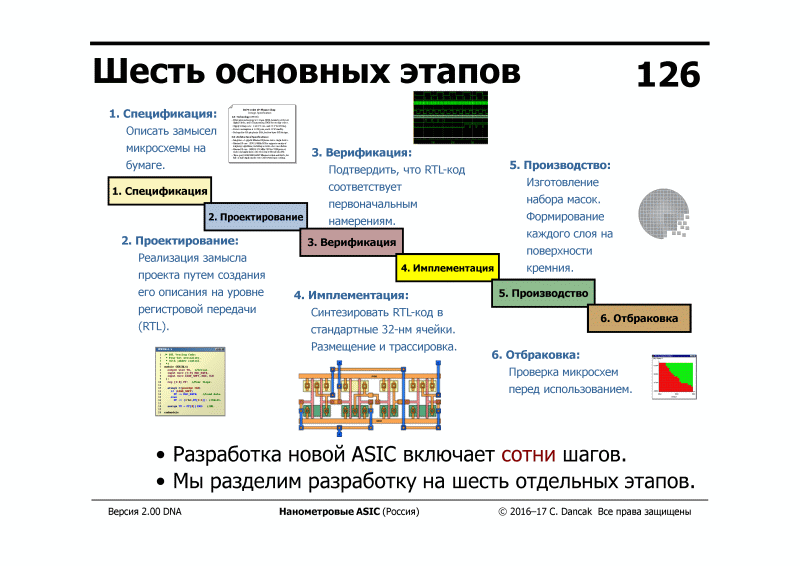

So far we have discussed the culmination of the microelectronic project - the manufacture of microchips in the factory. But how does such a project start?

In the past 25 years, chip design has most often been written in the Verilog hardware description language ([previously] in Europe and among the military - VHDL), after which a special program (logic synthesis) turns the design into a graph of wires and logical primitives, another program (static timing analysis) informs the designer whether it fits into the speed budget, and the third program (place-and-route) lays out this design on the chip site.

When the design goes through all the stages: coding on the chain, debugging, verification, synthesis, static timing analysis, floorplanning, place-n-route, parasitics extraction, etc. - it turns out a file called GDSII, which is sent to the factory, and the factory bakes chips. The most famous factories of this type are owned by Taiwan Semiconductor Manufacturing Company or TSMC.

From the post on Habrahabr How to start developing iron using FPGA - step by step instructions :

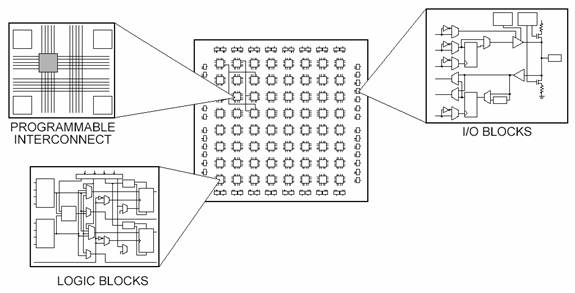

In its simplest form, an FPGA consists of a matrix of homogeneous cells, each function of which can be changed using multiplexers connected to the bits of the configuration memory. One cell can become AND gate with four inputs and one output, the other one single-bit register, etc. We load into the configuration memory a sequence of bits from the memory — and a predetermined electronic circuit is formed in the FPGA, which can be a processor, a display controller, etc.

FPGAs / FPGAs are not processors, “programming” the FPGAs (filling in the FPGA configuration memory) you create an electronic circuit (hardware), while programming a processor (fixed hardware) you slip a chain of sequential instructions written into the memory (software).

Source: https://habr.com/ru/post/337164/

All Articles