MIPSfpga - practical experience

Translation of the collective article Practical experiences based on MIPSfpga , not so long ago presented by Sarah Harris at a symposium in Toronto. A detailed description of MIPSfpga 2.0, which was released on July 3, 2017, is provided. The main difference, in my opinion, is compared to version 1.3: the lab package is expanded with a set that focuses on the internal operation of the processor. So, if you want to find out how the modern core works, then MIPSfpga 2.0 is your choice for high-quality self-education. This article will be extremely useful for university teachers - the issue of integrating MIPSfpga 2.0 into the educational process, including its compliance with the IEEE / ACM Methodological Guidelines for Undergraduate Computer Science Programs, is discussed in detail and with examples.

The article has a slight touch of marketing, but it seems to me that this does not diminish the merits of MIPSfpga 2.0, since there is nothing similar in depth, width of coverage and orientation of documentation on the educational process among open processor cores.

Among the authors of the article are David Harris and Sarah Harris - the authors of the popular textbook on digital circuit design and computer architecture, YuriPanchul - which is already known to the audience for its activity in promoting MIPSfpga and educational initiatives in the CIS countries. It is worth mentioning Robert Owen, who oversees the Imagination's University Program, and Zubair L. Kakakhel, who provided the addition of MIPSfpga support to the main branch of the Linux kernel (it was with its kernel code that I worked on when I started Linux on MIPSfpga-plus). Link to the original article: [ L1 ].

Practical experiences based on MIPSfpga

Authors: Daniel Chaver, Yuri Panchul, Enrique Sedano, David M. Harris, Robert Owen, Zubair L. Kakakhel, Bruce Ableidinger, Sarah L. Harris

The article discusses the use of the soft-microprocessor MIPSfpga when teaching computer architecture courses in the framework of undergraduate or graduate programs. Its latest version (MIPSfpga 2.0) consists of the following parts: a starter pack (MIPSfpga Getting Started Guide), a lab package (MIPSfpga Labs) and a system on a chip (MIPSfpga System on Chip). The article provides a brief description of them, examples of the integration of MIPSfpga into the curriculum, based on teaching experience at the Complutense University of Madrid, Darmstadt Technical University, as well as seminars held at universities and research centers in Russia. Access to MIPSfpga — the industrial core of the MIPS architecture, including the ability to research and modify it — allows students to bridge the gap between theory and practice.

1. Introduction

The MIPSfpga project is a comprehensive set of materials focused on teaching computer architecture and developed by Imagination Technologies. In addition to the source code of the MIPS microAptiv UP kernel, it includes training materials and development tools. Soft microprocessors have been used for several decades now, but MIPSfpga is the first commercial core available under an academic license, the codes of which were not obfuscated. This makes it possible to bridge the gap between existing educational programs built using “toy” cores of the MIPS architecture and real industrial MIPS processors and auxiliary tools.

The first version of MIPSfpga, which was released in June 2015, includes the Getting Started Guide, which, in addition to the source code of the microAptiv UP kernel, also contains a description of the processor, system on chip (SoC), debugging and development tools, and a set of scripts and examples. The following package (MIPSfpga Fundamentals) contains nine laboratory works that gradually teach students how to configure the equipment, programming, debugging, and connecting various peripheral devices to the processor core. And finally, the third packet (MIPSfpga-SoC) is a system on a chip, which shows how to get a complete solution running Linux, built around the MIPS core, interacting with memory (DDR), interfaces UART16550, I2C, Ethernet , interrupt controller.

In June 2017, the second version of the package (MIPSfpga 2.0) was released. As before, it consists of three parts: a starter pack (MIPSfpga Getting Started Guide, GSG), a set of labs (MIPSfpga Labs), which replaced the MIPSfpga Fundamentals pack, and a system on a chip (MIPSfpga System on Chip, SoC). Compared to the previous release, the GSG package has been supplemented with instructions on programming and debugging the kernel without using the Bus Blaster programmer, deploying the necessary software for working with MIPSfpga on computers running Windows and Linux, added a description of the top-level module of the MIPSfpga system in VHDL. The MIPSfpga Labs package includes 17 new labs that are focused on research and making changes to the core at the microarchitecture level. Among them: analysis and modification of cache structures and cache controller; adding user-defined instructions (UDI) through the CorExtend interface, using interrupts and direct memory access (DMA) for I / O operations; Shows how to make changes to the core MIPSfpga.

Section 2 of this article describes the packages included in MIPSfpga 2.0 (starter pack, lab suite, system-on-chip), as well as an analysis of how these materials comply with the IEEE / ACM Methodological Guidelines for Computer Science Bachelor's Programs (IEEE / ACM Curriculum Guidelines for Undergraduate Degree Programs in Computer Engineering) [ 1 ]. Section 3, using the example of three courses, shows how to integrate MIPSfpga into the curriculum. Section 4 describes projects similar to MIPSfpga, the conclusions are given in Section 5.

2. Review of MIPSfpga 2.0

The MIPSfpga project consists of three packages available on the resource [ 2 ] and discussed in sections 2.1-2.3. A more detailed description is given in [3]. These materials are in good agreement with theoretical concepts taught in the framework of computer architecture courses. Section 2.4 provides a brief description of the IEEE / ACM Methodological Guidelines for Undergraduate Computer Science Programs [ 1 ] and shows how the requirements of this document are covered by MIPSfpga 2.0.

2.1. Starter Pack (MIPSfpga Getting Started Guide, GSG)

The first package in question is GSG, which includes non-fuscated source codes of the MIPS processor, which is specifically targeted for deployment to the FPGA. This soft microprocessor is a version of the microAptiv UP kernel, which, in particular, is used in the popular Microchip PIC32MZ microcontroller. It is a set of files (in the Verilog language) containing a description of the processor with a 5-step pipeline and the MIPS32r3 instruction set [ 4 ]. The package also includes tools for development and debugging (Codescape MIPS SDK Essentials and OpenOCD), a description of the MIPSfpga core and system built on its base, a guide to using MIPSfpga and software tools, a set of scripts and examples ( note the translator: the GSG includes a project SoC, sufficient to run bare metal code. More complex SoC, focused on launching Linux, is presented in the MIPSfpga-SoC package .

Figure 1. The MIPSfpga system

The MIPSfpga system shown in Figure 1 consists of a kernel (MIPS Core) and peripheral devices that are connected to it using the AHB-Lite bus. Peripherals include memory (in this case, block RAM), and general purpose input / output interface (GPIO), which provides access to the LEDs and switches on the FPGA debug board. Considering the fact that many universities use Verilog or VHDL in training courses, the top-level module MIPSfpga 2.0 is present in two versions - for each of the listed languages.

To work with MIPSfpga, a debug board with FPGA and a BusBlaster programmer (debugger) are needed (translator's note: you can use a more accessible debugger, see [ L2 ]). Despite the fact that in the examples above, only Nexys4 DDR and DE2-115 are considered, the documentation contains detailed instructions for those who need to port the MIPSfpga system to debugging boards with more modest features (such as Basys3 or DE0). In addition, the manual describes the steps for downloading, installing and using the tools necessary for working with MIPSfpga, including simulation and synthesis tools (Vivado or Quartus II) necessary for configuring FPGAs, as well as development tools. For their work, you need a computer running Windows or Linux.

It is worth noting that a partnership agreement has been concluded between Europractice and MOSIS projects, within which academic and research centers are offered access to the MIPS core for its use in the production of Multi Project Wafer (MPW) - up to 100 sites. This agreement covers Warrior M-class 5100 and 5150 cores. This class is an extension of the microAptiv family, focused on Internet of Things solutions, wearable devices and other embedded applications. Thus, researchers gain access to the evolutionary latest version of the same core used in the MIPSfpga. These cores are offered in full configuration, including a floating point computing unit (FPU), a DSP, a microMIPS instruction set, and a hardware virtualization unit needed for solutions with special security requirements. All this allows MIPSfpga to be positioned as a comprehensive educational solution that can be used both as part of computer architecture courses and in teaching more complex sections of the master's program, including the possibility to implement the final solution in silicon available for research projects.

2.2. Laboratory work (MIPSfpga Labs)

The second of the MIPSfpga packages is intended for practical classes in computer architecture and on-chip system design based on the SoC project, which is part of the GSG. To successfully complete the laboratory work, students need basic knowledge in terms of digital circuitry, computer architecture, and the MIPS instruction set (ISA) [ 5 ]. Software development experience will be useful in this case, but is not mandatory, since necessary things can be mastered in the course of work.

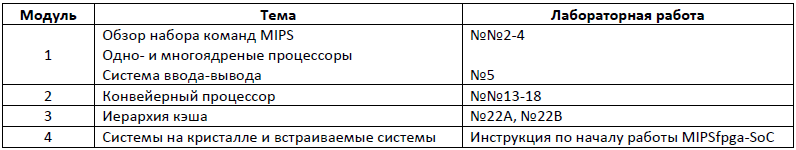

The package includes 25 laboratory works that allow the student to go through the initial MIPSfpga system configuration procedures, to study the complex interactions that occur within the core and the system based on it. Laboratory work can be divided into 4 parts: introductory, input-output, micro-architecture, memory. The introductory laboratory work (No. 1-4) shows how to deploy, program, and debug the MIPSfpga system. On the example of works devoted to input-output (No. 5-13), the procedure for connecting new peripheral devices to the system is explained. The third group of laboratory works (No. 14-19) immerses the student in the details of the micro-architecture of the microAptiv processor core - the heart of MIPSfpga. And finally, the last set (No. 20-25) is devoted to research and making changes to the memory hierarchy. Table 1 contains a list of laboratory work, a more detailed description of which is given below.

Table 1. MIPSfpga Lab Works

The first part (introductory) consists of 4 laboratory work, which introduces the tools needed to work with MIPSfpga. In work # 1, the project builds the MIPSfpga for a specific FPGA using Vilado's Xilinx software or Quartus II software from Altera ( note of the translator: now Intel ), the example of the Basys3 and DE0 boards shows how to deploy MIPSfpga on various debug boards. Works №2.3 explain the procedure for using the Codescape SDK (contains the gcc and gdb MIPS assemblies) and the Bus Blaster hardware debugger for compiling C programs and assembler, loading them into memory and then running and debugging on the FPGA. Work number 4 contains a set of additional practical task of programming.

The second part begins with 5 papers on interaction with memory-mapped I / O devices. As they are executed, the MIPSfpga system interacts with increasingly complex peripherals: a 7-segment indicator, a millisecond time counter, a sound emitter for music playback, two devices with an SPI interface (LCD and a light sensor). For works No. 7-9, additional components are needed, as described in [3].

The works №10-12 deal with more complex topics, such as interrupts and direct memory access (DMA). The basic principles of using interrupts in MIPS processors are explained in reference 10. It also demonstrates how interrupts help avoid periodic interrogation of peripheral devices, freeing up processor time for calculations or other tasks not related to I / O. In the following papers, analysis, design, construction and testing of a direct memory access module (No. 11) and an encryption module according to the DES standard (No. 11) are considered. And finally, in work No. 13, the practical example explains how to configure and use performance counters available in the microAptiv cores. There are several exercises to evaluate the performance of the program, involving the use of counters and various types of events. This mechanism is also used to assess the effectiveness of programs in the works №14-25.

In the third part of the laboratory work, immersion into the inner workings of the core is performed: the use of certain microAptiv features, the CorExtend interface is shown, the operation of the pipeline when executing instructions is described in detail. The first 4 papers (No. 14-17) are devoted to the work of the internal components of the microAptiv core and its pipeline. Learn how ADD, AND, LW and BEQ instructions are processed. First, the stages of the microAptiv pipeline are described and show how the decoded instruction passes through each of them. After that, during a step-by-step simulation, with reference to the Verilog code, the main signals related to the processing of instruction data are shown. And finally, the trainees are assigned to analyze individual control signals, explore additional instructions, add new instructions to the set of supported microAptiv commands.

In work No. 18, the work of the conflict resolution unit (Hazard Unit) is explained and shown. It also introduces the use of a clock divider with which the system can operate in the frequency range from a few MHz to 1 Hz. By reducing the clock frequency and connecting the control signals of the processor core (pipeline, conflict resolution block, cache extrusion signals) to the LEDs of the debug board, users are able to study the program behavior in real time.

The last of the works in this part (# 19) is devoted to using the CorExtend interface, which is available in MIPS processors. It is a powerful tool allowing you to declare and implement User Defined Instruction (UDI). Using CorExtend, a user can, by connecting a specialized hardware module to the processor core, increase the speed of execution of critical sections of the algorithm compared to what can be achieved using the standard MIPS32 command set. The paper describes the features of the CorExtend interface, its capabilities, limitations, module placement inside the processor core, temporal characteristics, interaction of the user command block with the microAptiv pipeline, several practical exercises of the experimental plan are provided.

In the last group of laboratory works, the MIPSfpga memory system is investigated, starting with the cache (No. 20-24) and ending with the implementation of the internal (sverhperativnoy) instruction memory (Scratchpad RAM, No. 25). The analysis of the MIPSfpga memory system begins with a demonstration of hits and cache misses on the example of several programs with the output of the corresponding information on the LED (No. 20).

In work No. 21, various types of arrays are analyzed that make up the cache used by the kernel (Data, Tag and Way Select arrays). The paper describes both the cache interface and its implementation. After a detailed explanation, students receive the task to implement and test a new cache configuration, as well as to try out several approaches to code optimization using performance counters.

The following three labs are dedicated to the implementation of the cache controller. In the work №22 analyzes the management of hits and misses, describes the main stages, structures and signals involved in the event hit or miss. All this is illustrated using simulation. Finally, exercises are proposed for examining the caching system, for example, by estimating the overhead costs (miss penalty) associated with the cache miss. Job 23 describes cache management policies supported by the microAptiv UP kernel. The trainees are tasked with evaluating various write policies and allocation lines of the cache (allocation policy), as well as implementing new replacement policies. And, finally, in work No. 24, the operation of the store buffer (Store Buffer) is explained, which temporarily stores data until it is written to the data porridge. And a fill buffer (Fill Buffer) containing a block that should be placed in the data cache after a slip.

Finally, in work No. 25 it is shown how to add in-memory instruction memory (Instruction Scratchpad RAM) to MIPSfpga. In the basic configuration of MIPSfpga there is a corresponding interface, but there is no implementation of this module. This lab shows how to add super-fast memory to the system and interact with it via the instruction / data cache controller.

Having completed the labs, the trainees are ready to develop more complex projects, such as adding support for new peripheral devices (for example, I2C or UART), new features to the processor core (hardware prefetcher or transition predictor) or memory system (second level cache or way predictor), or any other tasks to choose a teacher.

2.3. System on Chip (MIPSfpga-SoC)

The last of the MIPSfpga 2.0 packages demonstrates how to build a chip-based system based on the Linux operating system, an open source operating system, based on the processor core. A detailed (level-by-level) description of the SoC device (as an element of the embedded system) is provided, which ensures the execution of complex programs.

The Linux-based SoC is built on the basis of the MIPS processor core controlling the peripheral devices via the AHB-Lite bus. On the bus, the processor is the master device, and the peripheral modules are the slaves. Xilinx-specific IP cores are used as peripheral devices, which significantly reduces system development time. (Translator's note: and also makes it impossible to launch the original MIPSfpga-SoC on FPGAs from other manufacturers. The way out of this situation is MIPSfpga-plus [ L3 ] - a similar SoC project, but with platform-independent peripherals). All peripheral devices are connected to the processor core via the AHB-Lite bus with the device mapping into memory (memory-mapped I / O). Due to the fact that Xilinx peripheral modules are controlled via the AXI (Advanced eXtensible Interface) bus, the appropriate interface converter (bridge) “AHB-Lite to AXI” is included in the system (between the processor and the periphery). Of all the SoC devices, only the processor core and the GPIO module are provided by Imagination Technologies, the rest of the peripherals are Xilinx IP modules. A simple GPIO-module allows the example of the interaction of the processor core with buttons and LEDs to understand the construction and connection of the peripheral device.

Figure 2. Simplified structure of SoC running Linux

The Linux operating system can be divided into two parts: user space (Linux Userspace) and kernel (Linux Kernel). Applications in user space interact with hardware using a standard set of kernel-supplied system calls. To build the user space MIPSfpga-SoC, the Buildroot software package is used, which is characterized by great scaling capabilities. The kernel interacts with the hardware and provides a level of abstraction. To run the Linux kernel in the SoC, at least the following requirements must be met: a processor with MMU support, an interrupt controller, a timer interrupt, a UART interface, a memory, an EJTAG interface. Note that all of the above is present in the system shown in Figure 2.

In addition, the MIPSfpga-SoC includes a set of patches for Linux, which add system support to the OS kernel. Since the microAptiv UP processor core and peripheral modules are already supported by the core, the code already present in it is used and only the description of the MIPSfpga-SoC platform is added. In order to run Buildroot on the SoC core, it is built under the mips32r2 architecture. As a result, we get a system on which you can run applications using standard GNU C libraries.

2.4. IEEE / ACM guidelines for undergraduate computer science programs

The list of blocks (training topics) related to the field of knowledge. Computer architecture and IEEE / ACM Methodological Recommendations for undergraduate computer engineering programs are given in Table 2.

Table 2. Blocks in accordance with the IEEE Guidelines

MIPSfpga laboratory work provides a wide coverage of these blocks. Appeared in the early 80s, the MIPS architecture identified many solutions that were used in later architectures. Therefore, it plays a key role in the history of the development of the architecture of computing systems and corresponds to the subject of the CE-CAO-1 block. Laboratory works №2-3 involve the creation of projects in Vivado, compiling, running and debugging programs, which corresponds to the block CE-CAO-2. The topic of performance measurement (CE-CAO-4) is addressed in laboratory work No. 13 when working with performance counters. Which are used to assess the impact of various events and combinations of executed instructions on the performance of the kernel and its elements. In addition, performance counters are involved in laboratory work No. 14-25. In work No. 14, in particular, the execution of the ADD command and other arithmetic instructions is studied, which corresponds to the theme CE-CAO-5.

The processor architecture (CE-CAO-6) is studied in laboratory works No. 14-18, which, as noted earlier, consider the structure of the MIPS pipeline. In works No. 20-25, an exhaustive overview of the memory hierarchy is presented, including caches, super-operative memory, which covers the CE-CAO-7 block to a sufficient extent. The topics of CE-CAO-8 and CE-CAO-9 are devoted to work No. 5-20, which deals with the connection of various input-output devices to the MIPSfpga system, interaction based on interrupt processing, data transfer using direct memory access, and encryption.

Due to the fact that MIPSfpga is a single-core system, the last two thematic blocks devoted to multi-core and distributed systems (CE-CAO-10 and CE-CAO-11) are not reflected in the materials. However, more complex systems can be built on the basis of MIPSfpga, since It is open for academic use. As an example, the authors of [ 6 ], by introducing large-scale changes to the MIPSfpga code, developed a 120-core system, which was deployed on a Terasic DE5-NET FPGA debugging board.

3. Practical experience using MIPSfpga

MIPSfpga 2.0 has already been used for reading courses, conducting seminars and hackathons. This chapter provides three examples for integrating MIPSfpga into the educational process, as well as some additional examples of using the system. In all cases considered, MIPSfpga is used to teach computer architecture courses and system design on a chip.

3.1. University of Complutense de Madrid

During the second semester of the 2016/2017 academic year (from February to June 2017), MIPSfpga 2.0 was used at Complutense University of Madrid as part of the teaching course on Computer Architecture and Embedded Systems - a subject that is required for obtaining an engineering degree in communication systems and taught in the fourth year of study. Students of this course demonstrate a strong basic knowledge of digital circuitry, VHDL, computer architecture (MIPS instruction set, single and multi-core processors, I / O subsystem) and programming (C ++). Below is a description of this course, laboratory work, evaluation criteria, as well as feedback from students.

3.1.1. Course Description

The 12-week course consists of 24 one and a half hour lectures (2 per week) divided into 4 modules. Module 1 is devoted to the materials that have been studied previously: the MIPS instruction set, single- and multi-core processors, an input / output system. In module 2, the MIPS processor pipeline is examined, its implementation is studied using examples and tasks. Module number 3 is devoted to the cache hierarchy, and number 4 is an introduction to systems on a chip and embedded systems. MIPSfpga 2.0 is ideal for this course.

The main textbook is used [ 5 ] with an emphasis on chapters 4 (hardware description languages), 6 (Architecture), 7 (Microarchitecture) and 8 (Memory and I / O system). Moreover, book-going slides are used, which were refined in order to link MIPSfpga and the theory under study: materials on MIPSfpga were added, as well as a comparison of MIPSfpga (Figure 1) and the conveyor implementation of the processor core, memory and I / O systems given in [ 5 ].

3.1.2. Workshops

Practical exercises alternate with 24 hour and a half lectures (translator's note: in order not to create confusion here and hereinafter, Laboratory work is understood to be part of the MIPSfpga package, and the practical lesson is work that is supposed to be conducted in accordance with the course of a particular university). The course involves 12 weekly practical exercises, 2 hours each. , MIPSfpga 25 , , : №№1-5, 13-18, 22 ( 1). , MIPSfpga-SoC. 3 :

3.

4. , . №2 MIPS, №4 – , – №6 №9 . , №1, Nexys4 DDR Bus Blaster. MIPSfpga GSG c [ 2 ], ( , Windows — B D, Linux – G). , ( 4.1, 4.2.1 7.4 – Windows, 4 G – Linux). Verilog ( 4 [ 5 ]), .. VHDL.

4.

1-2 . , №13 №6 №7: №6, () №6 №7. (№7) , .

№№14-18 3-4 . 5 5 1 . 30 .

, , . 60% ( №№13-17) .

3.1.3.

: 0.5 FE + 0.3 LM + 0.2*TM, FE – , LM – , ( 4), TM – .

3.1.4.

, (P. Fernandez, M. Sanchez, G. Diaz-Tejeiro, C. Oliver, J. Alvaro, A. Villarin, M. Cereceda, M. Perez, A. Dorda, PM Teba, FJ Oliva, EI Quezada, D. Fernandez, JA Canadas, A. Menendez, J. Martin, I. Diaz) . : «, , » (G. Diaz-Tejeiro); « , » (M. Sanchez); « » (J. Martin); « . , , , , , , - . -, » (A. Menendez). « , » (P. Fernandez). « » (A. Villarin).

3.2.

2015/2016 (TUD) « -, ». 14- ( ). 5 . [ 5 ]. (№№4-8) MIPSfpga ( 1).

5.

6 7 [ 5 ] MIPS . , MIPSfpga. №4 (MIPSfpga. ) №№1-3 ( 1). MIPSfpga №7, 9, 11 12 .

1-3 MIPS, , . MIPSfpga, – . 4 : - ; - (LCD); (DMA) AHB-Lite; DES. – . , .

(FPGA Nexys4 DDR, Bus Blaster, , -, ). ( GSG). 2-4 , , . , . 42 .

3.3. ,

2015-2016 , MIPSfpga , : «», . . , «», , , - , , ( . – ), «». , MIPSfpga : Microchip Masters Russia, , SECR, Nanometer ASIC «». . , , . ASIC, - , , .

2015 , MIPSfpga , , . MIPSfpga ( , MIPS [ 5 ]) , , , (stalls) (forwarding). MIPSfpga , , , , , . ( , ), , HDL. , , MIPSfpga EDA . , , MIPSfpga 2.0. : ( 1 ), USB-UART , Bus Blaster, , CorExtend.

2016 . MIPSfpga HDL — . Nanometer ASIC MIPSfpga , ASIC MIPS M5150 ( MIPS microAptiv UP , Europractice). , , [ 8 ], MIPSfpga , SPI, I2C . : RTL- .

, MIPSfpga. , CorExtend ([ 9 ] , . ). MIPSfpga : SDRAM; ; Visual Studio Code ; UART16550 Linux Terasic DE10-Lite ( . : MIPSfpga MIPSfpga-plus [ L3 ], , [ L4 ]-[ L13 ] ). NGC-17 , MIPSfpga Wishbone () VGA- ( -- ). , , , .

4.

soft- , . MIPSfpga 2.0

4.1. soft-

Xilinx Altera soft- Nios/Nios II [ 10 ] MicroBlaze [ 11 ] , . : , , / , , . ARM c : Cortex M0 Design Start [ 12 ] – (8K gates). , EJTAG . . .

. OpenSPARC [ 13 ] ( Oracle Sun Microsystems) LEON [ 14 ] ( Aeroflex Gaisler ). , , , (SPARC RISC) MIPS. : RISC-V [ 15 ], , openRISC, opencores.org [ 16 ]. , .

, MIPSfpga . , , PIC32MZ Microchip. (MIPS32r3) . MIPSfpga , . , , . MIPSfpga , Xilinx, Altera .

4.2.

[17] HIP- ( .: Hypothetical processor ), . 5- soft-, MIPS-. , , , . 52 , MIPS32r3, MIPSfpga. , , , . , MIPSfpga , , .

[18] BZK.SAU — . 59 . , , . , , , « ».

CNP, [19], , . MinIPS – , MIPS. — Tiny C. , MIPSfpga , MIPSfpga .

The MIPS32r3 instruction set is widely known and well documented, so the teacher can implement his own compiler or choose one of the existing and supporting MIPS, such as: Codescape MIPS SDK, gcc, or LLVM. In addition, the example of the MIPSfpga-SoC package shows that connecting to the MIPSfpga core of the Ethernet controller is a completely realizable task.

Finally, in [20], a course on advanced multi-core architecture is presented. This course goes beyond the original MIPSfpga framework, but, as mentioned earlier, teachers can adapt the MIPSfpga GSG to their needs, as shown in [ 6 ].

4.3. findings

This article presents an analysis of the latest version of MIPSfpga, released in June 2017 and its application for seminars and training courses. As shown in this publication, the MIPSfpga learning infrastructure is ideally suited to the topics taught in computer architecture courses. Moreover, when using MIPSfpga in the learning process, students face problems similar to those that a design engineer must solve.

Among them we can mention: the integration of peripheral devices in the SoC, the addition of new instructions, both using a standard interface (such as CorExtend), and by introducing changes to a commercial core (such as microAptiv); evaluating various cache configurations and policies using performance counters; building a complete SoC based on the commercial core and Xilinx peripheral modules with the launch of Linux OS. A simplified approach to learning (for example, presented in [ 5 ] and based on a highly primitive core) is perhaps more suitable for elementary undergraduate courses. At the same time, the transition to the use of industrial-level solutions in teaching has an advantage, since the problems solved at the same time are very close to those that students will face in the real world. What makes MIPSfpga the perfect solution for senior undergraduate and graduate education.

5. Thanks

The authors would like to thank the following individuals and organizations for their contribution to the Imagination University Program: the University of Nevada, Las Vegas, the Imperial College of the United Kingdom, the United Kingdom; R and TIN2015-65316-P, Munir Hasan (IMG UK), Prashant Deokar (IMG India), Mahesh Firke (IMG India) Parimal Patel (Xilinx), Kent Brinkley (IMG USA), Rick Leatherman (IMG USA), Chuck Swartley (IMG USA), Sean Raby (IMG UK), Michio Abe (IMG Japan), Bingli Wang (IMG China), Sachin Sundar (IMG USA), Alex Wong (Digilent Inc.), Matthew Fortune (IMG UK), Jeffrey Deans (IMG UK), Laurence Keung (IMG UK), Roy Kravitz (Portland State University), Dennis Pinto (UCM), Tejaswini Angel (Portland State University), Christian White, Gibson Fahnestock, Jason Wong, Cathal McCabe (Xilinx), and Larissa Swanland (Digilent)

6. References

[1] CE2016 - Curriculum Guidelines for Undergraduate Degree Programs in Computer Engineering. IEEE and ACM, 2016

[2] Imagination University Program - Resources

[3] Harris, S., Harris, D., Chaver, D., et al .: “MIPSfpga: Using a Commercial MIPS Soft-Core in Computer Architecture Education.” IET Circuits, Devices and Systems, 2017.

[4] Imagination Technologies Ltd., "MIPS32 microAptiv UP Processor Core Family Datasheet", July 31, 2013

[5] Harris, D., and Harris, S., "Digital Design and Computer Architecture" (Elsevier Science and Technology, 2007, 2nd edn. 2012)

[6] Kumar HB, C., Ravi, P., Modi, G., Kapre, N ..: "120-core microAptiv MIPS Overlay for the Terasic DE5-NET FPGA board", Int. Symp. On Field-Programmable Gate Arrays, Monterey, USA, February 2017

[7] Intro HDL design

[8] NTUU Hackathon

[9] CorExtend Interface

[10] Altera - NIOS-II Processor , February 2017

[11] Xilinx - MicroBlaze Soft Processor Core , accessed February 2017

[12] ARM - Cortex M0 Design Start , accessed February 2017

[13] Oracle - OpenSPARC , Feb-2017

[14] Aeroflex Gaisler - LEON series Softcores , accessed February 2017

[15] Waterman, A., Lee, Y., Patterson, DA, et al., “The RISC-V Instruction Set Manual, Volume I: User-Level ISA”, version 2.0, 2014

[16] OpenCores OpenRISC , accessed February 2017

[17] Buli´c, P., Guˇstin, V., Sonc, D., and Strancar, A,.: "An FPGA-based integrated environment for computer architecture", Computer Applications in Engineering Education, 2013, 21, (1), pp. 26-35

[18] Oztekin, H., Temurtas, F., Gulbag, A .: "BZK.SAU: Implementing a hardware and software-based computer simulator for educational purpose". Proc. 2nd int. Conf. Computer Design and Applications, Qinhuangdao, China, June 2010, pp. 490-497

[19] Abe, K., Tateoka, T., Suzuki, M., Maeda, Y., Kono, K., Watanabe, T .: "An integrated laboratory for the processor, compiler design and computer networking", IEEE Trans . Education, 2004, 47, (3)

[20] Petit, S., Sahuquillo, et. al: "Research and Development of Advanced Multicore Architecture: Contents and Active Learning Methodologies", Journal of Parallel and Distributed Computing, Elsevier, 2017

Additional links

[L2] MIPSfpga and in-circuit debugging

[L3] MIPSfpga-plus project

[L4] MIPSfpga and SDRAM

[L5] MIPSfpga and interrupts

[L6] MIPSfpga and UART

[L7] Current activity around MIPSfpga and not only

[L8] We are raising Linux on MIPSfpga and Altera FPGA

[L9] Porting MIPSfpga to other cards and integrating peripherals into the system

[L10] Connection of peripheral modules to MIPSfpga, using the example of the Pmod KYPD keyboard

[L11] Connection of peripheral modules to MIPSfpga, by the example of ultrasonic distance sensors

[L12] MIPSfpga: outside of canon

[L13] How to start working with MIPSfpga

')

Source: https://habr.com/ru/post/335848/

All Articles