We raise Linux on MIPSfpga and Altera FPGA

The documentation provided by Imagination Technologies on MIPSfpga describes very well the Linux deployment in great detail. But the system used on the chip is built using Xilinx-specific peripheral modules. Therefore, its repetition on the debug board with Altera FPGA in its original form is impossible. The solution is a system on a MIPSfpga-plus chip with its platform-independent peripherals. How to run Linux on it, read in this article.

Introduction

Immediately, we note that the configuration obtained as a result of the actions described below is far from ideal. At the moment there is no boot from external media, and only UART and GPIO can be mentioned among supported devices. Therefore, the front of further work on the development of the MIPSfpga-plus system is very broad.

Further it is assumed that the reader:

- familiar with the subject area in the Harris-Harris volume [ L1 ];

- has access to the source codes MIPSfpga [ L2 ] and mipsfpga-plus [ L3 ];

- set up and tested the operation of MIPSfpga-plus with SDRAM [ L5 ] and UART [ L6 ], as well as in remote debugging mode [ L4 ];

- has some skills in using Linux development tools, experience with git;

In the described case, the following configuration is used:

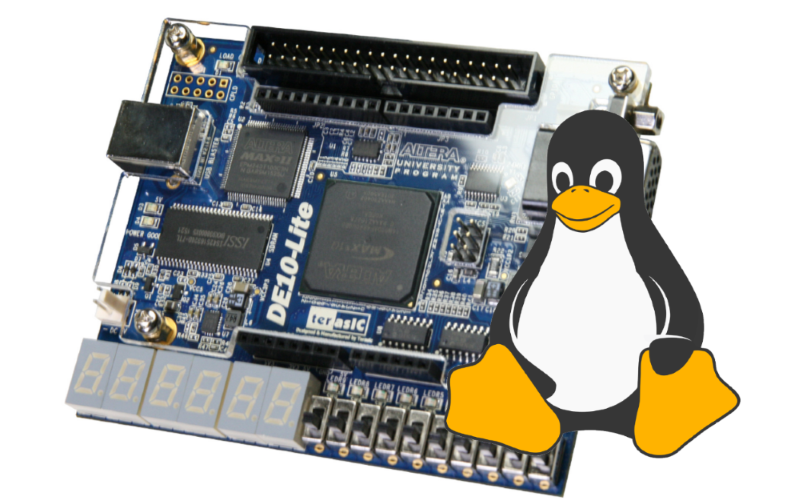

- Terasic DE10-Lite debug board with Altera MAX10 FPGA and SDRAM 64MB on board;

- Pinboard II board as a debugger and UART-converter. You can use any board with an FTDI USB chip that supports MPSSE, an example of such a configuration is described in [ L4 ];

- Windows 7 (x64) computer and Quartus Prime 16.1 for FPGA synthesis and programming;

- Ubuntu 17.04 (x64) virtual machine for building the kernel and RAM image of the file system;

- Internet access;

If you are planning to seriously and deeply immerse yourself in the magic of the Linux kernel, it is strongly recommended that you familiarize yourself with the materials [ L7 ], in particular, with the presentations [ L8 ] and [ L9 ].

If all the listed requirements are met, let's start!

Synthesis of configuration and programming of FPGA

In the MIPSfpga-plus settings (mfp_ahb_lite_matrix_config.vh file), peripheral modules for working with SDRAM and UART, as well as debugging via MPSSE should be enabled if the debugging mechanism described in [ L4 ] is used:

`define MFP_USE_SDRAM_MEMORY `define MFP_USE_DUPLEX_UART `define MFP_USE_MPSSE_DEBUGGER- using Quartus to assemble MIPSfpga-plus and programming the FPGA;

Kernel and RAM build

It is assumed that further actions are performed on the machine running Linux.

update the list of available packages for the system:

sudo apt-get updateInstall the utilities and libraries needed for configuration and build:

sudo apt-get install -y build-essential git libncurses5-dev bc unzipcreate a directory in which all further work will go and go to it:

mkdir ~/mipsfpga cd ~/mipsfpgaDownload toolchain from Imagination Technologies:

wget http://codescape-mips-sdk.imgtec.com/components/toolchain/2016.05-06/Codescape.GNU.Tools.Package.2016.05-06.for.MIPS.MTI.Linux.CentOS-5.x86_64.tar.gzcreate a directory and deploy the downloaded package there:

mkdir ~/mipsfpga/toolchain tar -xvf Codescape.GNU.Tools.Package.2016.05-06.for.MIPS.MTI.Linux.CentOS-5.x86_64.tar.gz -C ~/mipsfpga/toolchainit is desirable (but not necessary) to set the path to the deployed executable files in the $ PATH variable, this will simplify working with them. For example, in ~ / .profile

pathadd() { if [ -d "$1" ] && [[ ":$PATH:" != *":$1:"* ]]; then PATH="$1${PATH:+":$PATH"}" fi } pathadd "$HOME/bin" pathadd "$HOME/.local/bin" pathadd "$HOME/mipsfpga/toolchain/mips-mti-linux-gnu/2016.05-06/bin"we get the Linux kernel:

git clone git://git.kernel.org/pub/scm/linux/kernel/git/stable/linux-stable.git kernelwe get the buildroot with which the RAM image of the file system will be generated:

git clone git://git.buildroot.net/buildrootCreate a directory for buildroot and Linux patches required for deployment to MIPSfpga-plus:

mkdir patchesDownload patches [ L10 ], save them in the newly created directory;

go to the buildroot directory and roll back to version 2017.05.1 (commit f3d8beeb3694):

cd buildroot git checkout 2017.05.1apply the patch to buildroot:

git apply ../patches/MIPSfpga_buildroot.patchperform buildroot configuration:

make xilfpga_static_defconfigif necessary, make changes to the configuration:

make menuconfigWe start the assembly of the RAM image of the file system and go to drink delicious coffee (tea, beer or who loves anything), because The process is very long:

makego to the directory with the Linux kernel and check that the RAM image of the file system is on the expected path (in the future we will need to specify it in the kernel configuration):

cd ../kernel/ ls -l ../buildroot/output/images/rootfs.cpioroll back to version v4.12.1 (commit cb6621858813), because the patch is formed from it:

git checkout v4.12.1apply patch:

git apply ../patches/MIPSfpga_linux.patchWe use the basic configuration of the MIPSfpga kernel:

make ARCH=mips xilfpga_de10lite_defconfigRun the configuration editor:

make ARCH=mips menuconfig- enable RAM disk support and set the path to it (previously we checked the existence of this file):

- save the changes, exit the graphical configurator and start the kernel build:

make ARCH=mips CROSS_COMPILE=~/mipsfpga/toolchain/mips-mti-linux-gnu/2016.05-06/bin/mips-mti-linux-gnu-

Loading the kernel into memory and running

- on the machine to which the hardware debugger is connected, we start OpenOCD, for example, as described in [ L4 ];

- we start the terminal on the same machine (for example, PuTTY) and connect to the COM port (speed 115200);

on the Linux machine where we did the build, run gdb from the MIPS toolchain. It is assumed that we are in the directory with the compiled kernel:

mips-mti-linux-gnu-gdb ./vmlinuxFurther actions are performed in the gdb console.

Connect to OpenOCD, which runs on a machine with a hardware debugger:

(gdb) target remote 192.168..:3333perform a MIPSfpga system reset:

(gdb) mo reset haltWe inform the debugger that our system is Little Endian:

(gdb) set endian littleload the kernel image into memory:

(gdb) loadRun the kernel for execution:

(gdb) continue- if everything is done correctly, then after a while in the previously launched terminal we should see a download log, similar to the one below. Due to the peculiarity of the current kernel configuration, it will not appear immediately, but after a short delay.

Linux version 4.12.1+ (stas@ubuntu) (gcc version 4.9.2 (Codescape GNU Tools 2016.05-06 for MIPS MTI Linux) ) #1 Sat Jul 22 14:35:05 MSK 2017 CPU0 revision is: 00019e60 (MIPS M14KEc) MIPS: machine is terasic,de10lite Determined physical RAM map: memory: 04000000 @ 00000000 (usable) Initrd not found or empty - disabling initrd Primary instruction cache 4kB, VIPT, 2-way, linesize 16 bytes. Primary data cache 4kB, 2-way, VIPT, no aliases, linesize 16 bytes Zone ranges: Normal [mem 0x0000000000000000-0x0000000003ffffff] Movable zone start for each node Early memory node ranges node 0: [mem 0x0000000000000000-0x0000000003ffffff] Initmem setup node 0 [mem 0x0000000000000000-0x0000000003ffffff] Built 1 zonelists in Zone order, mobility grouping on. Total pages: 16256 Kernel command line: console=ttyS0,115200 PID hash table entries: 256 (order: -2, 1024 bytes) Dentry cache hash table entries: 8192 (order: 3, 32768 bytes) Inode-cache hash table entries: 4096 (order: 2, 16384 bytes) Memory: 60512K/65536K available (1830K kernel code, 99K rwdata, 320K rodata, 944K init, 185K bss, 5024K reserved, 0K cma-reserved) NR_IRQS:8 clocksource: MIPS: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 38225208935 ns sched_clock: 32 bits at 50MHz, resolution 20ns, wraps every 42949672950ns Console: colour dummy device 80x25 Calibrating delay loop... 10.81 BogoMIPS (lpj=21632) pid_max: default: 32768 minimum: 301 Mount-cache hash table entries: 1024 (order: 0, 4096 bytes) Mountpoint-cache hash table entries: 1024 (order: 0, 4096 bytes) devtmpfs: initialized clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 7645041785100000 ns futex hash table entries: 256 (order: -1, 3072 bytes) clocksource: Switched to clocksource MIPS random: fast init done workingset: timestamp_bits=30 max_order=14 bucket_order=0 Serial: 8250/16550 driver, 4 ports, IRQ sharing disabled console [ttyS0] disabled b0400000.serial: ttyS0 at MMIO 0xb0401000 (irq = 0, base_baud = 3125000) is a 16550A console [ttyS0] enabled Freeing unused kernel memory: 944K This architecture does not have kernel memory protection. mount: mounting devpts on /dev/pts failed: No such device mount: mounting tmpfs on /dev/shm failed: Invalid argument mount: mounting tmpfs on /tmp failed: Invalid argument mount: mounting tmpfs on /run failed: Invalid argument Starting logging: OK Initializing random number generator... done. Starting network: ip: socket: Function not implemented ip: socket: Function not implemented FAIL Welcome to MIPSfpga mipsfpga login: Work with GPIO

Let's use the Linux capabilities in order to control the peripherals that are available to us (at the time of writing this article is a GPIO, though not fully):

Check that the GPIO driver is loaded and the device is available:

ls /sys/class/gpio/ export gpiochip480 unexportin order to determine the available range of outputs (LEDs on the board are connected in the current configuration), install debugfs and use it to get the necessary information:

mount -t debugfs none /sys/kernel/debug cat /sys/kernel/debug/gpio gpiochip0: GPIOs 480-511, parent: platform/bf800000.gpio, bf800000.gpio:activate LED0 (in the current case, this is gpio480):

echo 480 > /sys/class/gpio/exportput it into output mode:

echo out > /sys/class/gpio/gpio480/directiontranslate it to a high level:

echo 1 > /sys/class/gpio/gpio480/value- if done correctly, the LED 0 LED should be lit.

What's next

The described configuration is, in fact, only the beginning of porting Linux to the MIPSfpga-plus system. To the number of works that must be performed so that the system can be used normally for practical tasks, include:

- support for existing peripherals: interrupt controller, more complete support for GPIO, Altera ADC;

- support for MIPSfpga-plus peripherals, including the currently missing PWM, SPI (limited presence), I2C, DDR and Ethernet interfaces;

- support for external media (mmc / sdram) and the ability to boot from them;

For this reason, if in the current configuration you encounter any errors (bugs), then do not be surprised - there is still a lot of work.

Thanks

The author is grateful to the team of translators from David Harris and Sarah Harris, Digital Circuit Design and Computer Architecture [ L1 ], by Imagination Technologies for their academic license for a modern processor core and educational materials, as well as personally for Yuri Panchulu YuriPanchul for his work on promoting MIPSfpga.

Links

[L1] - Digital circuit design and computer architecture

[L2] - How to start working with MIPSfpga ;

[L3] - MIPSfpga-plus project on github ;

[L4] - MIPSfpga and in-circuit debugging ;

[L5] - MIPSfpga and SDRAM. Part 1 ;

[L6] - MIPSfpga and UART ;

[L7] - Free Electrons. Free training materials and conference presentations ;

[L8] - Free Electrons. Embedded Linux system development course ;

[L9] - Free Electrons. Linux kernel and driver development course ;

[L10] - Patches for buildroot and Linux, required for deployment on MIPSfpga-plus .

')

Source: https://habr.com/ru/post/333920/

All Articles