MIPSfpga and SDRAM. Part 1

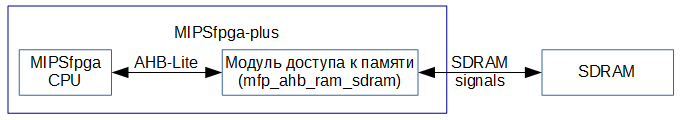

This week, I’ve finished work on adding SDRAM support to the MIPSfpga-plus project. Now, when working with MIPSFpga, in addition to block memory limited by FPGA resources, external RAM is also available.

This article consists of 2 parts:

Part 1. Brief description of the SDRAM access module. An example of use.

Part 2. A detailed description of working with memory, sufficient to ensure that a person who had not previously dealt with RAM chips could understand the module. Bibliography.

It is assumed that the reader at least:

- familiar with the subject area in the volume of the Harris-and-Harris textbook [1] ;

- has experience in C programming, assembler, using gcc;

- has minimal experience with MIPSfpga. Having no such experience, it will be logical to start with simpler things , and only then think about how to use RAM in your system.

If you are already an experienced developer, then Part 1 is to run your eyes diagonally, Part 2 - does not contain anything new for you. In this case, you can bring undoubted benefits to society if you add SDRAM support for another debugging board. At the moment, it is implemented only for Terasic DE10-Lite - one of 9 motherboards to which the MIPSfpga core was ported as part of the MIPSfpga-plus project.

General information

MIPSfpga is an academic licensed (free licensed for educational and research projects) industrial MIPS microAptiv microprocessor core. Yury Panchul wrote at one time about how to get access to the source codes of this kernel.

MIPSfpga-plus is a MIPSfpga-based system-on-chip design, in addition to the core, which includes some additional peripheral strapping. Initially, it was created for laboratory work on working with MIPSfpga, but nothing prevents you from taking it as the basis of your system. One of the main "chips" of the project: the ability to fill the program into the system's memory using usb-uart converters ($ 5), which are more available than Bus Blaster ($ 50).

system configuration

Basic parameters of the SDRAM access module ( mfp_ahb_ram_sdram.v )

- Currently, only chips with a 16-bit data bus are supported - this is exactly the bit capacity of the memory on the Terasic DE10-Lite;

- Small module size (less than 300 lines of code);

- The minimum set of operations required for operation has been implemented: INIT, READ, WRITE, AUTO_REF;

- The module operates at a processor frequency (50 MHz), no synchronization or clock domain crossing ;

- All settings related to the timings are included in the parameters of the module, which simplifies its transfer to other cards;

- Optimization of paging memory access is absent. Batch operations (Burst Operation, WRAP4 in AHB-Lite bus terminology) are treated as a set of individual (SINGLE) operations;

- To run in simulation mode, the Verilog model from Micron was used ;

- Correct work on the hardware is confirmed on the Terasic DE10-Lite board (memory chip IS42S16320D );

- To verify the correctness, a separate C-program 04_memtest was written , launched on MIPSfpga-plus. It writes a large array into memory and then, with a certain periodicity, checks the integrity of the data in this array, displaying the current stage on the LED, the number of the test cycle and the total number of errors on the 7-segment indicators;

- The debugging of the developed module is available "in isolation" from the MIPSfpga-plus code within the project: ahb_lite_sdram is the sandbox in which I started development. There testbenches, as well as standalone module that simulates the work of AHB-Lite master without cpu (for hardware testing). This project can be used to simplify porting to other boards;

- When working with SDRAM, the cpu down clock mode available in MIPSfpga-plus is not supported (option MFP_USE_SLOW_CLOCK_AND_CLOCK_MUX).

Order of configuration and running a memory test

It is assumed that you already have MIPSfpga and MIPSfpga-plus deployed and compiled. If so, then to use SDRAM you need:

- Get the current MIPSfpga-plus code from github.

- Select the type of memory used in mfp_ahb_lite_matrix_config.vh

MFP_USE_BYTE_MEMORY - block memory with byte-by-byte storage (x8);

MFP_USE_WORD_MEMORY - block memory with word storage (x32);

MFP_USE_BUSY_MEMORY - block memory with imitation of delay in operation;

MFP_USE_SDRAM_MEMORY - sdram memory. - Go to the programs \ 04_memtest directory ;

- Select the appropriate mode of operation in main.c

SIMULATION

SDRAM_64M

SDRAM_8M - Set (select) the stack boundary in the 02_compile_and_link.bat file corresponding to the mode and amount of memory;

For simulation mode (SIMULATION)

- Build the program, create files to initialize the memory, run the simulation:

02_compile_and_link.bat

05_generate_verilog_readmemh_file.bat

06_simulate_with_modelsim.bat

When working with the board (SDRAM_64M, SDRAM_8M)

- Build and fill configuration on fpga;

- Perform (press) a reset on the board — upon reset, initialized including. sdram access module;

- Build the program, create a file for uploading the firmware, upload the firmware:

02_compile_and_link.bat

08_generate_motorola_s_record_file.bat

12_upload_to_the_board_using_uart.bat - During operation, the LEDs will indicate the current test phase:

0 - write cycle;

1- cache reset cycle;

2 - pause;

3 - reading cycle;

4 - all checks completed, no errors;

5 - errors found during checks. - During operation, 7-segment indicators (on de10-lite there are 6 of them) will indicate:

two senior digits - check number;

four lower digits - the number of read errors detected.

What else can you do

My goal was to create a solution that is as simple as possible, transparent and easily portable to other cards. The module is somewhat primitive in comparison with its "older" counterparts, this leaves room for modernization and increasing its performance:

- To ensure the memory operation at the double frequency (100 MHz), relative to the frequency cpu (50 MHz);

- Ensure that the memory works at the maximum frequency available for the chip by adding clock domain crossing;

- Provide the ability to work memory of another bit;

- Optimize the work of the module for paging memory access;

- Choosing the best startup strategy AUTO_REF, depending on the intensity of memory use.

I would be grateful for Pulrequests with bug fixes and new functionality.

Thanks

The author is grateful to the team of translators of the textbook by David Harris and Sarah Harris “Digital circuit design and computer architecture” , by Imagination Technologies, as well as personally by Yuri Panchul YuriPanchul .

')

Source: https://habr.com/ru/post/321530/

All Articles