You can download materials from the Nanometer ASIC workshop (RUSNANO / MISiS / Imagination Technologies) - educational program for all chips

Lord The Nanometer ASIC seminar organized by RUSNANO, MISiS and Imagination Technologies turned out to be quite popular - more than 180 people registered to it, 127 came, and representatives of all significant Russian microelectronic projects lit up in the audience - from radiation-resistant microchips from NIISI to smart chips. cameras from ELVIS-NeoTek, engineers from Baikal Electronics, project managers for microchip design automation from Moscow State University, developers of Russian FPGAs from Voronezh, teachers from HSE / MIEM and other universities, organizations izatorov Olympiads for high school students from MIPT and many others.

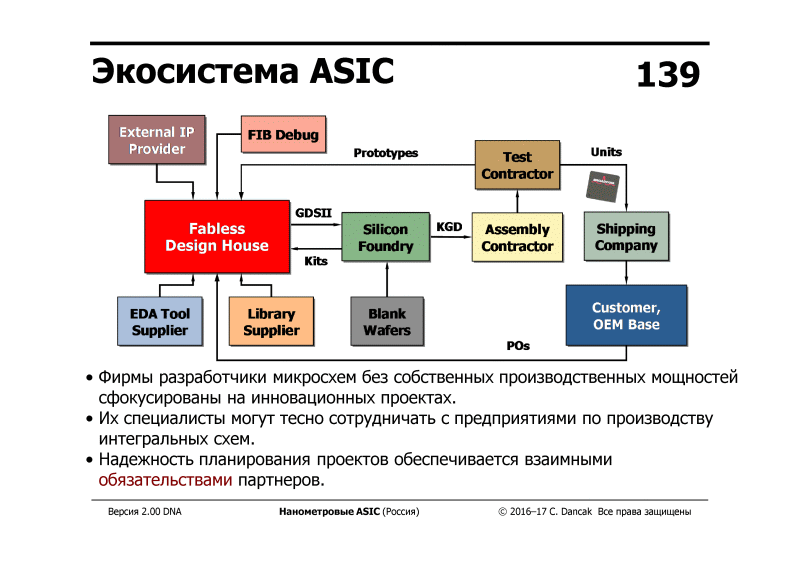

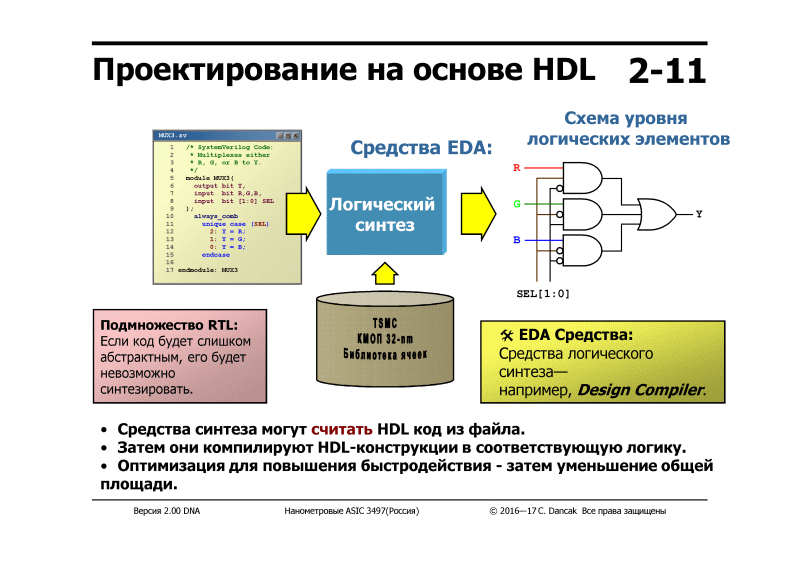

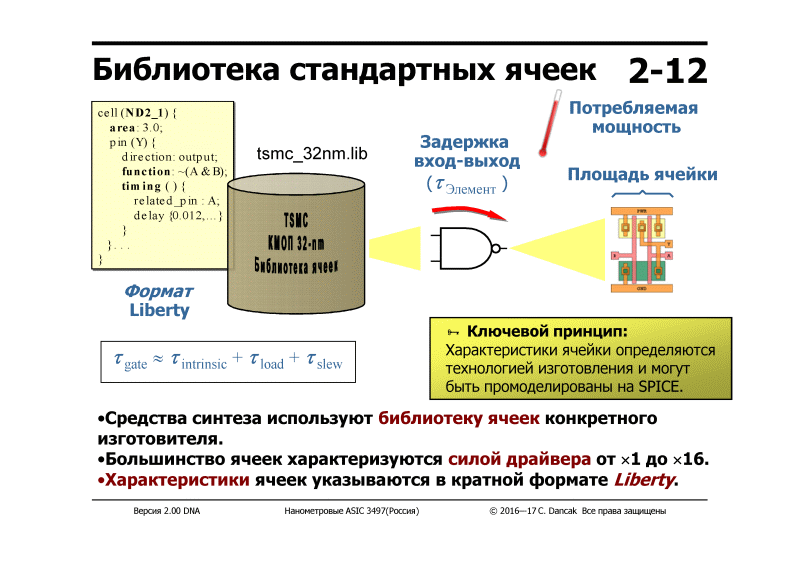

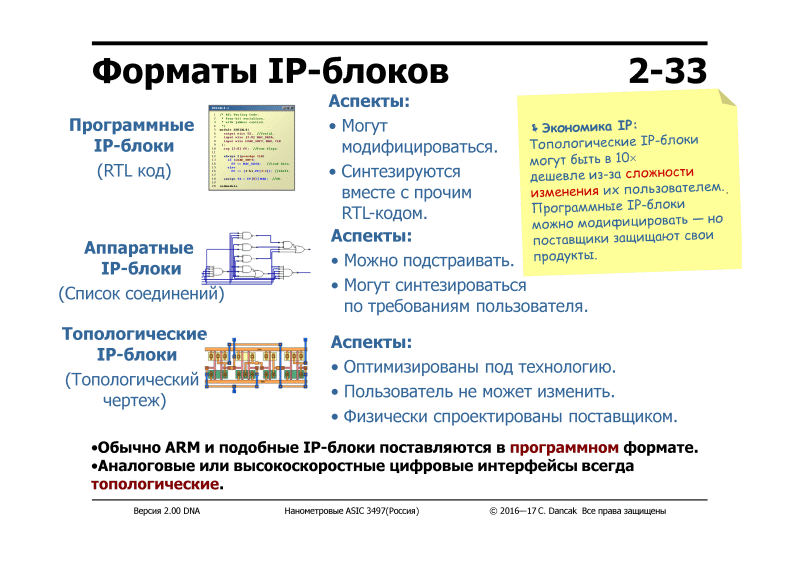

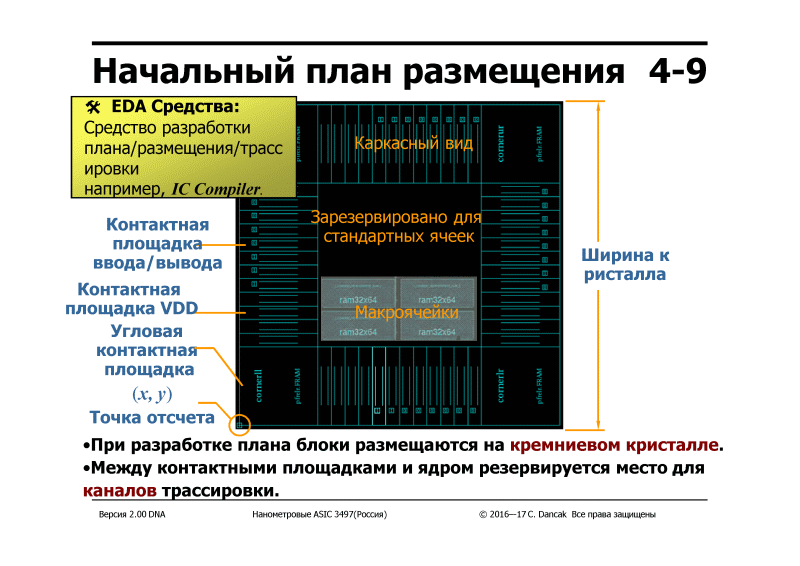

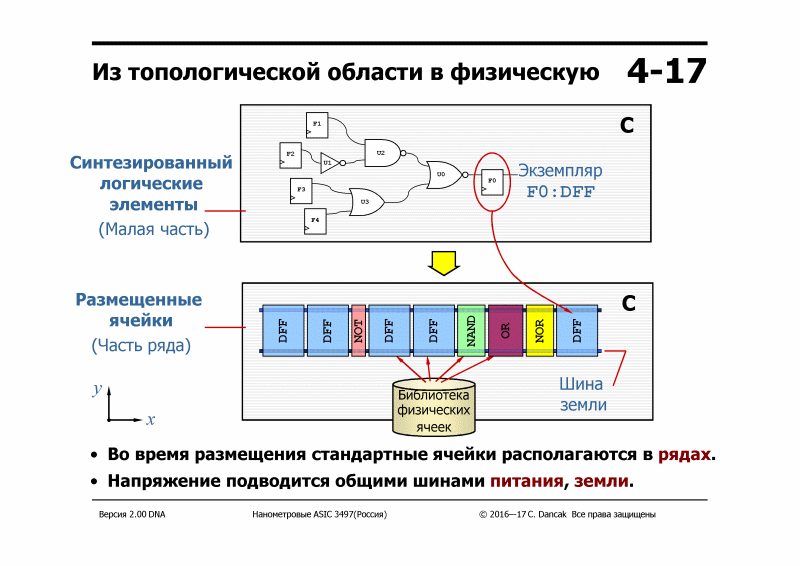

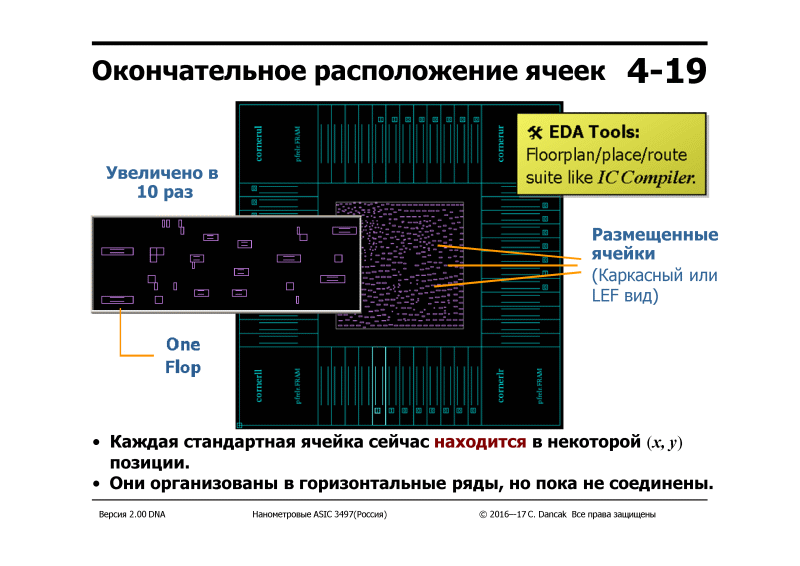

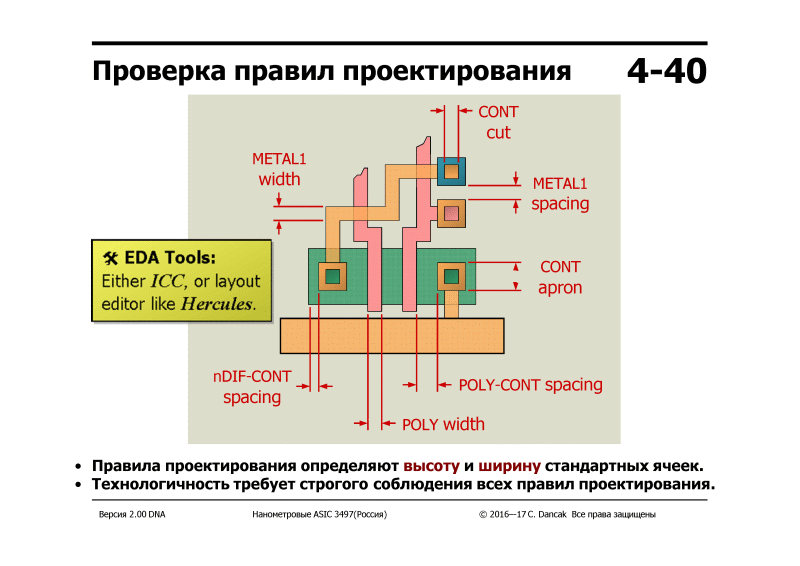

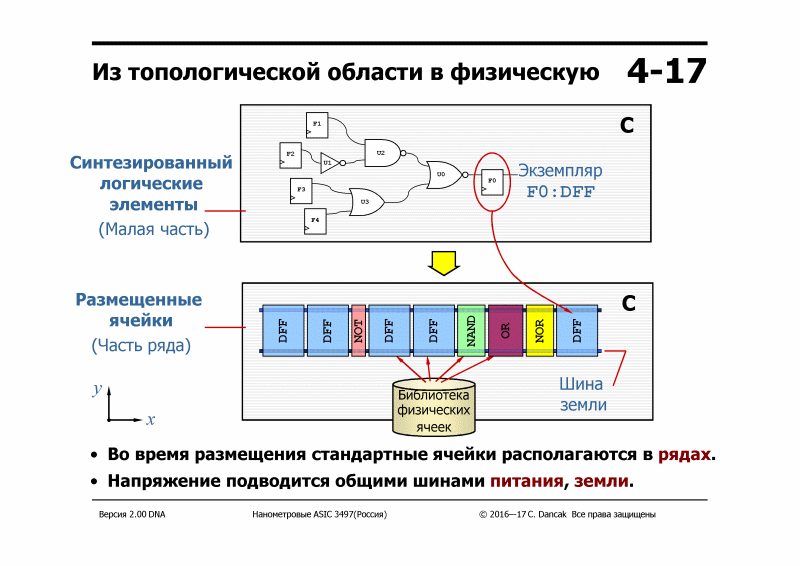

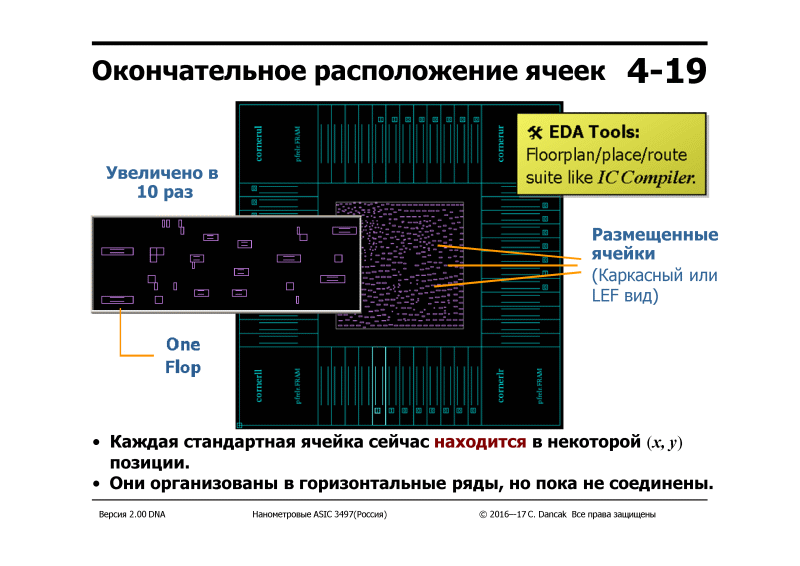

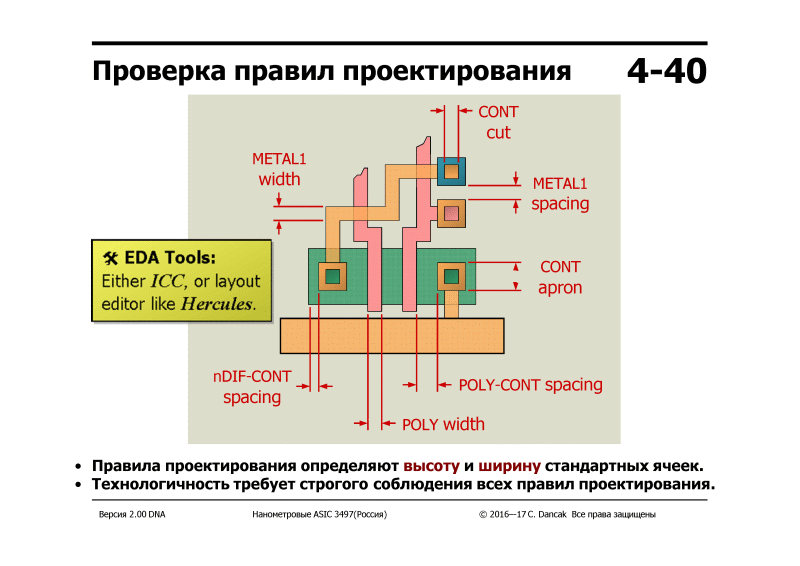

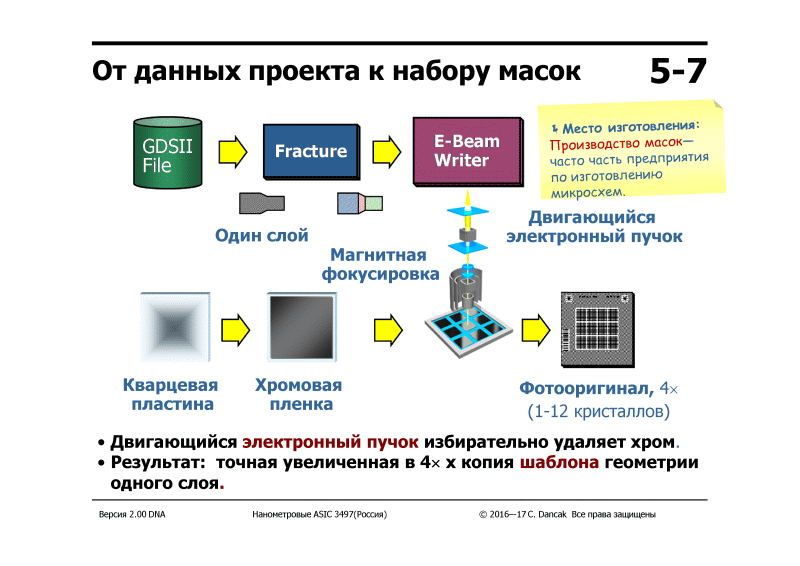

Despite the fact that the seminar was too elementary for professional specialists in using Synopsys IC Compiler, its introductory nature was redeemed by its breadth - engineers from the whole design and production chain could refresh the memory they forgot, investors in the semiconductor industry could see the companies in which they invest are doing, the students looked at what they might like and say so where to dig (in the semiconductor industry of Silicon Valley, young engineers specialize in logical / physical / analogue design quite early in their careers).

The workshop presenter, lecturer at the University of California at Santa Cruz (Silicon Valley office) Charles Dancak answers the questions:

')

Download all slides in Russian here .

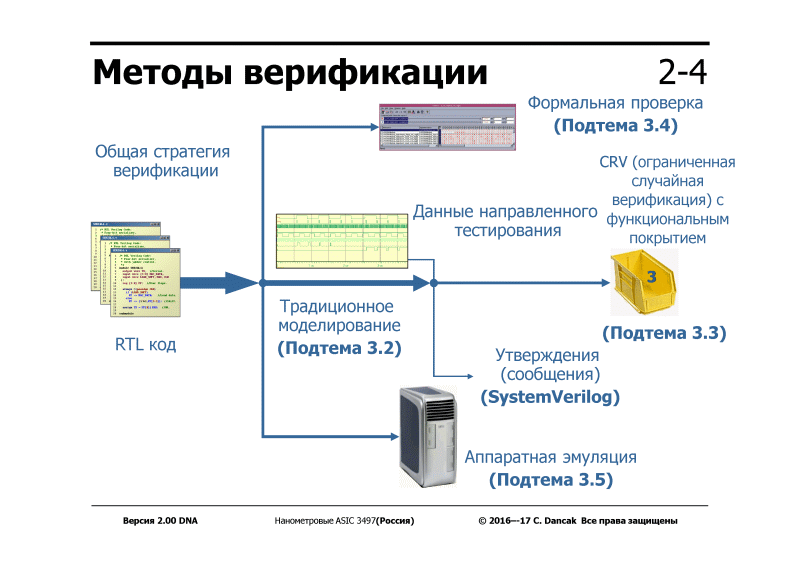

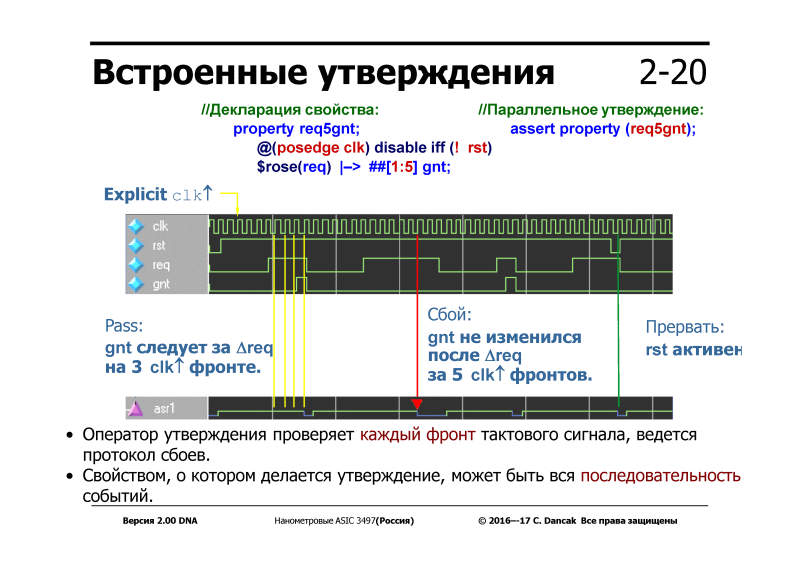

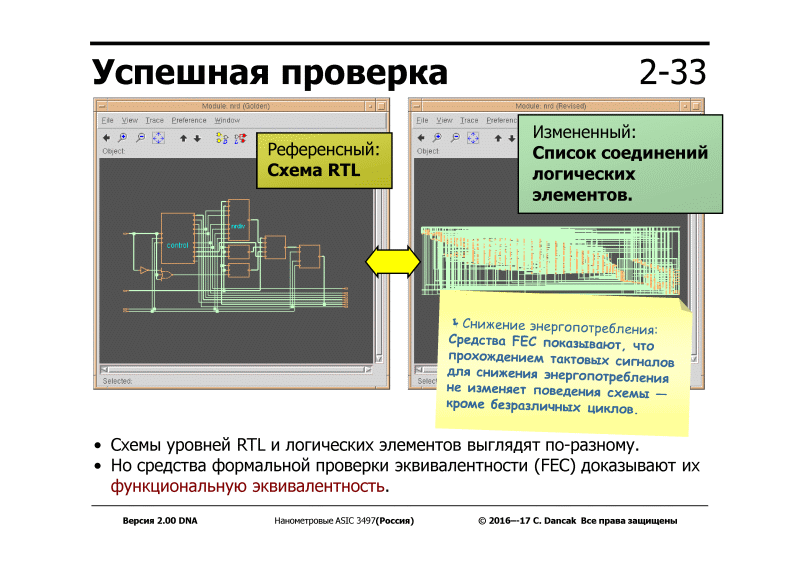

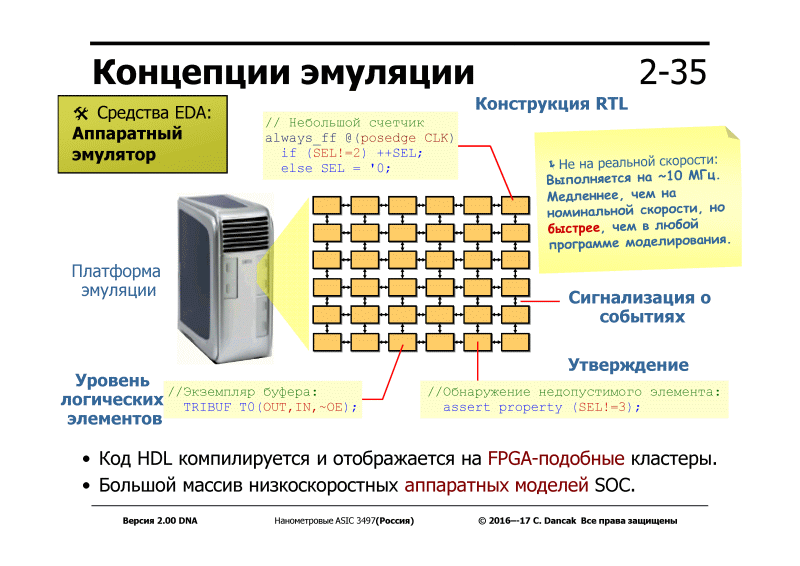

Under the cut - selected slides Nanometer ASIC (25 of 322):

Materials related workshops Imagination Technologies (MIPSfpga and Connected MCU) can be downloaded here .

Cadence Design Systems also took part in the workshops (with presentations) to balance the yin-yang with slides based on the route from Synopsys. Cadence and Synopsys are two world leaders in chip design tools.

Despite the fact that the seminar was too elementary for professional specialists in using Synopsys IC Compiler, its introductory nature was redeemed by its breadth - engineers from the whole design and production chain could refresh the memory they forgot, investors in the semiconductor industry could see the companies in which they invest are doing, the students looked at what they might like and say so where to dig (in the semiconductor industry of Silicon Valley, young engineers specialize in logical / physical / analogue design quite early in their careers).

The workshop presenter, lecturer at the University of California at Santa Cruz (Silicon Valley office) Charles Dancak answers the questions:

')

Download all slides in Russian here .

Under the cut - selected slides Nanometer ASIC (25 of 322):

Materials related workshops Imagination Technologies (MIPSfpga and Connected MCU) can be downloaded here .

Cadence Design Systems also took part in the workshops (with presentations) to balance the yin-yang with slides based on the route from Synopsys. Cadence and Synopsys are two world leaders in chip design tools.

Source: https://habr.com/ru/post/314892/

All Articles