For lovers of FPGAs, ASICs, architecture and micro-architecture - more about seminars and conveyors

Colleagues: as you may already know, Imagination Technologies (known as a GPU developer inside the Apple iPhone + follower of the Stanford / MIPS cult project) along with RUSNANO + MISiS + MGU + MIPT + MIET in Moscow, ITMO in St. Petersburg and Kiev activists from KPI and KSU - conducts a series of workshops on chip design and embedded microprocessor programming. The closest of these seminars will be next week (October 18-20 in Almaty). In this post - the current hourly schedule of seminars and a little bit aesthetic images of the conveyors of embedded microprocessor cores, the length, maximum frequency and power consumption of which we will talk a little during the seminars.

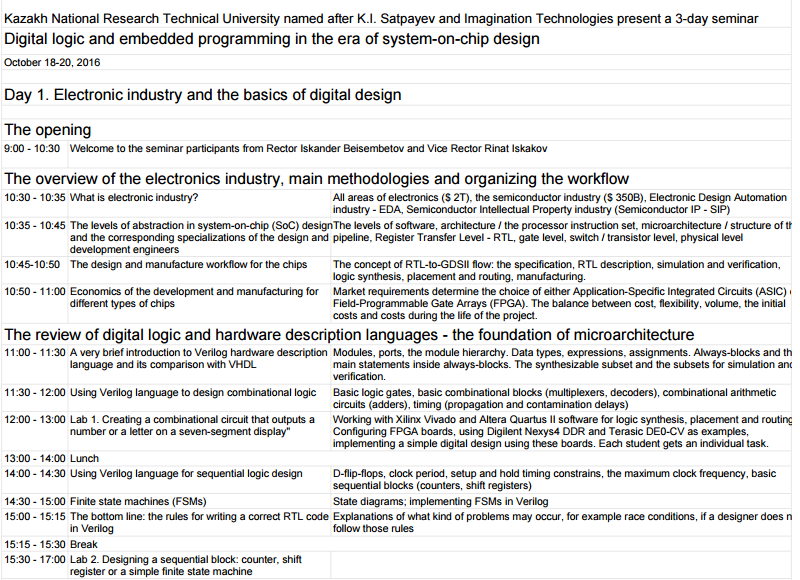

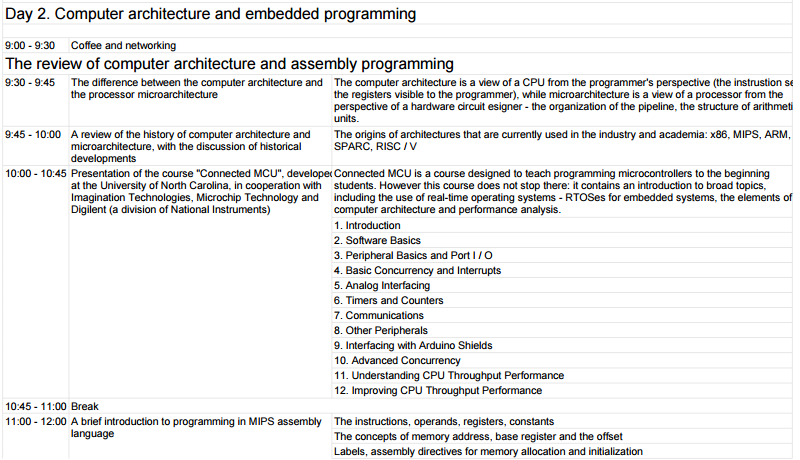

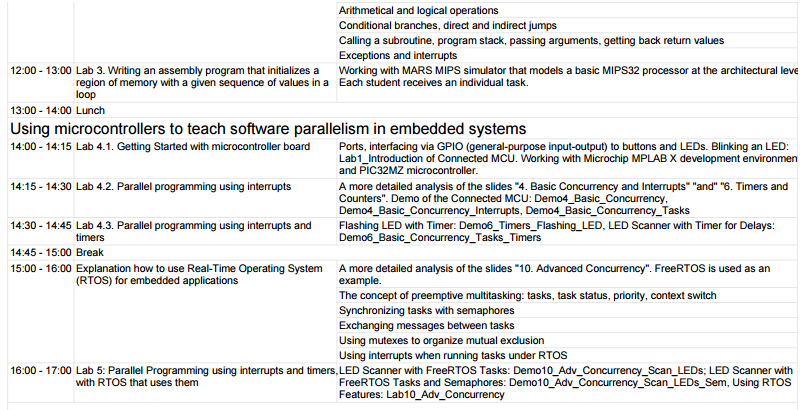

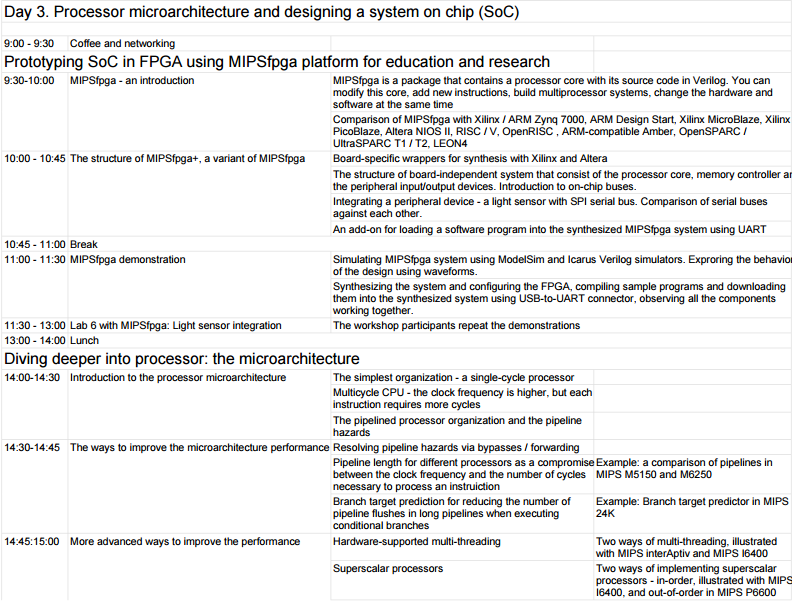

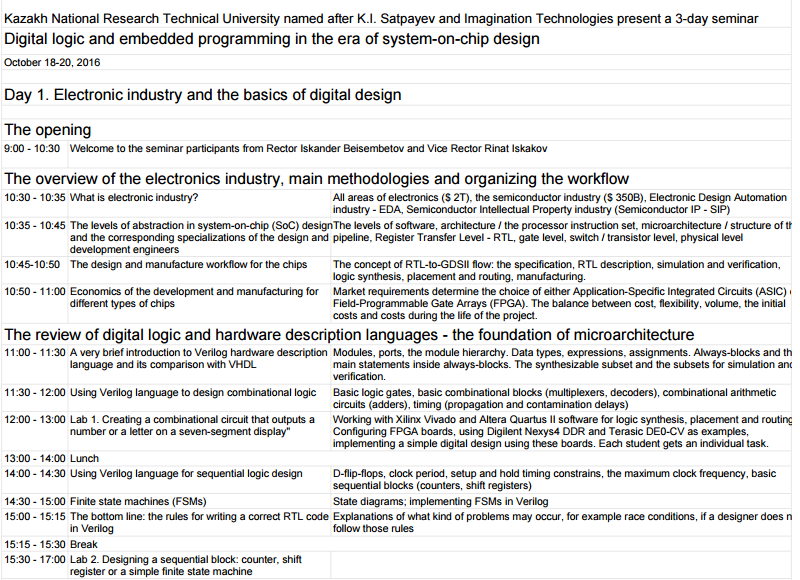

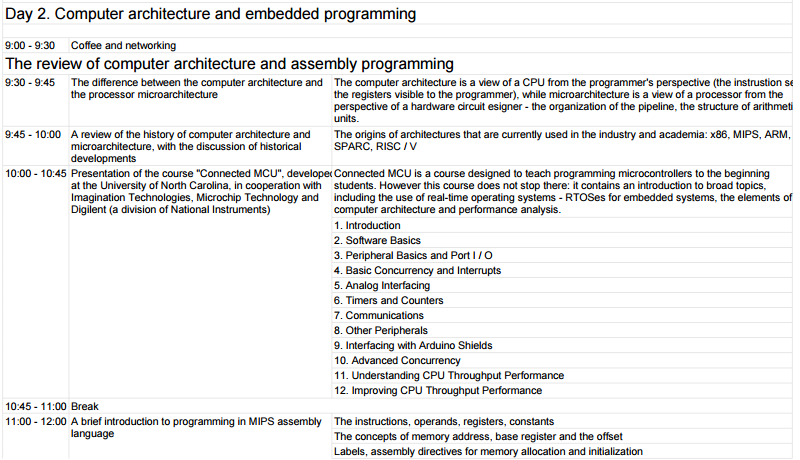

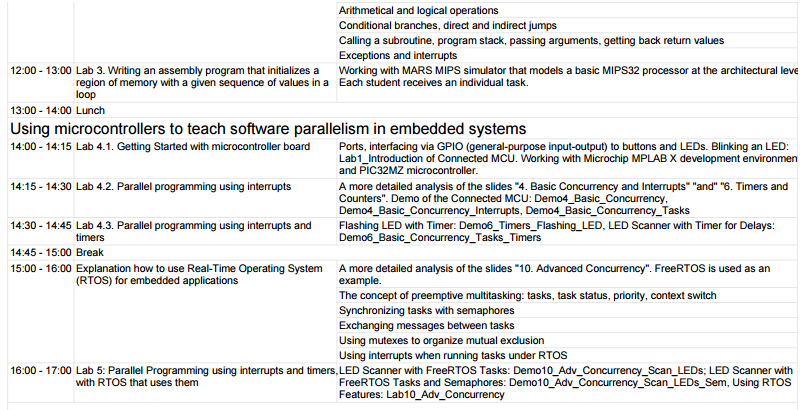

So schedules:

First Alma-Ata.

')

October 18-20, 2016 - Almaty, Kazakh National Technical University named after KI Satpayev.

The main organizer is the Department of Automation and Control of KazNRTU, in partnership with Almaty Management University.

Registration email for the MIPSfpga and Connected MCU combined seminar - seminar-kazntu@silicon-kazakhstan.com .

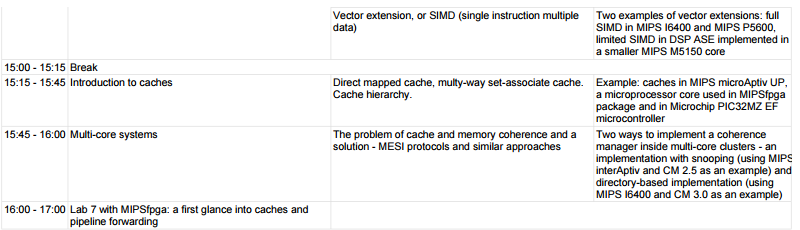

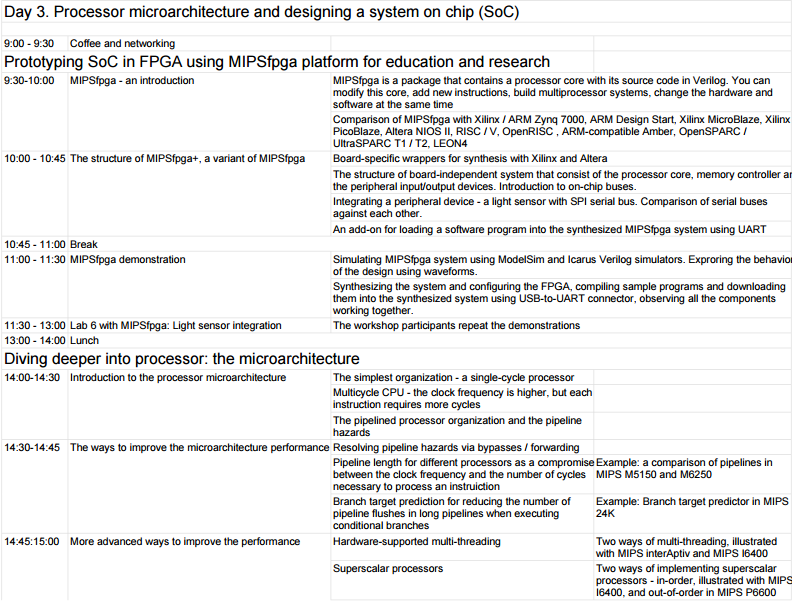

Almaty residents were asked to do seminars in English, so here’s a schedule of three-day seminars in English:

Dates and contact information about the seminars in Russia and Ukraine is given in the post Chips from different sides: Nanometer ASIC, MIPSfpga and Connected MCU workshops in Russia, Ukraine and Kazakhstan . Briefly:

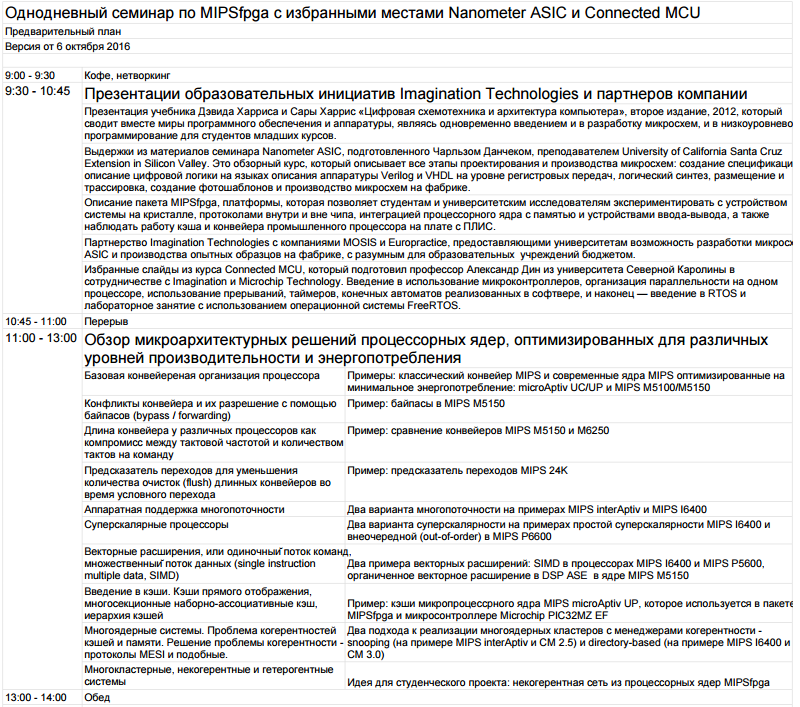

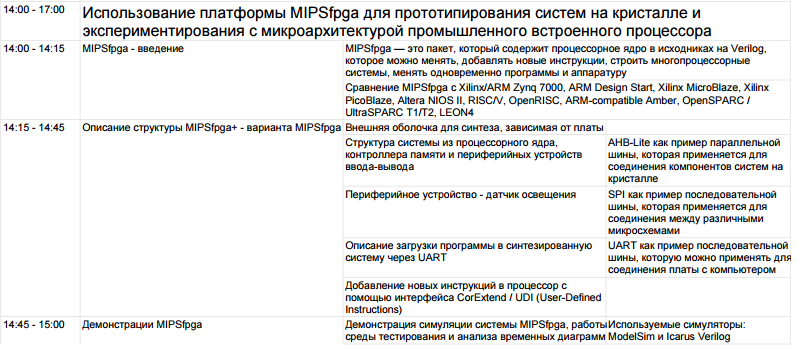

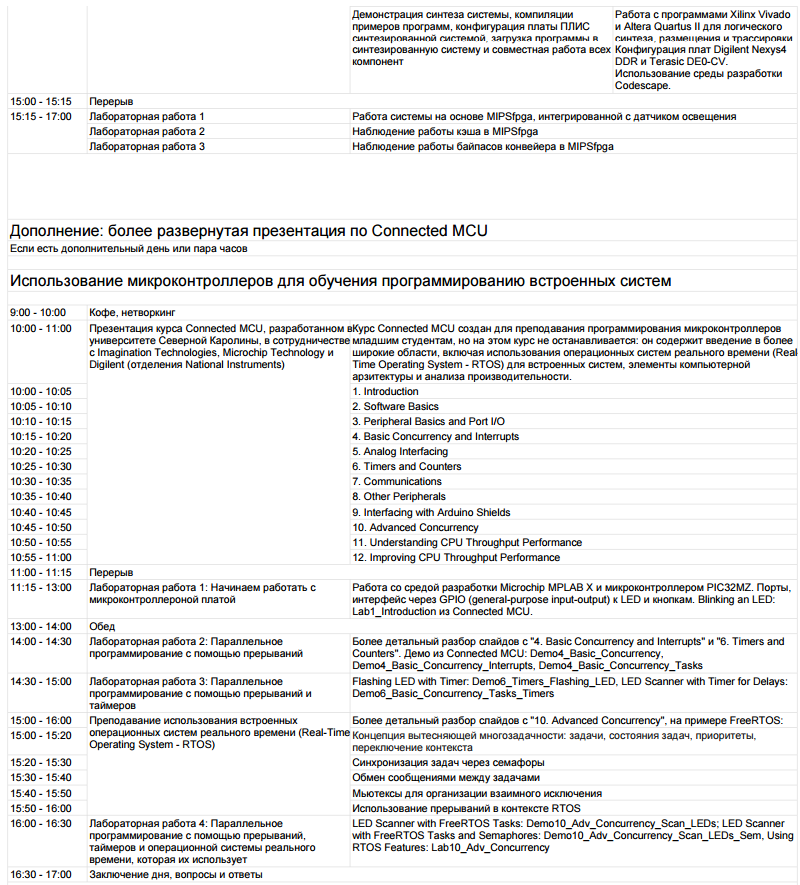

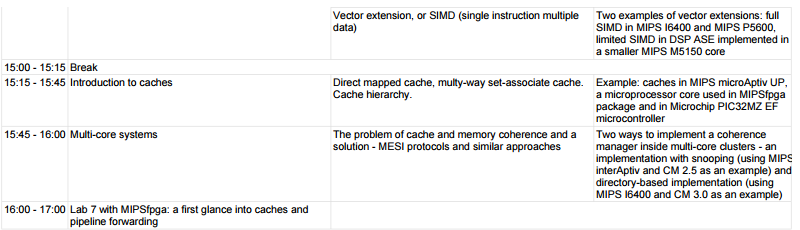

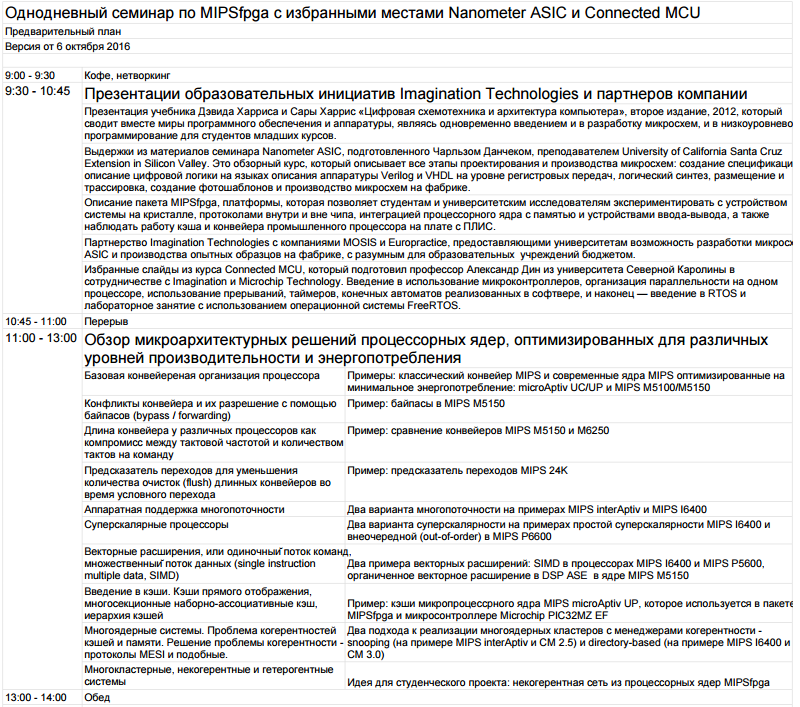

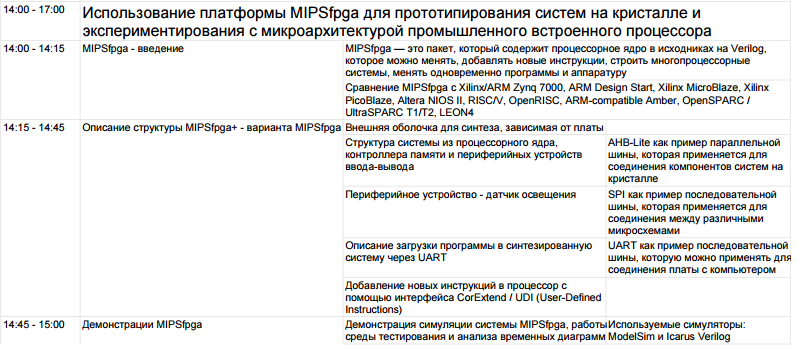

The preliminary schedule of one-day seminars on MIPSfpga at Moscow State University, MIPT, MIET, ITMO and KPI is lower. At the end there is an info about a possible extra day, which theoretically could arise at MSU in addition to the current schedule:

About the Nanometer ASIC seminar recently there was already a post ( habrahabr.ru/post/311662 ) and there will be one more, since an addendum can be made to the seminar. The current schedule is http://edunano.ru/doc/6335690702352234538 .

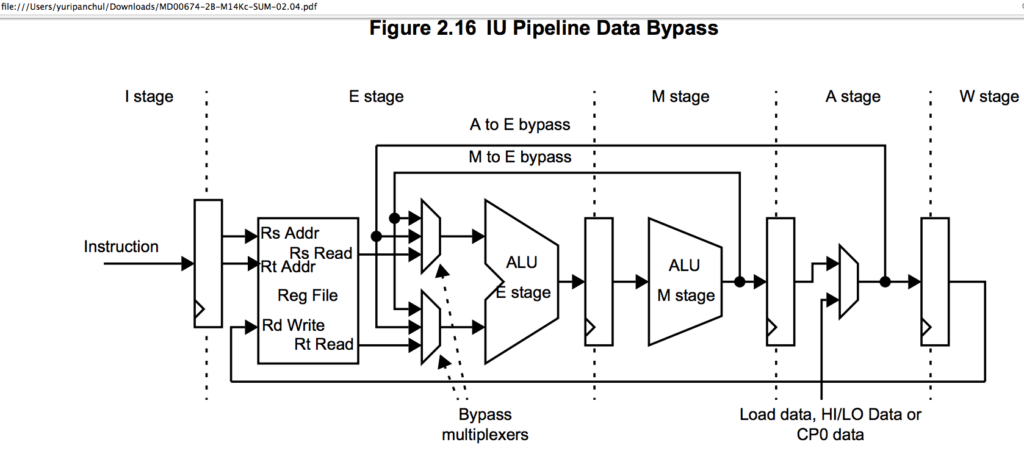

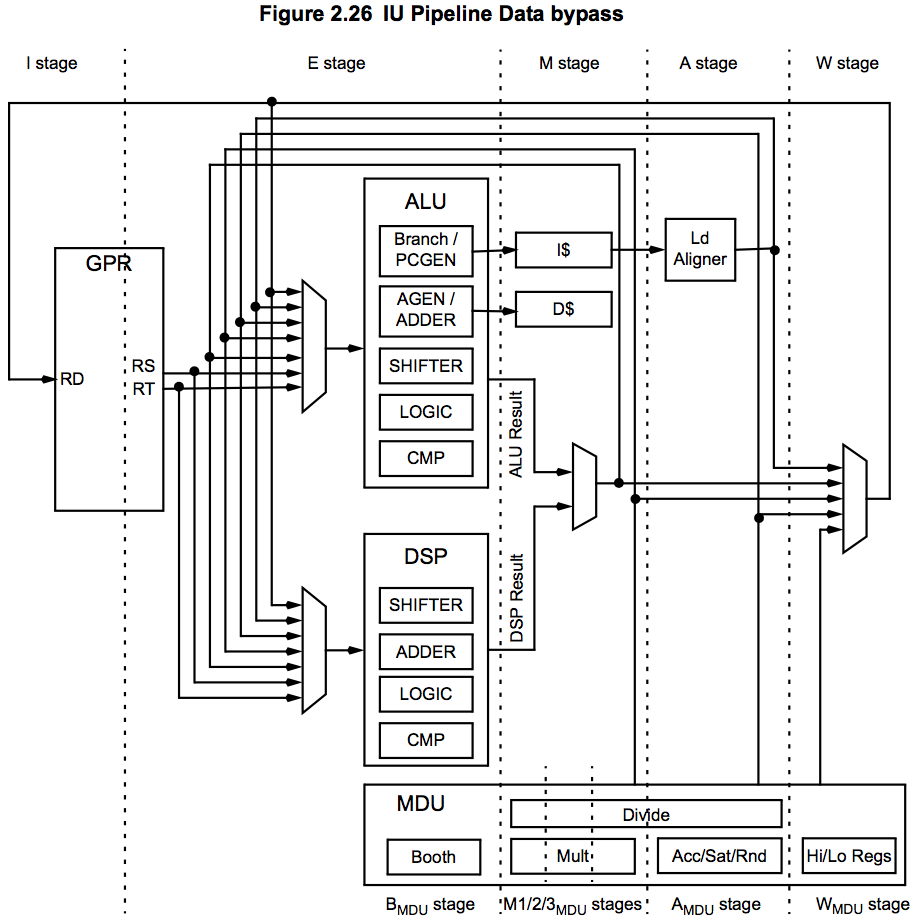

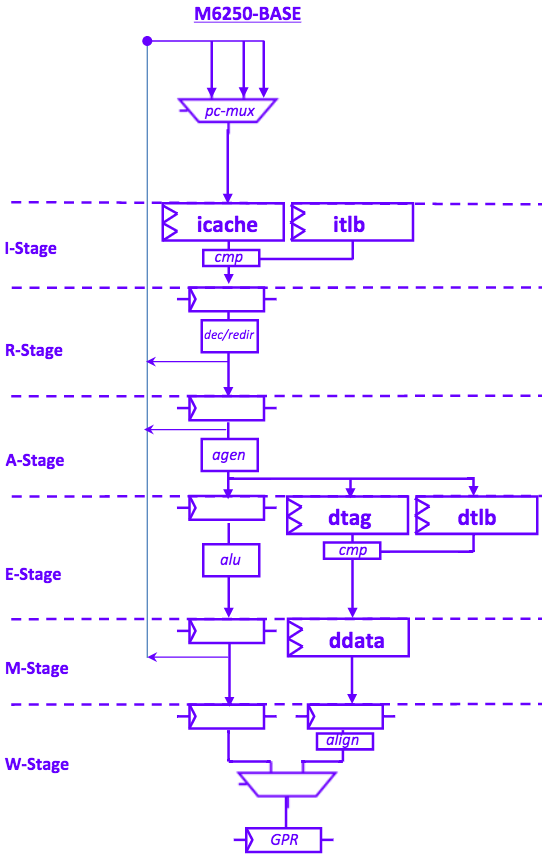

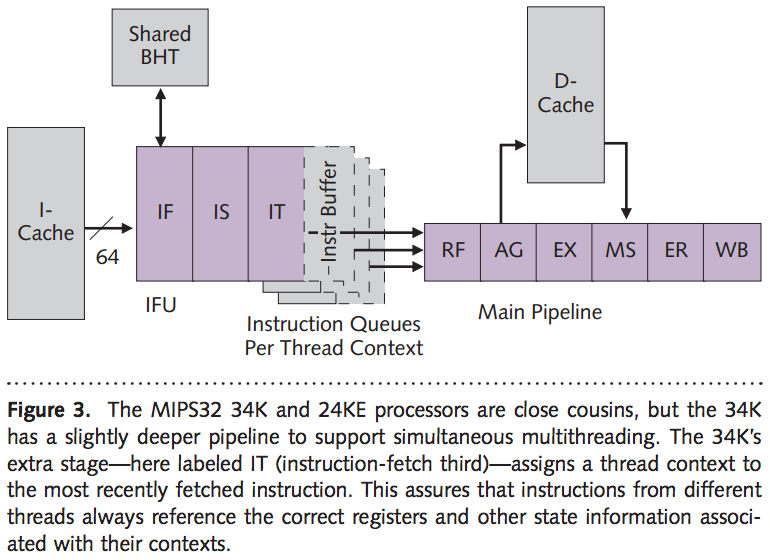

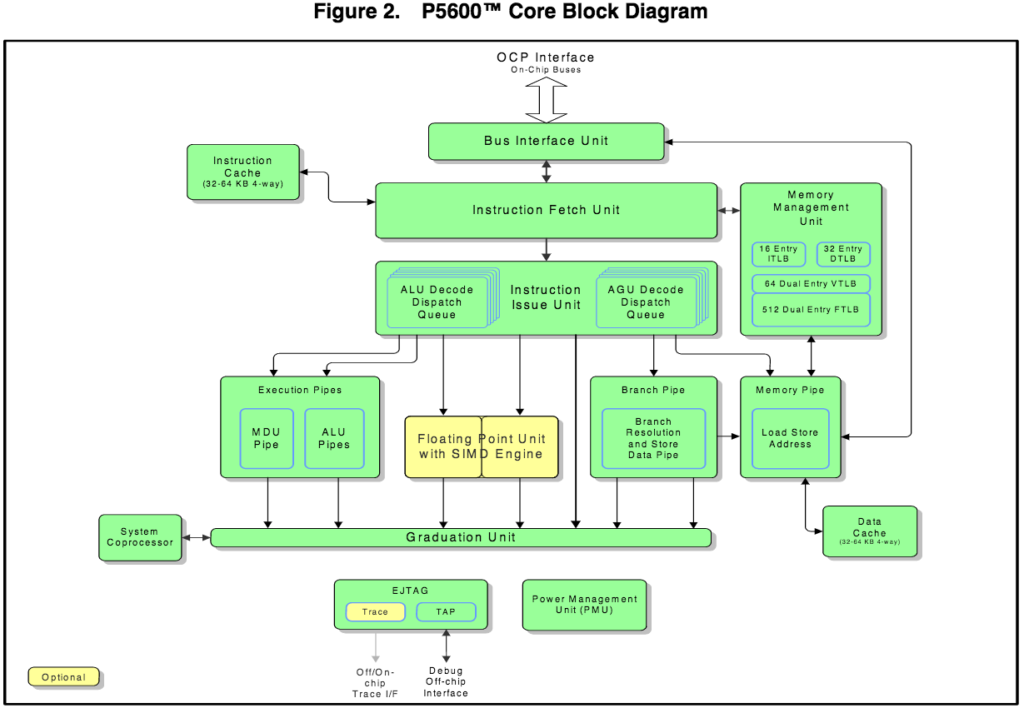

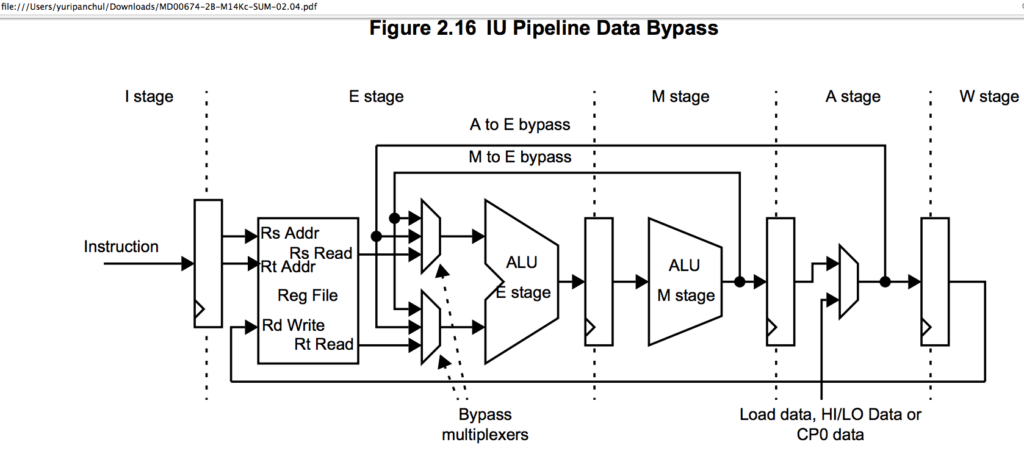

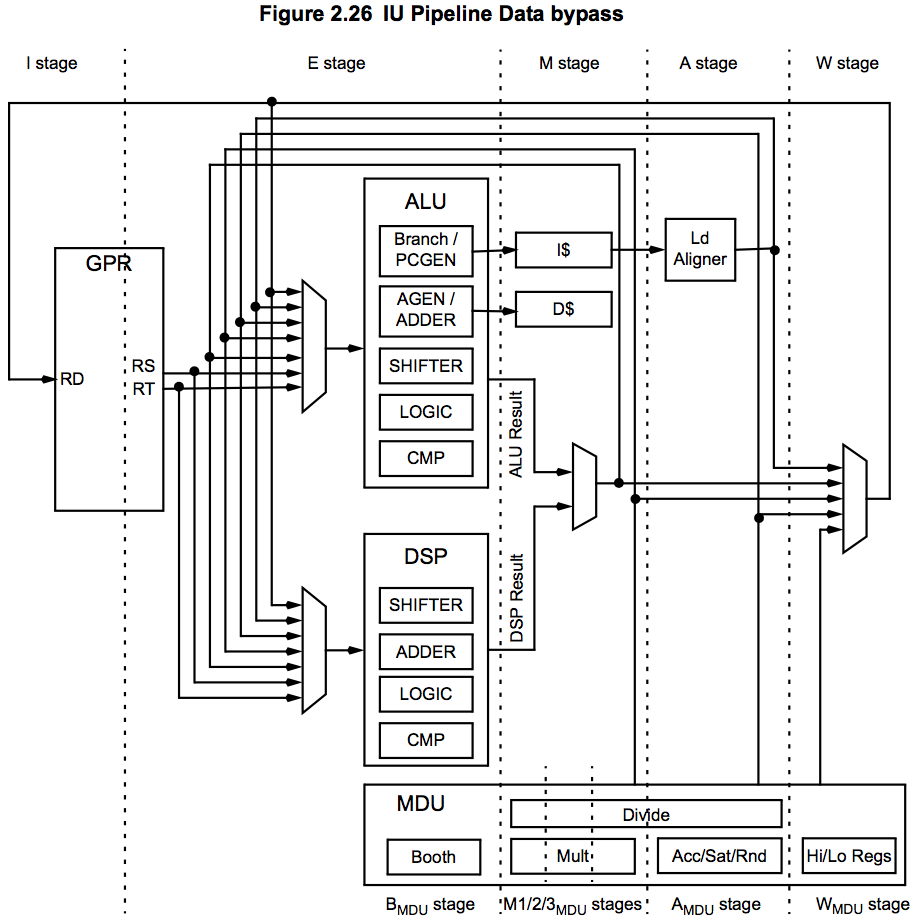

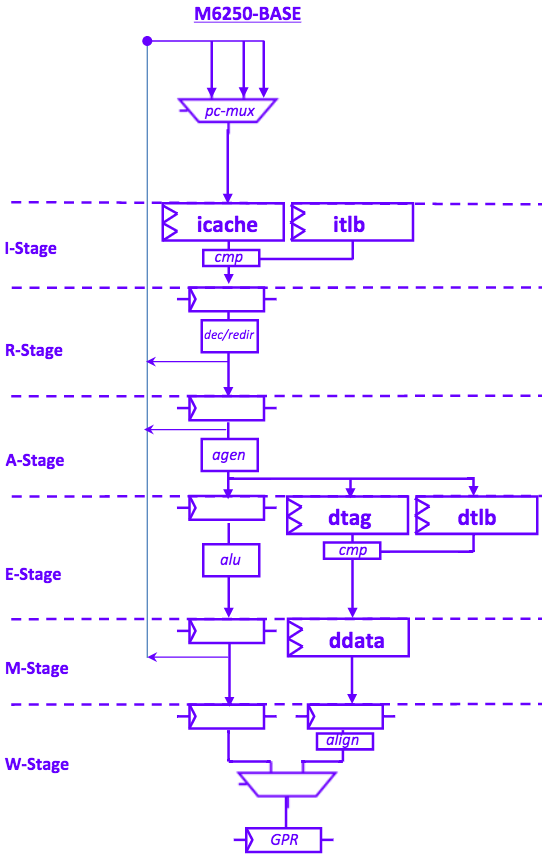

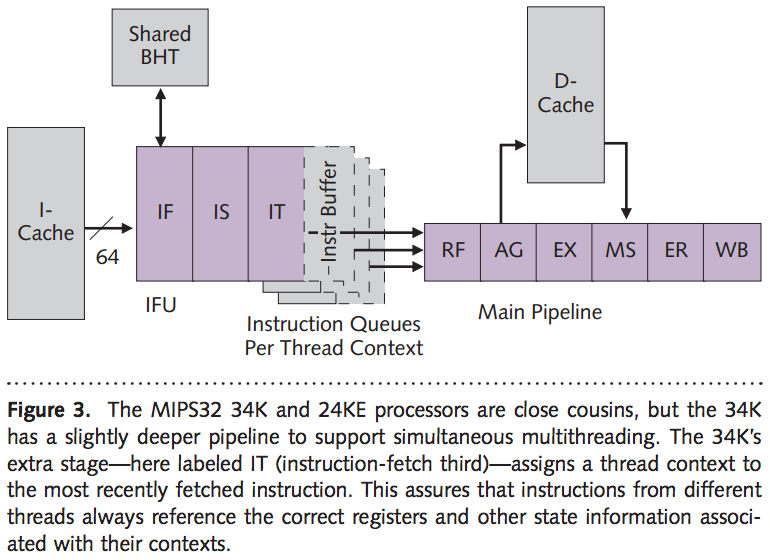

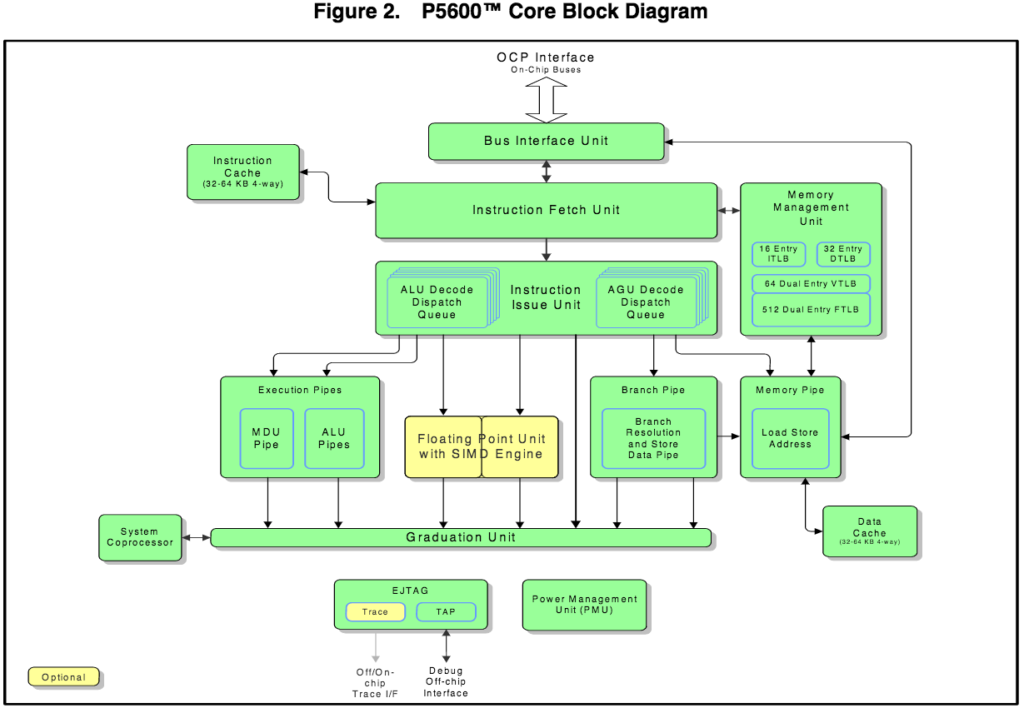

And now several pipeline diagrams of embedded microprocessor cores optimized for a different balance of performance, maximum clock frequency and power consumption. We will talk about this a bit in each of the seminars:

Short conveyor, low maximum clock frequency, but low power consumption:

The conveyor is slightly longer, but the maximum clock frequency is higher:

But the processor is optimized for efficiency (high enough performance with low power consumption):

Optimized for speed: superscalar with OoO:

See you!

So schedules:

First Alma-Ata.

')

October 18-20, 2016 - Almaty, Kazakh National Technical University named after KI Satpayev.

The main organizer is the Department of Automation and Control of KazNRTU, in partnership with Almaty Management University.

Registration email for the MIPSfpga and Connected MCU combined seminar - seminar-kazntu@silicon-kazakhstan.com .

Almaty residents were asked to do seminars in English, so here’s a schedule of three-day seminars in English:

Dates and contact information about the seminars in Russia and Ukraine is given in the post Chips from different sides: Nanometer ASIC, MIPSfpga and Connected MCU workshops in Russia, Ukraine and Kazakhstan . Briefly:

- October 18-20, 2016 - Almaty, KazNRTU (in partnership with Almaty Management University) - MIPSfpga and Connected MCU - seminar-kazntu@silicon-kazakhstan.com

- October 24, 2016 - Moscow, MSU - MIPSfpga and some Connected MCU - seminar-msu@silicon-russia.com

- October 25, 2016 - Dolgoprudny, MIPT - MIPSfpga and a little Connected MCU - seminar-mipt@silicon-russia.com

- October 26, 2016 - Zelenograd, MIET - MIPSfpga and a bit of Connected MCU - seminar-miet@silicon-russia.com

- October 27, 2016 - Moscow, Nautech company (LLC “High Technologies”) - MIPSfpga and a bit Connected MCU - seminar-nautech@silicon-russia.com

- October 28 - a series of reports at the SECR conference in Moscow on topics related to the workshops of Imagination Technologies and Nauteha

- October 31 - November 1, 2016 - Moscow, MISiS / FIEP RUSNANO / eNANO - Nanometer ASIC - Yulia.Osaulets@rusnano.com , with a copy at seminar-misis@silicon-russia.com

- November 2 and 3, 2016 - St. Petersburg, ITMO - Nanometer ASIC - seminar-itmo-nanometer-asic@silicon-russia.com

- November 7, 2016 - St. Petersburg, ITMO - MIPSfpga and a bit Connected MCU - seminar-itmo-mipsfpga@silicon-russia.com

- November 9 and 10, 2016 - Kiev, KPI / Lampa / Belka - Nanometer ASIC - seminar-kpi-nanometer-asic@silicon-ukraine.com

- November 11, 2016 - Kiev, KPI / Lampa / Belka - MIPSfpga and a little Connected MCU - seminar-kpi-mipsfpga@silicon-ukraine.com

- November 12, 2016 - Kiev, KPI / Lampa / Belka - Hackathon by MIPSfpga - hackathon-kpi@silicon-ukraine.com

The preliminary schedule of one-day seminars on MIPSfpga at Moscow State University, MIPT, MIET, ITMO and KPI is lower. At the end there is an info about a possible extra day, which theoretically could arise at MSU in addition to the current schedule:

About the Nanometer ASIC seminar recently there was already a post ( habrahabr.ru/post/311662 ) and there will be one more, since an addendum can be made to the seminar. The current schedule is http://edunano.ru/doc/6335690702352234538 .

And now several pipeline diagrams of embedded microprocessor cores optimized for a different balance of performance, maximum clock frequency and power consumption. We will talk about this a bit in each of the seminars:

Short conveyor, low maximum clock frequency, but low power consumption:

The conveyor is slightly longer, but the maximum clock frequency is higher:

But the processor is optimized for efficiency (high enough performance with low power consumption):

Optimized for speed: superscalar with OoO:

See you!

Source: https://habr.com/ru/post/312354/

All Articles