Clocking Atmel microcontrollers SAMD20 / 21

Some theory

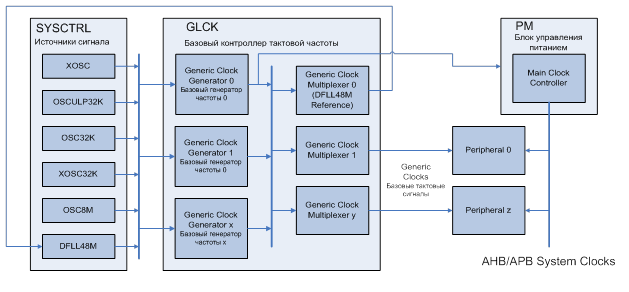

According to the documentation for Atmel microcontrollers of the SAMD20 / 21 series, the clocking system consists of the following blocks:

- source block (controlled by SYSCTRL)

- Clock source is the base frequency in the system. This may be, for example, an internal oscillator 8 MHz (OSC8M), an external oscillator (XOSC), a digital phase locked loop (DFLL48M);

- The basic clock controller (GLCK-generic clock controller), which controls the distribution of clock signals and consists of:

- Basic Frequency Generators (Generic Clock Generator) is a programmable pre-splitter, to which any signal source can be connected. From the output of the generator 0 (GCLKGEN [0], GCLK_MAIN), the signal goes to the power management unit (Power manager), which generates the main clock signal;

- Base clocks (Generic Clocks) are usually signals that clock the periphery. Basic clock signals using the basic signal multiplexers can use any of the clock signals available in the system. Different peripheral units may use different clock signals. The output of multiplexer 0 is used as the reference source for the digital phase locked loop unit. Note that in this case, the DFLL output should not be used as a reference signal for a generator, the output of which is used as a reference for multiplexer 0.

- power management unit (PM - Power manager)

- power control unit controls the synchronous clocking of the system. This includes CPUs, buses (APB, AHB) and synchronous (in terms of CPUs) peripherals. It contains clocking masks with which you can turn on and off the user interface of the periphery, as well as dividers for CPU clock signals, buses.

Peripherals can be clocked simultaneously with 2 clocks:

- synchronous from Power Manager (provides peripherals with CPU via APB / AHB bus);

- asynchronous from GCLK (ensures the operation of the "core" of the periphery).

The synchronization between these two clock signals is implemented in hardware. And even if the frequencies and signal sources are the same, synchronization still happens.

All registers clocked with the same frequency and source as the buses do not require synchronization. All registers of the “core” require synchronization when writing, and some when reading.

The synchronization process is indicated by the SYNCBUSY bit in the status register or by interrupt.

Thus, in theory, to adjust the clock signals you need:

- Choose a base source (or several) of the reference clock: it can be an external oscillator, an internal, etc. (SYSCTRL block)

- Configure the prescaler and multiplexer for each of the base signals (GCLK block).

- Select the main clock signal (output from generator 0).

- Adjust peripheral clocking (generic clocks).

To work correctly with the clock signals, you need to look into the electrical characteristics at the end of the datasheet, since there are many interesting things. In particular:

- DFLL reference clock can be:

- minimum value: 0.732 kHz

- typical value: 32.768 kHz

- maximum value: 35.1 kHz

- DFLL output: 47 to 49 MHz

- external oscillator must be: no more than 32 MHz.

How does the code in ASF

We will not go into the details of the entire library, you can read about it in the article about ASF . Consider only what concerns clocking. When you create a project in Atmel Studio, a main.c file is created, which already contains system_init () .

The prototype of this function is located in the src / asf / sam0 / system / system.c file :

/** * \brief Initialize system. * * This function will call the various initialization functions within the * system namespace. If a given optional system module is not available, the * associated call will effectively be a NOP (No Operation). * * Currently the following initialization functions are supported: * - System clock initialization (via the SYSTEM CLOCK sub-module) * - Board hardware initialization (via the Board module) * - Event system driver initialization (via the EVSYS module) * - External Interrupt driver initialization (via the EXTINT module) */ void system_init(void) { /* Configure GCLK and clock sources according to conf_clocks.h */ system_clock_init(); /* Initialize board hardware */ system_board_init(); /* Initialize EVSYS hardware */ _system_events_init(); /* Initialize External hardware */ _system_extint_init(); } We are interested in system_clock_init () , which, in turn, is defined in clock.c .

In general, the code for this function is made entirely on defines from asf / config / conf_clocks.h . Therefore, you can not understand much, rather just for the sake of interest to see.

But the whole configuration takes place in conf_clocks.h in accordance with the plan above.

Practice

Consider all the example. Suppose we have a motherboard with MK SAM20 / 21, which is clocked from external quartz at 7.3728 MHz, and we want to receive a system clock 48 MHz.

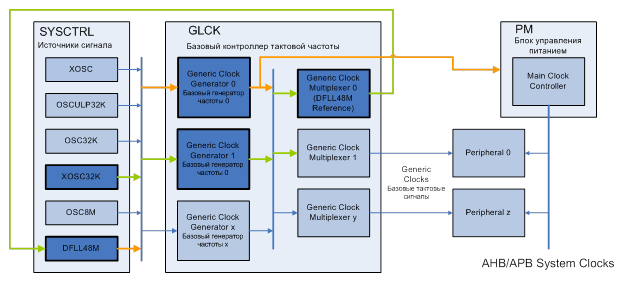

We have to configure everything as shown by the orange arrows in the figure below:

Those. The base oscillator 1 must have a clock signal from the external quartz at the input, which must be divided to a frequency acceptable for DFLL (from 0.7 to 35 kHz). The DFLL must be enabled, an appropriate reference signal for it and the multiplication factor are chosen to get something close to 48 MHz at the output. DFLL output must be set to base generator 0.

The calculation of the coefficients of division and multiplication.

In order to get an acceptable reference clock signal for DFLL, the signal from the external oscillator must be very divided:

7.3728 MHz / 256 = 28.8 kHz

And the multiplication factor for DFLL is determined on the basis of the input (reference frequency) and the desired output frequency:

28.8 * 1666 = 47.980800 MHz

Now consider how to do this in conf_clocks.h .

We allow clocking from an external source and specify its parameters:

// SYSTEM_CLOCK_SOURCE_XOSC configuration - External clock/oscillator # define CONF_CLOCK_XOSC_ENABLE true # define CONF_CLOCK_XOSC_EXTERNAL_CRYSTAL SYSTEM_CLOCK_EXTERNAL_CRYSTAL # define CONF_CLOCK_XOSC_EXTERNAL_FREQUENCY 7372800UL # define CONF_CLOCK_XOSC_STARTUP_TIME SYSTEM_XOSC_STARTUP_32768 # define CONF_CLOCK_XOSC_AUTO_GAIN_CONTROL true # define CONF_CLOCK_XOSC_ON_DEMAND true # define CONF_CLOCK_XOSC_RUN_IN_STANDBY false Allowing DFLL to work:

// SYSTEM_CLOCK_SOURCE_DFLL configuration - Digital Frequency Locked Loop # define CONF_CLOCK_DFLL_ENABLE true # define CONF_CLOCK_DFLL_LOOP_MODE SYSTEM_CLOCK_DFLL_LOOP_MODE_CLOSED # define CONF_CLOCK_DFLL_ON_DEMAND false Configure DFFL (reference frequency source and multiplication factor):

// DFLL closed loop mode configuration # define CONF_CLOCK_DFLL_SOURCE_GCLK_GENERATOR GCLK_GENERATOR_1 # define CONF_CLOCK_DFLL_MULTIPLY_FACTOR 1666 # define CONF_CLOCK_DFLL_QUICK_LOCK true # define CONF_CLOCK_DFLL_TRACK_AFTER_FINE_LOCK true # define CONF_CLOCK_DFLL_KEEP_LOCK_ON_WAKEUP true # define CONF_CLOCK_DFLL_ENABLE_CHILL_CYCLE true # define CONF_CLOCK_DFLL_MAX_COARSE_STEP_SIZE (0x1f / 4) # define CONF_CLOCK_DFLL_MAX_FINE_STEP_SIZE (0xff / 4) Set up the generators 0 and 1 (allow the work, choose the reference frequency):

// Set this to true to configure the GCLK when running clocks_init. If set to // false, none of the GCLK generators will be configured in clocks_init(). # define CONF_CLOCK_CONFIGURE_GCLK true // Configure GCLK generator 0 (Main Clock) # define CONF_CLOCK_GCLK_0_ENABLE true # define CONF_CLOCK_GCLK_0_RUN_IN_STANDBY false # define CONF_CLOCK_GCLK_0_CLOCK_SOURCE SYSTEM_CLOCK_SOURCE_DFLL # define CONF_CLOCK_GCLK_0_PRESCALER 1 # define CONF_CLOCK_GCLK_0_OUTPUT_ENABLE false // Configure GCLK generator 1 # define CONF_CLOCK_GCLK_1_ENABLE true # define CONF_CLOCK_GCLK_1_RUN_IN_STANDBY false # define CONF_CLOCK_GCLK_1_CLOCK_SOURCE SYSTEM_CLOCK_SOURCE_XOSC # define CONF_CLOCK_GCLK_1_PRESCALER 256 # define CONF_CLOCK_GCLK_1_OUTPUT_ENABLE false Stock

For the most attentive, we are pleased to announce that the Rainbow company is renewing the promotion of the free distribution of ATSAMD20G16A-AU microcontrollers for radio amateurs (and not only):

After receiving and processing the application, we will contact you and explain where and when to pick up the samples (SVAO).

- Samples are provided free of charge on condition of pickup from the Moscow office of Rainbow

- 2 microcontrollers are provided per person.

- To participate in the action, it is necessary to send an application to the email address gav@rtcs.ru for obtaining samples with brief information about yourself and the intended use of microcontrollers (full name and contact information, 3-5 project description sentences)

- Participants of the action are offered specials. The price of the evaluation fee of the SAM D20 series with the ATSAMD20-XPRO debugger is 1000 rubles (the number of boards is limited)

After receiving and processing the application, we will contact you and explain where and when to pick up the samples (SVAO).

Done!

')

Source: https://habr.com/ru/post/275375/

All Articles