The phase shift signal on VHDL

This article is a continuation of a series of topics VHDL delay element , VHDL delay element. Another look at the delay elements on VHDL implemented in the FPGA.

The focus will be on a specific application example, which anyone can run in the simulator or a real gland. The example was created for convenient simulation in the Xilinx ISE environment using Modelsim SE and with minimal changes implemented into a full-fledged IP Core.

Perform a phase shift of the pulsed signal by a predetermined amount (the pulse duration is arbitrary), possibly not synchronous with the frequency of the core logic. Do this without rebooting or shutting down the module / device.

DIP switch 8 positions, which set the delay code in the binary code (shift value). Hard or Soft Reset - initial reset, setting default parameters. The reference frequency is 100 MHz, i.e. 10 ns minimum displacement time.

')

Impulse will call a logical unit - 1.

Pause, logical zero - 0.

The code is implemented as a state machine, which, in my opinion, thanks to the step-by-step structure and the ability to give a distinct name to each stage, is very simple and straightforward.

In addition to the comments to the code, a testbench simulation file is attached.

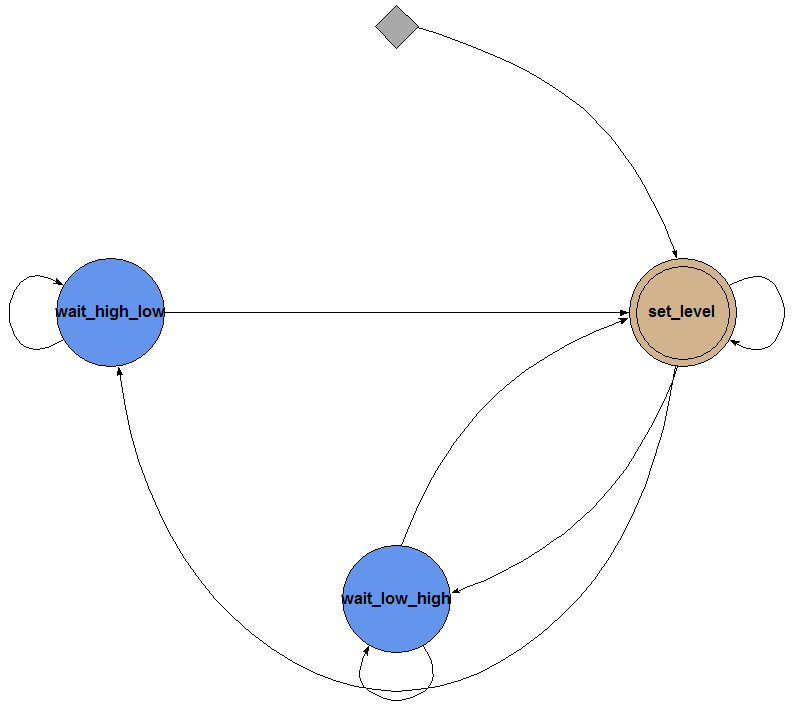

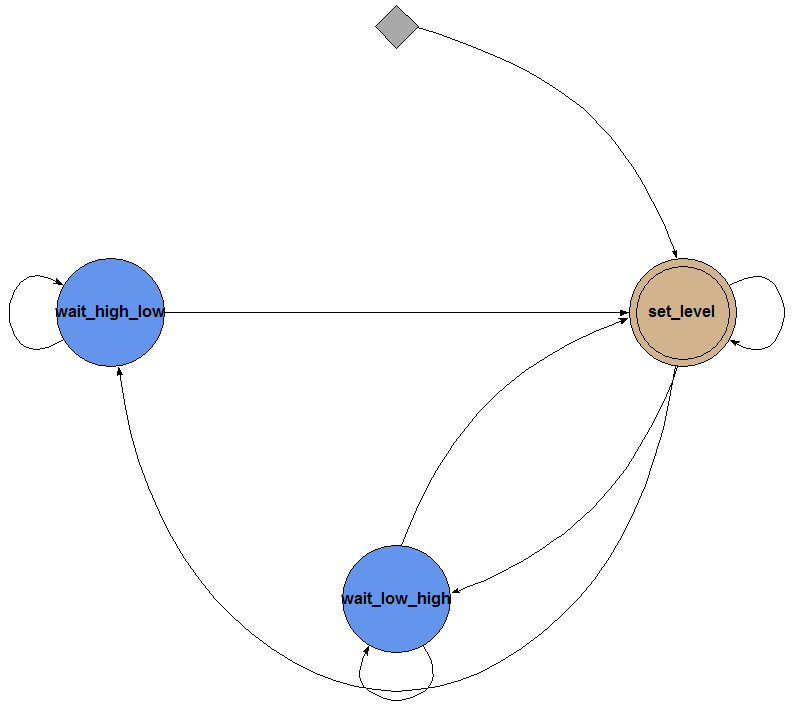

Chart finite state machine:

The main logic. The code tracks the change in the signal level, then the counter is started, when its value becomes equal to the offset set, the output goes to the same level as it is being monitored and so on in a circle.

Simulation code for Modelsim:

An experienced electronics engineer could notice the shortcomings of this code, namely. Exposed delay should not exceed:

- pulse duration, if the pulse duration is less than the pause duration;

- pause duration, if the pause duration is less than the pulse duration.

Those. the value of the phase shift should not exceed 180 ° for both 0 and 1 in the case of a pulse signal.

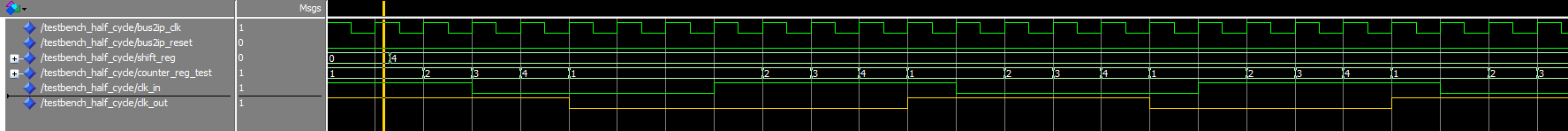

In the diagram below you can see how the phase of the input signal is shifted by 40 ns in real time, so to speak, with a delay in the operation of the logic:

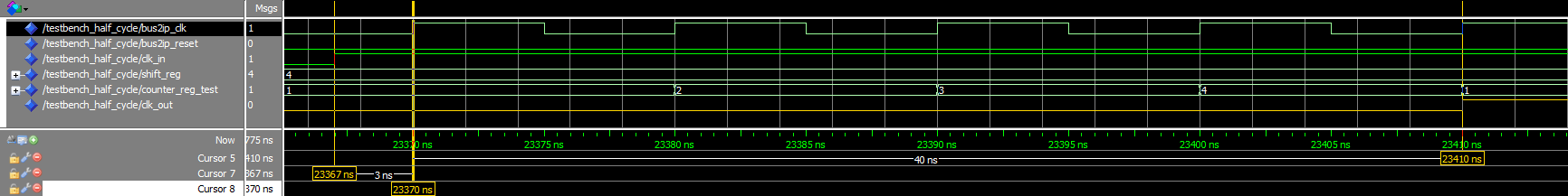

The following is a demonstration of the situation if the tuned signal and the reference frequency are asynchronous:

I suggest you analyze this situation and draw your own conclusions.

I will be glad to your comments and comments, with the help of which in the next article, this code will be supplemented with new functionality.

Thanks for attention.

The focus will be on a specific application example, which anyone can run in the simulator or a real gland. The example was created for convenient simulation in the Xilinx ISE environment using Modelsim SE and with minimal changes implemented into a full-fledged IP Core.

Formulation of the problem

Perform a phase shift of the pulsed signal by a predetermined amount (the pulse duration is arbitrary), possibly not synchronous with the frequency of the core logic. Do this without rebooting or shutting down the module / device.

Instruments

DIP switch 8 positions, which set the delay code in the binary code (shift value). Hard or Soft Reset - initial reset, setting default parameters. The reference frequency is 100 MHz, i.e. 10 ns minimum displacement time.

')

Implementation

Impulse will call a logical unit - 1.

Pause, logical zero - 0.

The code is implemented as a state machine, which, in my opinion, thanks to the step-by-step structure and the ability to give a distinct name to each stage, is very simple and straightforward.

In addition to the comments to the code, a testbench simulation file is attached.

Chart finite state machine:

The main logic. The code tracks the change in the signal level, then the counter is started, when its value becomes equal to the offset set, the output goes to the same level as it is being monitored and so on in a circle.

freq_shift_half_cycle.vhd

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity freq_shift_half_cycle is Port ( Bus2IP_Clk : in STD_LOGIC; -- Bus2IP_Reset : in STD_LOGIC; -- Clk_in : in STD_LOGIC; -- Shift_reg : in STD_LOGIC_VECTOR (7 downto 0); -- Bus2IP_Clk counter_reg_test : out STD_LOGIC_VECTOR (7 downto 0); -- Clk_out : out STD_LOGIC -- ); end freq_shift_half_cycle; architecture Behavioral of freq_shift_half_cycle is type state_type is (set_level, wait_high_low, wait_low_high); -- signal current_stage : state_type; signal counter_shift : STD_LOGIC_VECTOR (7 downto 0); -- begin shift_fsm : process (Bus2IP_Reset, Bus2IP_Clk, Clk_in, Shift_reg) begin if Shift_reg = x"00" or Bus2IP_Reset = '1' then -- reset Clk_out <= Clk_in; counter_shift <= x"01"; counter_reg_test <= x"01"; -- current_stage <= set_level; elsif (Bus2IP_Clk'event and Bus2IP_Clk = '1') then case current_stage is when set_level => if counter_shift = Shift_reg then -- , 0 1 if Clk_in = '1' then Clk_out <= '1'; current_stage <= wait_high_low; else Clk_out <= '0'; current_stage <= wait_low_high; end if; counter_shift <= x"01"; counter_reg_test <= x"01"; -- elsif counter_shift < Shift_reg then counter_shift <= counter_shift + 1; counter_reg_test <= counter_shift + 1; -- current_stage <= set_level; end if; when wait_high_low => -- 1 0 set_level if Clk_in = '1' then current_stage <= wait_high_low; else current_stage <= set_level; end if; when wait_low_high => -- 0 1 set_level if Clk_in = '0' then current_stage <= wait_low_high; else current_stage <= set_level; end if; when others => current_stage <= set_level; end case; end if; end process shift_fsm; end Behavioral; Simulation code for Modelsim:

testbench_half_cycle.vhd

LIBRARY ieee; USE ieee.std_logic_1164.ALL; -- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values --USE ieee.numeric_std.ALL; ENTITY testbench_half_cycle IS END testbench_half_cycle; ARCHITECTURE behavior OF testbench_half_cycle IS -- Component Declaration for the Unit Under Test (UUT) COMPONENT freq_shift_half_cycle PORT( Bus2IP_Clk : IN std_logic; Bus2IP_Reset : IN std_logic; Clk_in : IN std_logic; Shift_reg : IN std_logic_vector(7 downto 0); counter_reg_test : OUT std_logic_vector(7 downto 0); Clk_out : OUT std_logic ); END COMPONENT; --Inputs signal Bus2IP_Clk : std_logic := '0'; signal Bus2IP_Reset : std_logic := '0'; signal Clk_in : std_logic := '0'; signal Shift_reg : std_logic_vector(7 downto 0) := (others => '0'); --Outputs signal counter_reg_test : std_logic_vector(7 downto 0); signal Clk_out : std_logic; -- Clock period definitions constant Bus2IP_Clk_period : time := 10 ns; constant Clk_in_period : time := 100 ns; BEGIN -- Instantiate the Unit Under Test (UUT) uut: freq_shift_half_cycle PORT MAP ( Bus2IP_Clk => Bus2IP_Clk, Bus2IP_Reset => Bus2IP_Reset, Clk_in => Clk_in, Shift_reg => Shift_reg, counter_reg_test => counter_reg_test, Clk_out => Clk_out ); -- Clock process definitions Bus2IP_Clk_process :process begin Bus2IP_Clk <= '1'; wait for Bus2IP_Clk_period/2; Bus2IP_Clk <= '0'; wait for Bus2IP_Clk_period/2; end process; Clk_in_process :process begin Clk_in <= '1'; wait for Clk_in_period/2; Clk_in <= '0'; wait for Clk_in_period/2; -- wait for 1000 ns; end process; -- Stimulus process stim_proc: process begin -- hold reset state for 100 ns. Bus2IP_Reset <= '1'; wait for 500 ns; Bus2IP_Reset <= '0'; wait for 5000 ns; Shift_reg <= x"01"; -- wait for 5000 ns; Shift_reg <= x"00"; wait for 5000 ns; Shift_reg <= x"04"; wait for Bus2IP_Clk_period*10; -- insert stimulus here wait; end process; END; An experienced electronics engineer could notice the shortcomings of this code, namely. Exposed delay should not exceed:

- pulse duration, if the pulse duration is less than the pause duration;

- pause duration, if the pause duration is less than the pulse duration.

Those. the value of the phase shift should not exceed 180 ° for both 0 and 1 in the case of a pulse signal.

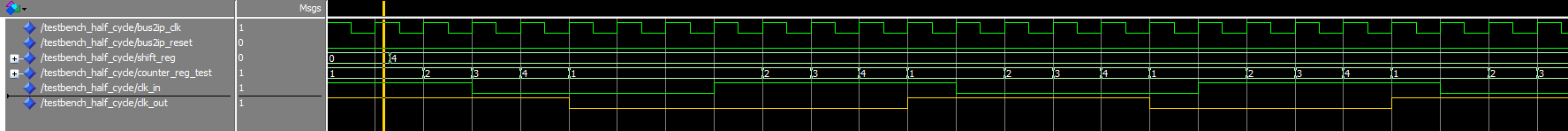

In the diagram below you can see how the phase of the input signal is shifted by 40 ns in real time, so to speak, with a delay in the operation of the logic:

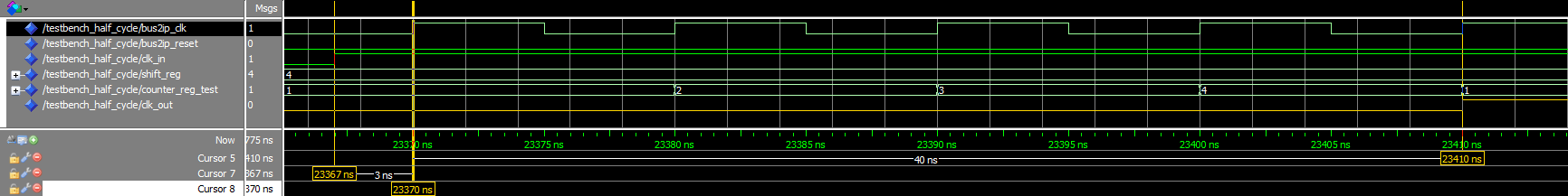

The following is a demonstration of the situation if the tuned signal and the reference frequency are asynchronous:

I suggest you analyze this situation and draw your own conclusions.

I will be glad to your comments and comments, with the help of which in the next article, this code will be supplemented with new functionality.

Thanks for attention.

Source: https://habr.com/ru/post/273851/

All Articles