TKGate - an open-source digital circuit simulator: the project is alive again

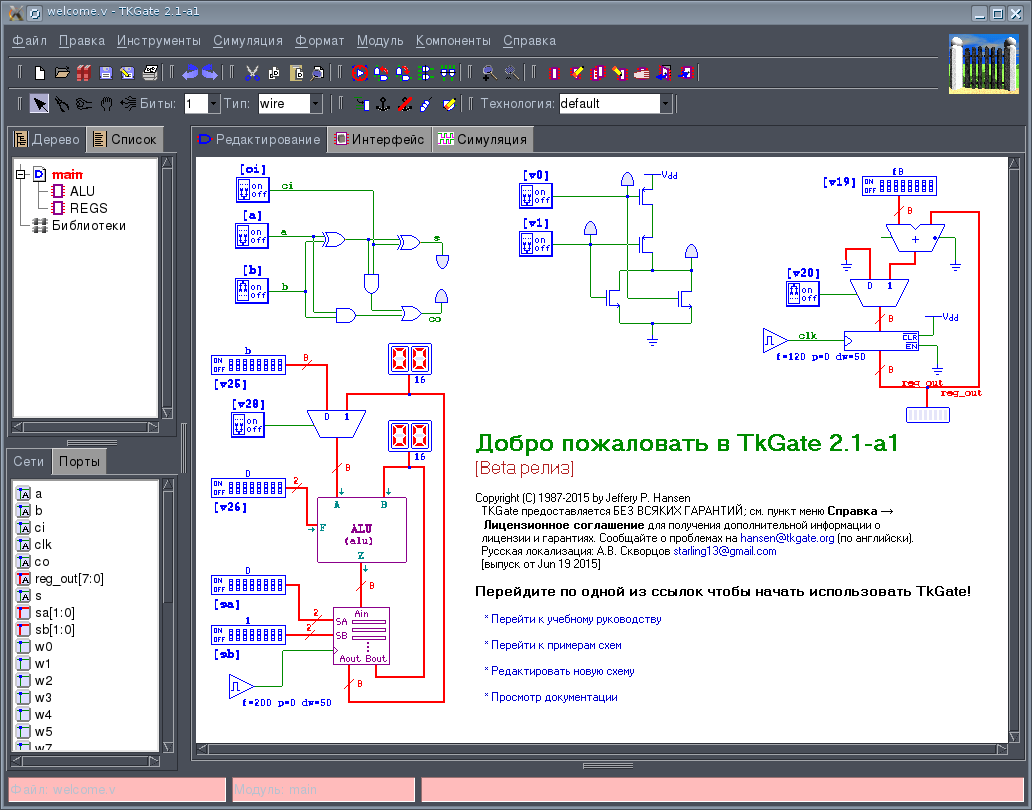

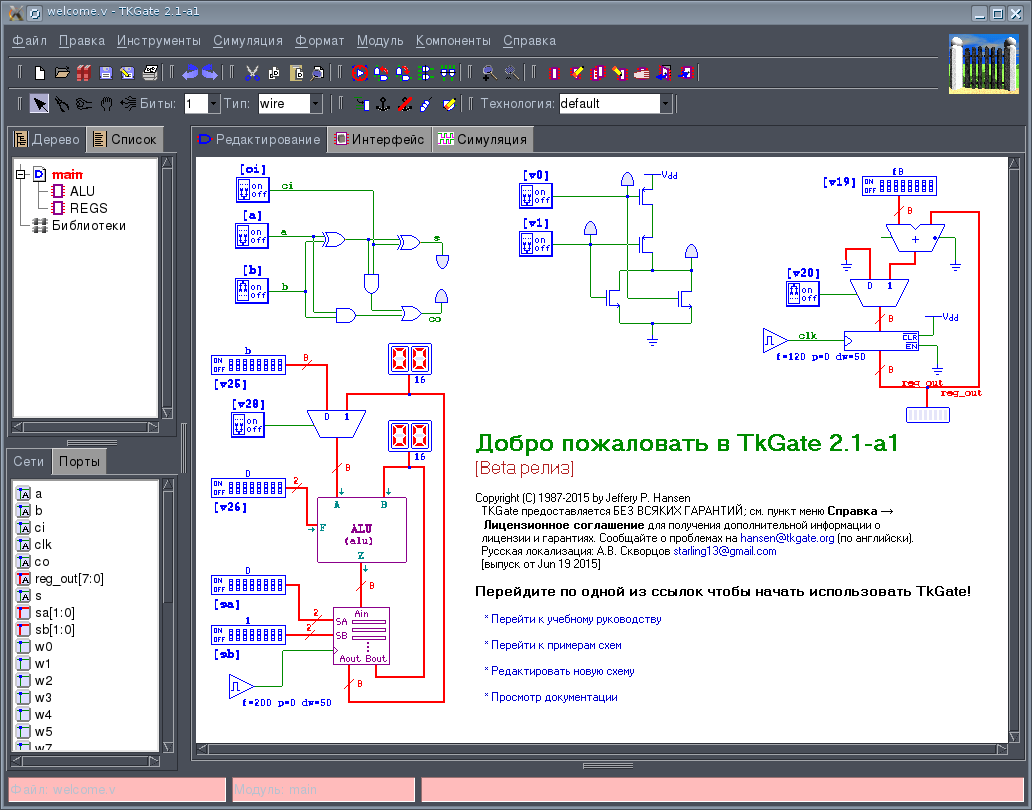

TKGate ( tkgate.org ) is an open source Verilog based digital circuit simulator. It works in Linux OS. The simulator is written in a bunch of C and Tk / Tcl. The author of the project is Jeffery P. Hansen (inactive). Now our compatriot Andrey Skvortsov is engaged in development. Last week, after a six-year (!) Break in development, a new version of the TKGate-2.0 simulator was released. This is what TKGate looks like:

')

Under the cut a more detailed analysis of TKGate.

I used TKGate around 2005-2006, and I have the most positive memories of it. Then around 2009, the development of the project ceased, and I did not have projects with digital electronics, which had to be modeled. From now on, I have not seen this simulator and thought that the project had died. Now, fortunately, there was a developer who raised this project from the dead. Now let's take a closer look at this simulator. Key features of the simulator are as follows:

The schematic file is a regular Verilog script, whose comments contain information about the location of components and wires. This Verilog code, for example, can then be transferred to CAD for the synthesis of FPGAs.

The TKGate GUI is written in Tk / Tcl and therefore for those who are used to modern KDE and Gnome it looks a bit old-fashioned. Nevertheless, this does not harm the functionality of the program.

The simulator works only under Linux, the version for Windows, probably, can be built from the source itself.

The previous version of TKGate-1.8 is in the Debian repository, and to install it, just run the command:

There are no ready packages for the latest version yet, so you need to build it yourself. The following dependencies are required:

You can either download the source archive from the official site or clone the project repository on Bitbucket:

If you took the archive with the source code from the official site, then it should be unpacked in the directory where it was unpacked to run:

If you clone the repository, the build sequence is more complicated:

You can make install to replace checkinstall, which will build the package for your distribution.

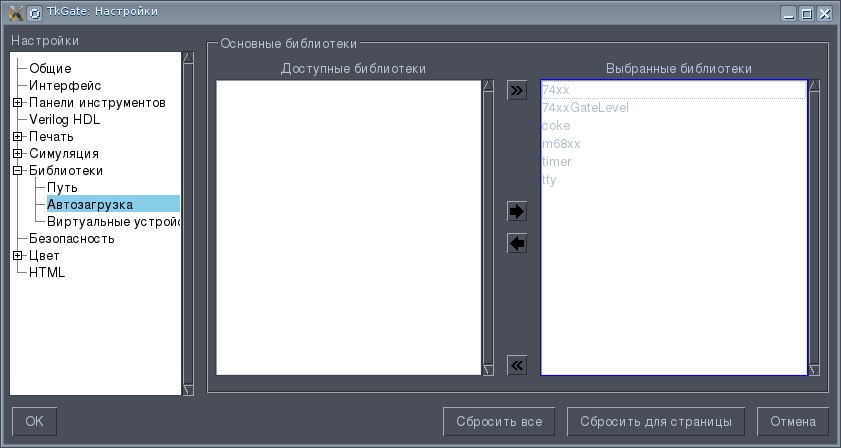

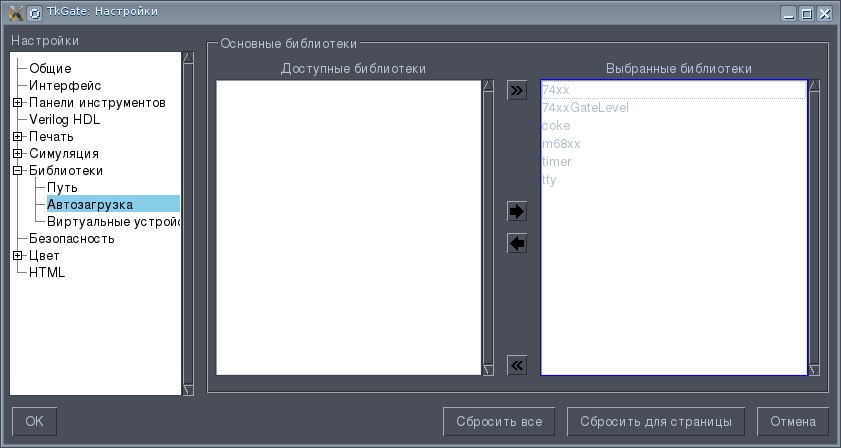

After installation, you need to configure the library loaded at startup. You can download all or some of the libraries. To do this, click in the main menu Tools-> Settings and then in the appeared dialog Library-> Startup. Select the libraries that are loaded at startup. In particular, the program contains the library of the IC of the 74th series (TTL and TTLSH). This completes the setup.

You can dynamically load libraries by clicking the right button on the Libraries item in the project tree in the left part of the program window and selecting the Library Manager item from the context menu.

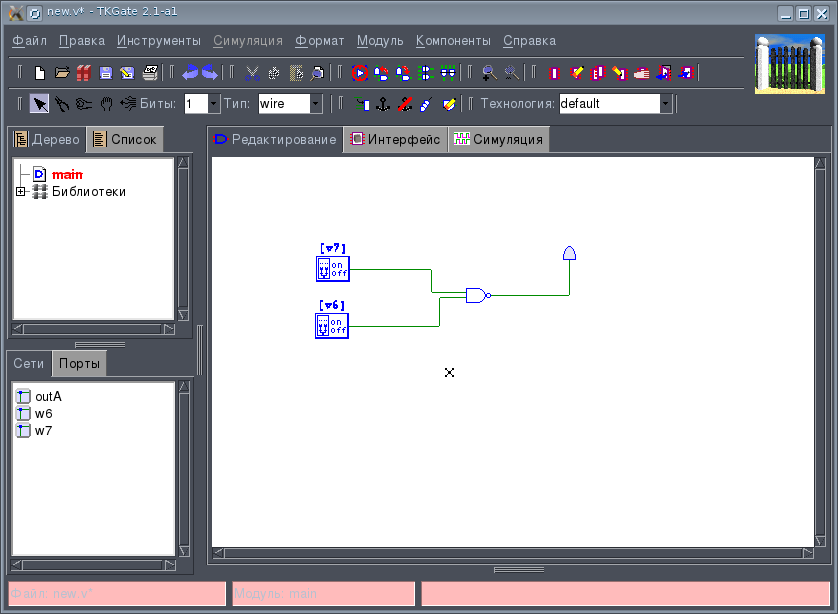

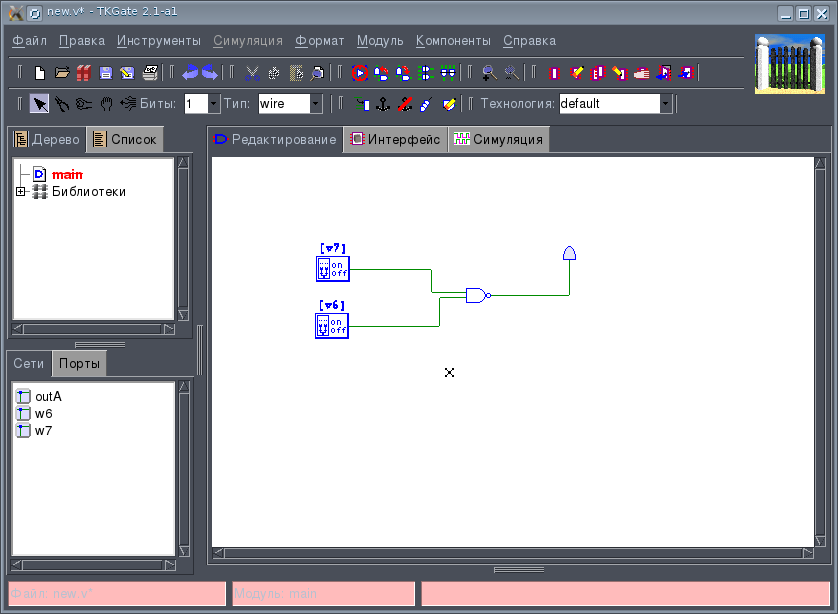

Consider a small example. Let's model the element 2I-NOT. To do this, create a new file: File-> Create.

An empty diagram opens. The central part of the main window of the program is the actual input field of the scheme.

Now you need to add components. Components are added via the context menu.

called by right-clicking on the schema field. Select Components-> Valve-> AND-NOT. To the inputs of the valve, you need to connect switches that will feed them a log.0 or a log.1, and an LED to the output to monitor the status of the 2I-NOT valve. Switches are selected again through the context menu Components-> Input / Output-> Switch. The LED is in the same place: Components-> Input / output-> LED. Now we connect all the wires. It should be such a scheme:

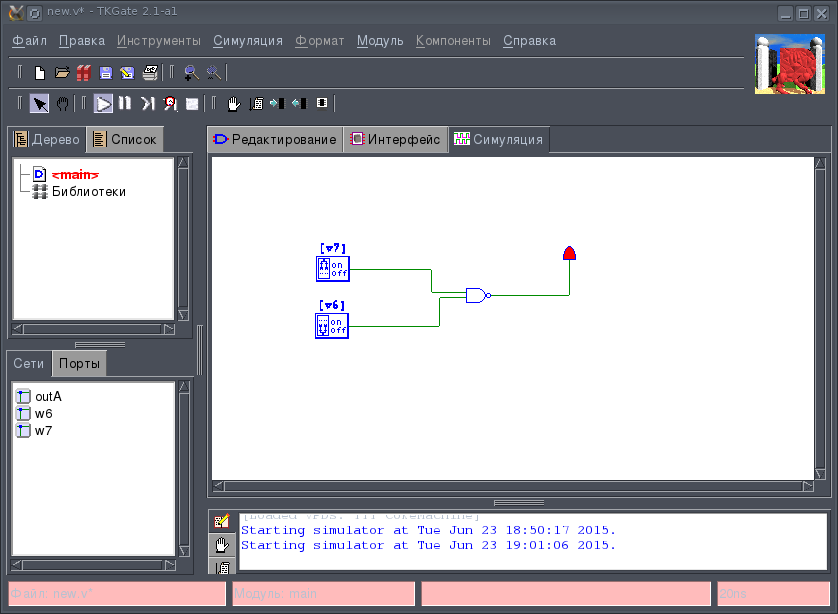

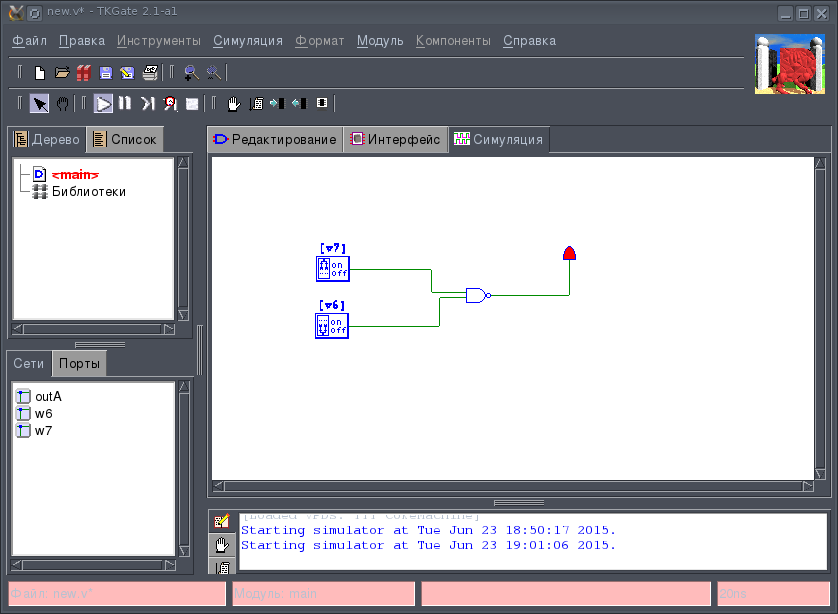

Now the circuit can be modeled. To do this, go to the Simulation tab. The Simulation menu becomes active. Now run the simulation: Simulation-> Start. The simulation is completely interactive, unlike for example the digital circuit modeling in Qucs. The modeling approach in TKGate resembles Multisim or Proteus. During simulation, you can manually change the state of switches, etc. and watch the circuit response. In our scheme, if you click on the switches, you will see that the output state of the logic element varies depending on the state of the inputs according to the truth table of the element 2I-NOT. To stop the simulation, you need to call the command Simulation-> Finish Simulation. The result of the simulation is shown in the figure:

More sophisticated circuits may include medium integration ICs, Verilog modules, RAM, and ROMs.

Thus, we can conclude that despite the break in development and the old-fashioned interface, TKGate is a powerful enough tool for analyzing digital circuits.

- Official site of the project tkgate.org

- Project repository on Bitbucket: bitbucket.org/starling13/tkgate/branch/2.0

')

Under the cut a more detailed analysis of TKGate.

History and main features

I used TKGate around 2005-2006, and I have the most positive memories of it. Then around 2009, the development of the project ceased, and I did not have projects with digital electronics, which had to be modeled. From now on, I have not seen this simulator and thought that the project had died. Now, fortunately, there was a developer who raised this project from the dead. Now let's take a closer look at this simulator. Key features of the simulator are as follows:

- Interactive digital circuit modeling

- Available component types: logic elements, triggers, registers, counters, decoders, multiplexers, RAM, ROM, ALU, keys on a MOS transistor, input signal simulators, LEDs, seven-segment indicators, scales, clock generators.

- Use custom Verilog scripts.

The schematic file is a regular Verilog script, whose comments contain information about the location of components and wires. This Verilog code, for example, can then be transferred to CAD for the synthesis of FPGAs.

The TKGate GUI is written in Tk / Tcl and therefore for those who are used to modern KDE and Gnome it looks a bit old-fashioned. Nevertheless, this does not harm the functionality of the program.

Installation

The simulator works only under Linux, the version for Windows, probably, can be built from the source itself.

The previous version of TKGate-1.8 is in the Debian repository, and to install it, just run the command:

apt-get install tkgate There are no ready packages for the latest version yet, so you need to build it yourself. The following dependencies are required:

- Tk / tcl

- Gcc

- Autotools

You can either download the source archive from the official site or clone the project repository on Bitbucket:

hg clone https://bitbucket.org/starling13/tkgate If you took the archive with the source code from the official site, then it should be unpacked in the directory where it was unpacked to run:

./configure make make install If you clone the repository, the build sequence is more complicated:

./configure aclocal automake make make install You can make install to replace checkinstall, which will build the package for your distribution.

Customization

After installation, you need to configure the library loaded at startup. You can download all or some of the libraries. To do this, click in the main menu Tools-> Settings and then in the appeared dialog Library-> Startup. Select the libraries that are loaded at startup. In particular, the program contains the library of the IC of the 74th series (TTL and TTLSH). This completes the setup.

You can dynamically load libraries by clicking the right button on the Libraries item in the project tree in the left part of the program window and selecting the Library Manager item from the context menu.

Work with the program

Consider a small example. Let's model the element 2I-NOT. To do this, create a new file: File-> Create.

An empty diagram opens. The central part of the main window of the program is the actual input field of the scheme.

Now you need to add components. Components are added via the context menu.

called by right-clicking on the schema field. Select Components-> Valve-> AND-NOT. To the inputs of the valve, you need to connect switches that will feed them a log.0 or a log.1, and an LED to the output to monitor the status of the 2I-NOT valve. Switches are selected again through the context menu Components-> Input / Output-> Switch. The LED is in the same place: Components-> Input / output-> LED. Now we connect all the wires. It should be such a scheme:

Now the circuit can be modeled. To do this, go to the Simulation tab. The Simulation menu becomes active. Now run the simulation: Simulation-> Start. The simulation is completely interactive, unlike for example the digital circuit modeling in Qucs. The modeling approach in TKGate resembles Multisim or Proteus. During simulation, you can manually change the state of switches, etc. and watch the circuit response. In our scheme, if you click on the switches, you will see that the output state of the logic element varies depending on the state of the inputs according to the truth table of the element 2I-NOT. To stop the simulation, you need to call the command Simulation-> Finish Simulation. The result of the simulation is shown in the figure:

More sophisticated circuits may include medium integration ICs, Verilog modules, RAM, and ROMs.

Thus, we can conclude that despite the break in development and the old-fashioned interface, TKGate is a powerful enough tool for analyzing digital circuits.

Source: https://habr.com/ru/post/261005/

All Articles