Squires of microelectronics. Video report from the San Francisco Electronics Design Conference

How can a student or a university researcher not only design a microchip, but also get it in their hands from the factory? After all, the initial payment for the factory production of chips for commercial purposes usually exceeds a million dollars? Fortunately, this path exists for much less money - through an organization called Europractice. I recorded a video interview with its director Carl Das.

How can a student or a university researcher not only design a microchip, but also get it in their hands from the factory? After all, the initial payment for the factory production of chips for commercial purposes usually exceeds a million dollars? Fortunately, this path exists for much less money - through an organization called Europractice. I recorded a video interview with its director Carl Das.And if a student grows up and wants to fill up all the continents with chips designed by his company, but does not know where to start? And to this I have an answer - I also recorded a video interview with Mark Scrivener, director of eSilicon's Semiconductor Manufacturing Services. Mark and I together calculated point by point the expenses and the prime cost of the conventional Russian chip, which will be produced in large volumes in 2016-2020.

I recorded these and other videos at the Design Automation Conference (DAC) last week in San Francisco. The DAC conference focuses on the Electronic Design Automation (EDA) industry, which serves chip designers. Among the people I interviewed last week were Verilog hardware description guru John Sanguinetti, heads of companies that develop software tools for chip developers, developers of FPGA circuit boards, one of the founders of the Zelenograd chip design company Alexander Galitsky, and other professionals and businessmen .

')

So:

First, a video interview with Carl Das, who is the Director of ASIC Services at IMEC, who is responsible for the Emerging Business Program with TSMC and the Europractice IC Service. Deciphering what it means:

ASIC - Application-specific integrated circuit, a specialized microcircuit, for example, which stands in an iPhone.

IMEC - Interuniversity Microelectronics Center is an interuniversity center for research in the field of microelectronics, which employs about 2,000 people. Located in Belgium and the Netherlands, with offices in other countries.

Emerging Business Program - when a new company needs to try to release chips in small quantities.

TSMC - Taiwan Semiconductor Manufacturing Company - the world's largest IC chip maker

Europractice IC Service is a special service for university services, which, for relatively small money (thousands of euros instead of hundreds of thousands), provides access to legally licensed software for the development of microchips and, again, for comparatively little money (tens of thousands of euros instead of millions) to the production of microchips at the factory.

And now a video interview with Mark Scrivener, Director SMS Sales, eSilicon

SMS is Semiconductor Manufacturing Services - semiconductor manufacturing services

eSilicon is a company that at the beginning of the XXI century became the pioneer of a new business model - services on various physical aspects of chip design, integration with blocks from various designers and interaction with factories. This company became famous after they made ASIC for iPad.

In short, if you designed a new microprocessor or DSP at the logical level, verified its functionality on the simulator, determined that it fits into the timing budget after synthesis, and you do not want to bother with the physical aspects of chip design (place & route, parasitics extraction, design rule check), and also if you want to minimize the proceedings with lawyers in other countries, how to license different IP blocks, and if you do not really like communicating with factories in Taiwan or in Dresden directly - then eSilicon is for you.

In the video, Mark demonstrates how any Russian schoolchild can register with them on the site and enter the parameters of the chip he is going to produce (how many nanometers, what size, does it have SRAM and the analog part), which tester at the factory to use and the testing time , and also plans on release in different years - 100,000 in the first year, 500,000 in the second, etc.

After that, the website will think and generate a PDF file on many pages, where all expenses and cost of the chip are described in detail. In particular, you can estimate the cost with which you can produce some hypothetical future Russian chips.

And the most interesting - this PDF file is a legally binding quote, i.e. if a schoolchild playing with a site has a couple of million dollars in pocket money for a down payment and a desire to produce a chip, then eSilicon has a legal obligation to give him this opportunity at a published price:

www.esilicon.com/asic-design-services/star-online-tools/gdsii-quoting-portal

The Europractice counterpart in the USA is MOSIS, and eSilicon is a competitor in particular Open-Silicon.

So far we have discussed the culmination of the microelectronic project - the manufacture of microchips in the factory. But how does such a project start?

In the past 25 years, chip design has most often been written in the Verilog hardware description language (in Europe and in the military - VHDL), after which a special program (logic synthesis) turns the design into a graph from wires and logical primitives, another program (timing analysis) reports to the designer, whether it fits into the budget of speed, and the third program (place-and-route) lays out this design on the chip site.

When the design goes through all the stages: coding on the chain, debugging, verification, synthesis, static timing analysis, floorplanning, place-n-route, parasitics extraction, etc. - it turns out a file called GDSII, which is sent to the factory, and the factory bakes chips. The most famous factories of this type are owned by Taiwan Semiconductor Manufacturing Company or TSMC.

I interviewed a man who is about the same language for Verilog as for Keriugan and Richie. John Sanguinetti is the early guru of the veralog from the 1980s, the founder of the company Chronologic Simulation, who presented the world with the fast simulator of the veilog of VCS (Verilog Compiled code Simulator), which most developers of large chips now use. John greeted Russian young people who study Verilog and expressed a few thoughts about high-level synthesis and its applicability to the development of out-of-order processors:

Will high-level synthesis apply to the development of out-of-order processors?

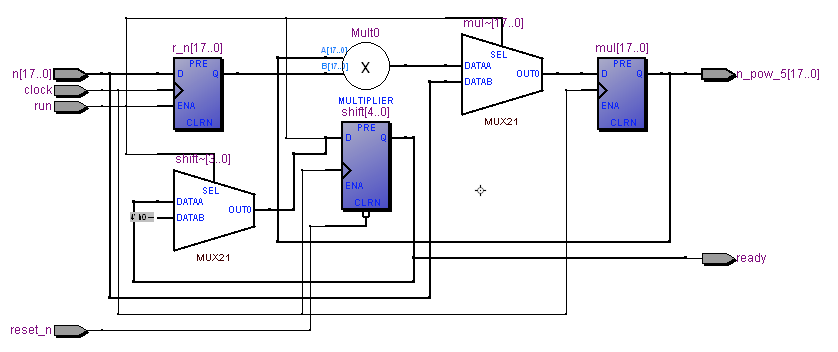

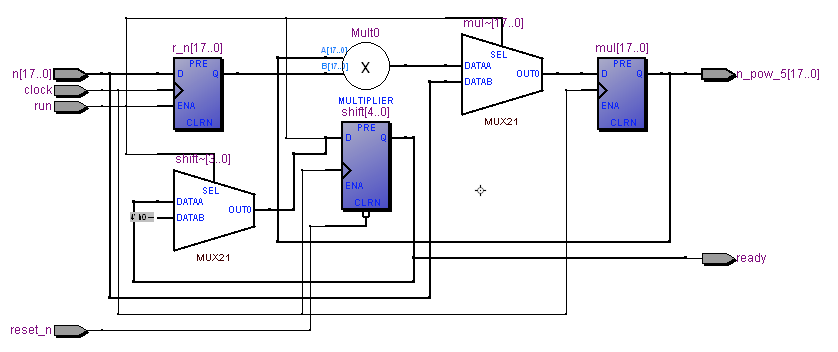

For those readers who do not know what Verilog looks like, I quote one of the examples I wrote for the students, along with the scheme into which it is translated (“synthesized”):

module pow_5_implementation_3

(

input clock,

input reset_n,

input run,

input [17: 0] n,

output ready

output [17: 0] n_pow_5

);

reg [4: 0] shift;

always @ (posedge clock or negedge reset_n)

if (! reset_n)

shift <= 0;

else if (run)

shift <= 5'b10000;

else

shift <= shift >> 1;

assign ready = shift [0];

reg [17: 0] r_n, mul;

always @ (posedge clock)

if (run)

begin

r_n <= n;

mul <= n;

end

else

begin

mul <= mul * r_n;

end

assign n_pow_5 = mul;

endmodule

At the conference they sold books on the verilog:

But the booth of the company Doulos Training which teaches engineers of different companies with languages Verilog and VHDL, verification and related technologies for money. This company has several competitors, in particular Willamette HDL and Sutherland HDL:

I also met the chiefs of the verification department at Synopsys, this group now supports the VCS simulator.

The head of the department is Manoj Gandhi (left), Executive Vice President and General Manager, Verification Group, and on the right is Jayant Nagda, he was the Manager of SystemVerilog implementation at VCS in the early 2000s:

Synopsys had a big booth at the exhibition, one of the three major companies in the electronics software industry, two other members of the trinity are Cadence and Mentor Graphics:

Cadence is the # 2 company in EDA. In December last year, they conducted seminars in Moscow, more precisely at MEPhI:

At the Cadence stand, they demonstrated a new synthesis tool called the Cadence Genus - apparently a competitor to the Synopsys Design Compiler - the main tool for logical synthesis used by the developers of ASICs:

Mentor Graphics is the number 3 company in EDA. Back in 1996, I attached one group at MIPT to do projects for Mentor Graphics right from Dolgoprudny:

In addition to the three large companies in the EDA industry, there are smaller players who exploit their niches. One of these players is the company SILVACO, which develops programs for the physical part of the development of ASIC - modeling at the physical level, checking design rules, finding any parasitic effects at the nano level. (This stage begins after the development of design at a logical level). Several Russians work in SILVACO, in particular, Aleksey Zharikov (in the video below left) and Gayar Usmanov (on the right).

We talked about the following topics:

1. Is it possible to arrange startups in Russia in the field of the physical part of the development of microchips?

2. What happens in Belarus (Integral plant as a supplier of personnel for the EDA industry).

3. Does having a local fab contribute to the emergence of EDA companies?

After that, I spoke with the company's head (chairman of the board) Iliya Pesic, SILVACO Chairman of the Board, he told me that they are expanding to Eastern Europe and working closely with the factories from which they receive the PDK (Process Design Kit) development tools to support production at this factory):

I have been participating in DAC conferences since 1996 and I notice when certain topics become fashionable. Current fashion - increased interest in the FPGA / FPGA theme. Moreover, this topic is popular this year not only on the DAC, but also among non-technical media - in connection with the purchase of Intel FPGA development company called Altera. For $ 16.7 billion dollars!

When in March there were rumors on the Intel-Altera deal on the Internet, many journalists simply did not understand what the company was doing, for which Intel decided to pay such big money. One conjectured that Altera allegedly "Intel's main processor competitor" (despite the fact that Alter's FPGAs are not processors at all, although the processor can stand next to reconfigurable gates), the other one that Altera is allegedly "a manufacturer of telecommunications equipment" (no telecommunications equipment Altera does not produce), the third is that Altera is allegedly a "contract manufacturer of microcircuits" aki TSMC (despite the fact that Altera does not have its own factories).

What is FPGA / FPGA I explained on the fingers in another post on Habré - How to start developing iron using FPGA - step by step instructions . But we repeat this information again:

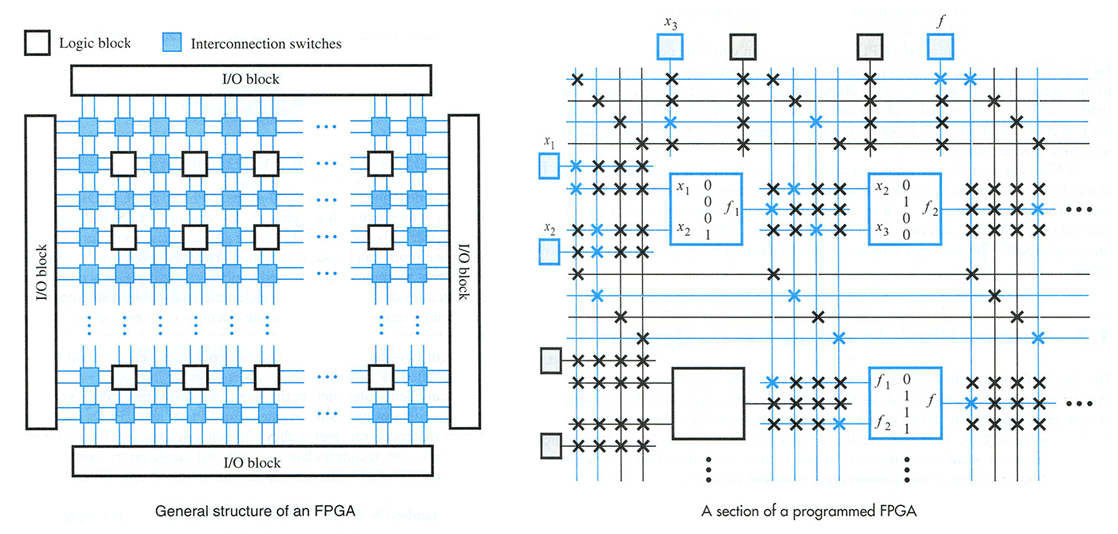

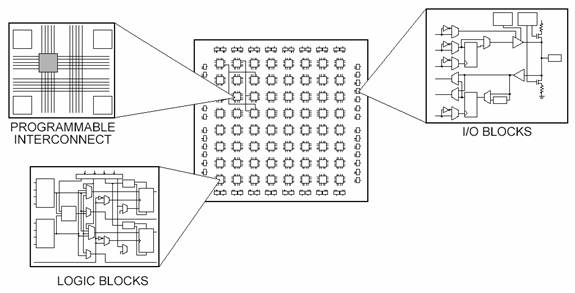

In its simplest form, an FPGA consists of a matrix of homogeneous cells, each function of which can be changed using multiplexers connected to the bits of the configuration memory. One cell can become AND gate with four inputs and one output, the other one single-bit register, etc. We load into the configuration memory a sequence of bits from the memory — and a predetermined electronic circuit is formed in the FPGA, which can be a processor, a display controller, etc.

FPGAs / FPGAs are not processors, “programming” the FPGAs (filling in the FPGA configuration memory) you create an electronic circuit (hardware), while programming a processor (fixed hardware) you slip a chain of sequential instructions written into the memory (software).

Below is a diagram of the simplest FPGA block, which includes a look-up table (LUT) and flip-flop. True, this scheme does not show multiplexers that change the function of the cell, and connections to the configuration memory.

Diagrams illustrating FPGA structure:

And another one:

In my previous posts about FPGAs ( 1 , 2 ), I wrote about student FPGA boards for $ 80- $ 150- $ 300, and now we will look at manufacturers of "adult" boards with prices from $ 5,000 to $ 50,000 and higher, with fast and large Xilinx Virtex- 7 FPGA. These boards are used by ASIC developers for prototyping:

Company from Germany proFPGA:

Company from Southern California Dini Group:

Company from Northern California S2C:

But large FPGA boards are not new to me - back in the 20th century, I participated in the FCCM conference (IEEE Symposium on Field-Programmable Custom Computing Machines) in Wine Country, where a third of the people were university researchers, a third were big FPGA boards and a third - comrades from the army and the CIA, who used these boards for their secret needs (decoding, signal processing, etc. - see ieeexplore.ieee.org/xpl/mostRecentIssue.jsp?punumber=5734&filter%3DAND% 28p_IS_Number% 3A15334% 29 & pageNumber = 3 )

But what was new to me this year was the large number of new companies that sell in the form of intellectual property (semiconductor IP), the design of blocks of FPGA cells that can be placed on the ASIC. Here is one such company from France, Menta:

Here is another one, flexlogix from Silicon Valley:

And one more - the French ADICSYS, whose founder, Peer Schmitt, I took a video interview, why all this is necessary. It turns out that one of the reasons for using FPGA on ASIC is that (!) The chip designer can conceal the most secret part of the circuit from the factory (!) Type 95% of the chip is unclassified, and the secret state machine is stitched after production, when the warm chip comes back with Taiwan to Zelenograd:

Then I met a group of Russian defilers , including Vlad and Elena Potanin, the founders of Viveng , which deals with services to analog and mixed-signal (digital and analog) design. The company is located in Silicon Valley, before it Potanins worked at Texas Instruments, National Semiconductor, Zilog, at Angstrom, studied at MEPI and MIET-e.

Potanin was joined by Alexander Kotov, a flash memory specialist from Silicon Storage Technologies , who was bought a few years ago by Microchip Technology, a microcontroller manufacturer. “Oh, another Russian microchip!” I exclaimed, for I know the microchip well, I even gave a talk at their conference in St. Petersburg .

We talked about translating the textbook of Harris & Harris into Russian, which is distributed free of charge, and about the fate of Russia.

And a little about the relevance of analog design - both in general and for Russia in particular:

And here is another Russian project on DAC, the Black Swift board designed in Russia at the stand of Imagination Technologies. The board itself is small black, it stands on a large demo:

I also met Fumiko Suzuki, a consultant on the Japanese e-market, who again shared a translation of the Harris & Harris textbook into Russian, which is distributed free of charge. I also told that X & X was also translated into Japanese and mentioned critics who claim that Russians should read such textbooks only in English.

Fumiko’s response to the question of whether Harris & Harris translate correctly: “Of course, of course. When you read in your own language, you learn more. When you get used to it, you can read in English, but in any case it’s a great book. ”

Chinese Mannie Wright, engineering application manager, also believes that difficult-to-read texts for young students can be better read Chinese (Harris & Harris also translated into Chinese):

But the opinion of Link Jepson, an American born in the United States, who learned Russian from his sports interest and lived a life of a Russian engineer in Zelenograd for a year and a half. Link is the verification engineer (SystemVerilog, UVM) of the chip that does ray-tracing to generate realistic three-dimensional images:

In Russian: “the main thing is to make cool chips, something useful [and the language is secondary]”:

In English about Harris & Harris:

But I met Link, unlike all the listed comrades, not at the DAC, but at a conference called Silicon Valley Open Doors, SVOD, which was held simultaneously with the DAC conference, but not in San Francisco, but 60 kilometers south , in the Museum of Computer History in Mountain View. As you can guess from the title (“Code”), this is a conference that brings together Russian startups and American investors.

I went to SVOD to randomly catch someone who is related to Russian electronics, and at the same time take a look at business Russian girls who usually hang out at such conferences. The girls were immediately found in the person of Anna Degtereva, one of the organizers of UTGEM'14, the Ukrainian high-tech conference, which I described in panchul.livejournal.com/390486.html .

Anna confirmed my observation that this year a lot more people arrived at the Code than last year:

People from Russian electronics, in the person of Alexander Galitsky, a man with the following biography , were found rather quickly: MIET, MIPT, Zelenograd, ELAS, on-board computer of the Salyut space station, agreement with Sun Microsystems, participation in the founding of NPO ELVIS and ELVIS-PLUS company , venture fund Almaz Capital .

I asked the opinion of Alexander Galitsky on the following questions:

1. Why is cooperation between Imagination Technologies and the ELVIS group of companies significant? Imagination Technologies is best known as the developer of the PowerVR graphics processor inside the Apple iPhone, as well as the licensee of the MIPS processor cores. The ELVIS group of companies is known as the developer of space microelectronics and "smart cameras", which are used in particular to ensure the security of Sheremetyevo Airport.

2. How to improve the education of young Russian engineers in the field of microelectronics?

3. How can I use the Russian factories Micron and Angstrom in Zelenograd?

4. How to bring the chips, designed in Russia, to the world market?

Then Alexander Galitsky went to the stage to perform, and I drank coffee and went home to write this post:

Source: https://habr.com/ru/post/260069/

All Articles