Industrial processor sources will be available for universities.

Lord The other day, Imagination Technologies (the company that designed the PowerVR GPU graphics processor inside the Apple iPhone) and Xilinx (No. 1 company in FPGA) launched a bit of an iconoclastic initiative to give universities the sources of the modern MIPS microAptiv UP industrial core, which is used for example in the Microchip PIC32MZ microcontroller. Students will be able to change the commands of this processor, add their peripheral devices to it and implement the resulting design on the FPGAs.

Here is a link to a seminar report on May 13-14 near Los Angeles, where Imagination and Xilinx will show a new product called MIPSfpga to representatives of academia - imgtec.com/mipsfpga

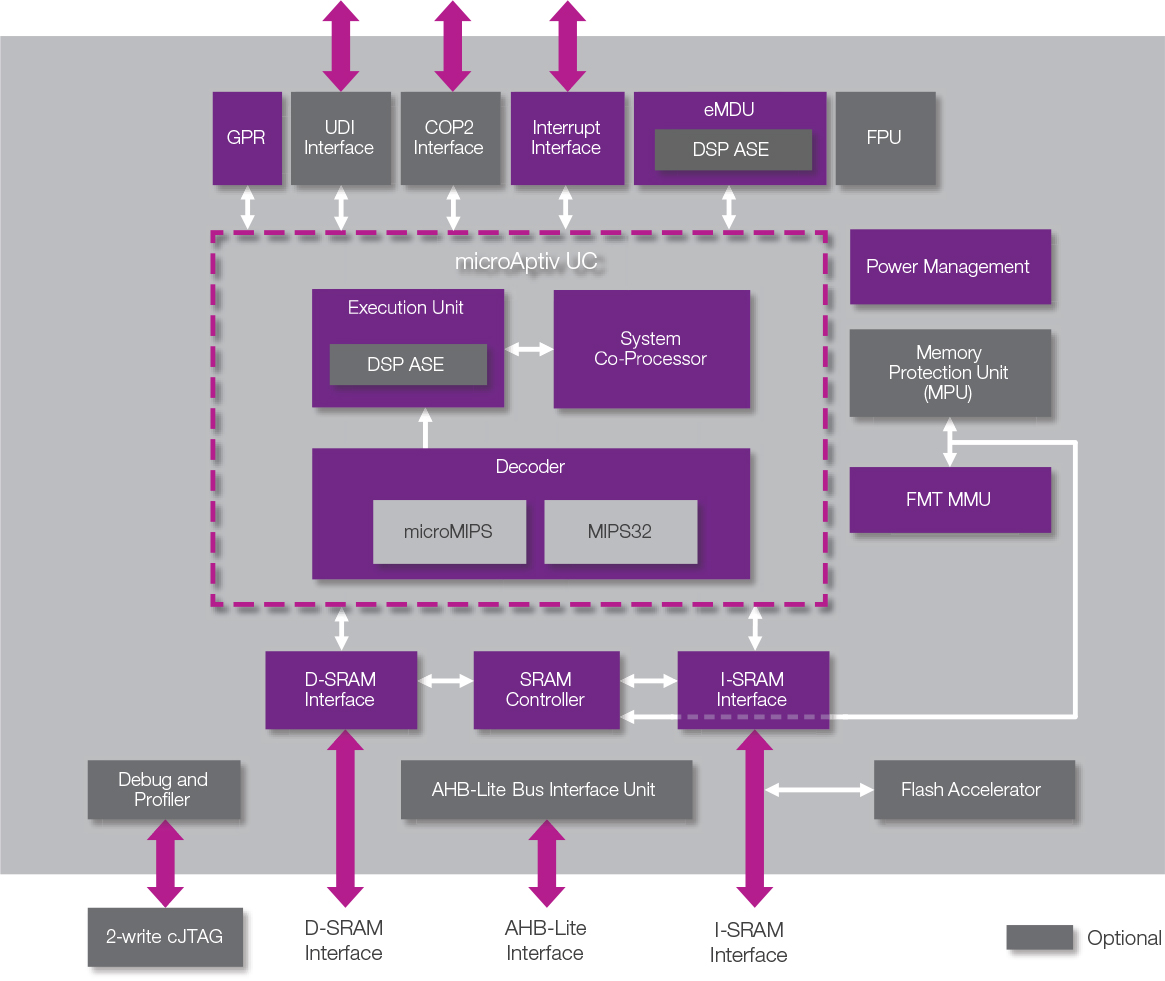

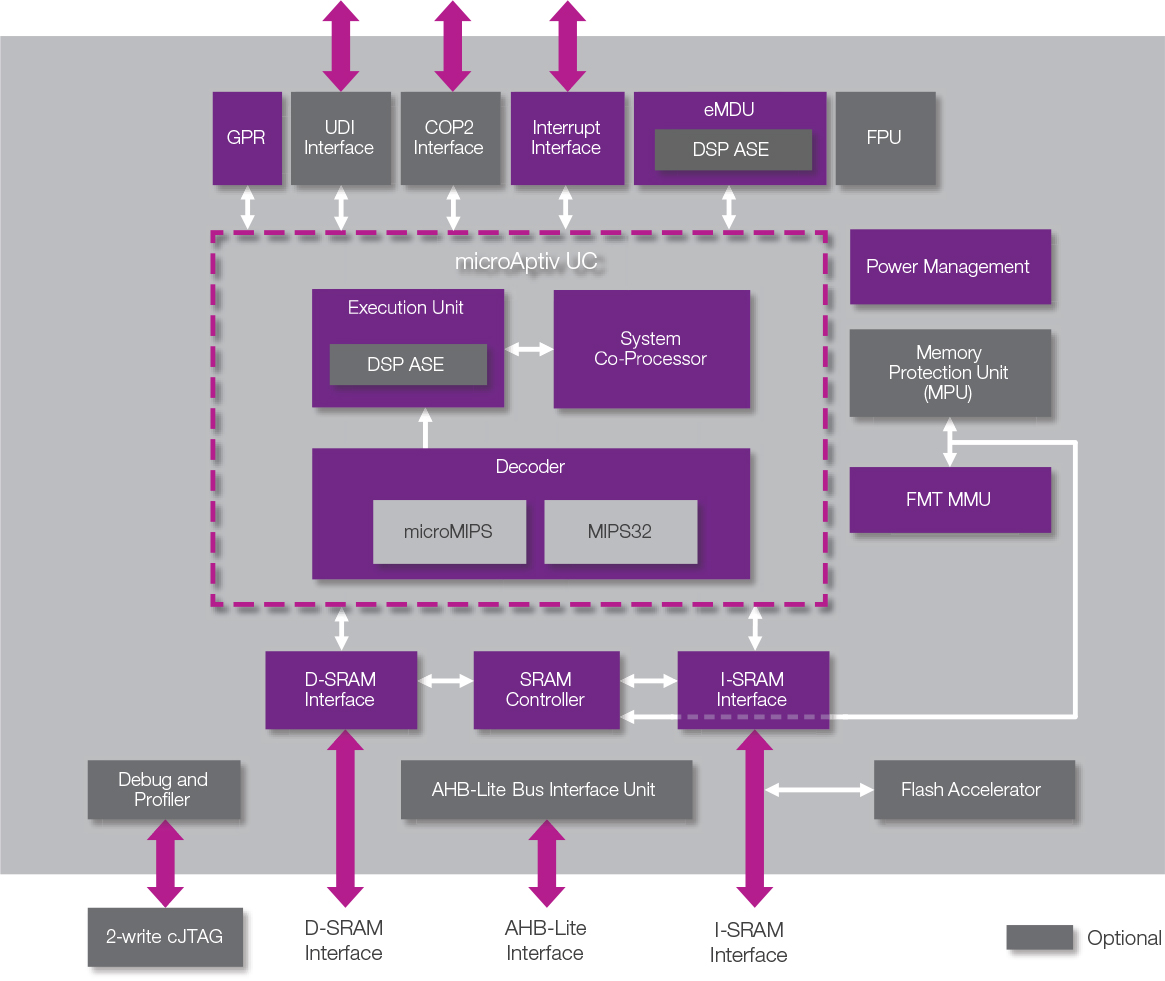

In fact, MIPSfpga is a free license for the basic configuration of the economical MIPS microAptiv UP processor core, which is provided in the source code in the Verilog hardware description language. This is the same core that is sold to commercial customers for hundreds of thousands of dollars. MIPS microAptiv UP is a simple design with five stages of a serial pipeline (as in computer architecture textbooks), but it has caches and TLB MMUs. TLB MMU allows you to even use Linux on it.

')

Kernel Description: www.imgtec.com/mips/aptiv/microaptiv.asp

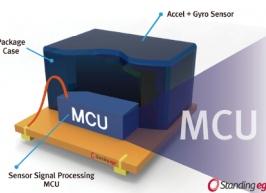

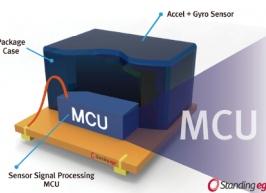

The most widely known example of using the MIPS microAptiv UP kernel is the Microchip PIC32MZ 32-bit microcontroller, which was launched last year. And from the most recent examples of use: On April 10, the Electronic Engineering Times published an article about the South Korean start-up Standing Egg, which licensed the MIPS M5100 core (actually MIPS microAptiv without caches and MMU, but with an added extension for virtualization) to create a platform for MEMS sensors, With applications for Internet of Things:

www.eetimes.com/document.asp?doc_id=1326327

Microchip developers with MIPS microAptiv UP use the standard for the last 20 years electronic design methodology called Register Transfer Level (RTL, register transfer level). According to this methodology, a design is written in Verilog, after which a special program (logic synthesis) turns the design into a graph of wires and logic elements, another program (static timing analysis) informs the developer whether it fits into the speed budget, and the third program (place -and-route) lays out this design on the chip site.

When the design goes through all the stages: coding on the chain, debugging, verification, synthesis, static timing analysis, floorplanning, place-n-route, parasitics extraction, etc. - it turns out a file called GDSII, which is sent to the factory, where the chips are made. The most famous factories of this type are owned by Taiwan Semiconductor Manufacturing Company or TSMC. At the same time, nothing prevents the production of microcircuits with the MIPS microAptiv UP core in the Russian factories Mikron and Angstrom.

An alternative to manufacturing a chip in a factory is to implement a design on user-programmable arrays of logic elements (Field Programmable Gate Array - FPGA), which is used for educational purposes in the new MIPSfpga product.

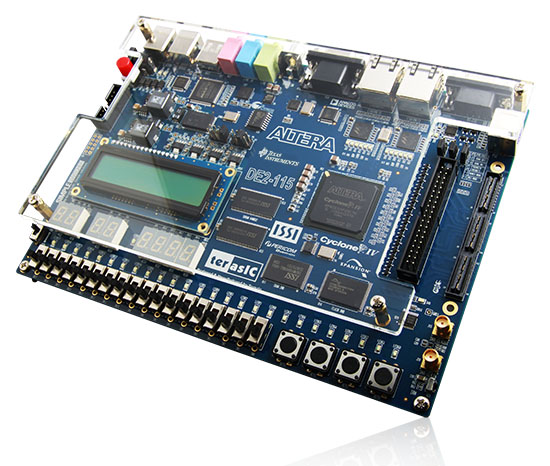

Although the MIPSfpga package is sharpened for synthesis for FPGA (for example, MIPSfpga has a memory implementation inside the caches, using macros for Xilinx Artix-7 and Altera Cyclone IV), but basically these are the same sources that are used for synthesis in ASIC. In other words, undergraduate and graduate students can experiment with the core on low-cost FPGA boards, come up with some interesting solution (say, a multi-core SoC from small incoherent cores, or a combination of the MIPS microAptiv UP core with a specialized student DSP processor) without investing money investors, after which, when the idea is proven, find investors, purchase a commercial license and make a microchip at the factory - ASIC.

I note that in the case of MIPSfpga, this is not about a limited educational subset of MIPS (there are quite a lot of such subsets from other sources) and not about an open-source core like OpenRISC or Leon4, but about a commercially successful modern industrial core that licensed several for the money dozens of companies.

The competing company ARM also has a soft core for educational experimentation on FPGAs, but their core is not in open source (i.e., students cannot connect wires to internal registers and modify the verilo), the ARM core ARM Cortex M0 in the competing The product has no caches, debugger interface and TLB MMU. MIPSfpga has all this.

Additional details:

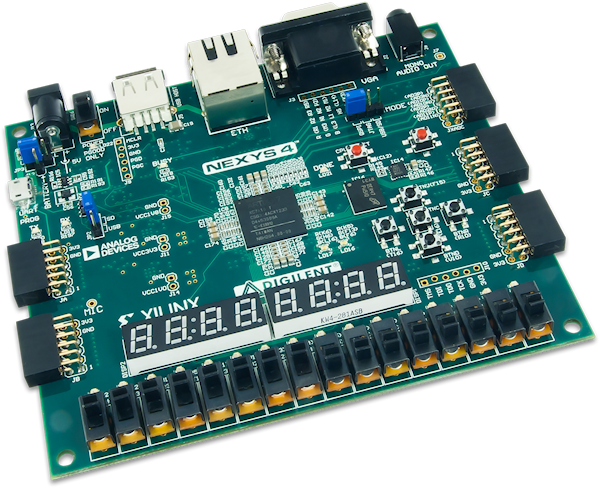

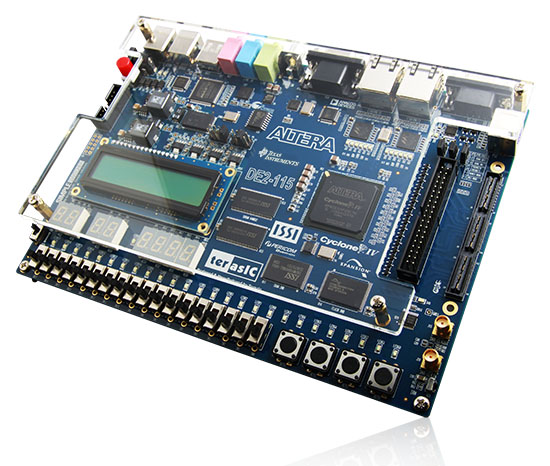

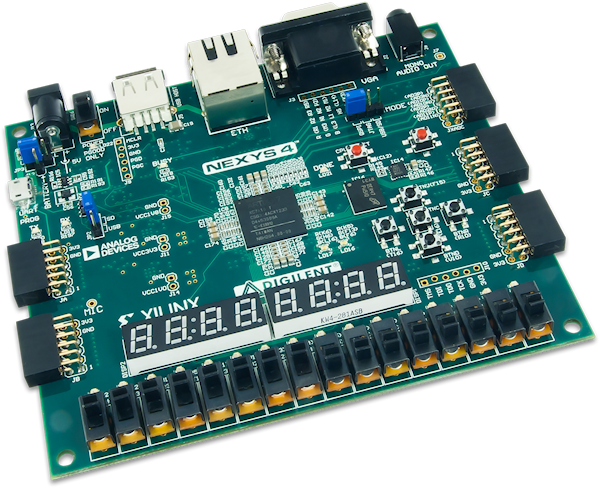

Now MIPSfpga runs on two Digilent Nexys-4 boards with Xilinx Artix-7 and Altera DE2-115 with Cyclone IV E. The first one has an academic price of $ 180 / commercial, $ 320, and the second has an academic price of $ 300 / commercial, $ 600. It is quite easy to transfer it to other boards (provided that it fits together) - you need to replace some of the memory macros and connect the top-module to the board-specific external verilog wrapper. In particular, you can try to transfer it to a cheap Digilent Basys-3 board from Xilinx Artix-7 (academic $ 80 / commercial $ 150), as well as to boards that are designed or manufactured in Russia.

As a toolchain, the Codescape MIPS SDK is offered, which contains a debugger and the GCC toolchain. The connection between the debugger and the Nexys-4 board is done using EJTAG, BusBlaster probe and OpenOCD. On the Altera DE2 115 a debugging interface is used which stands directly on the board, i.e. BusBlaster is not needed. Also included is a boot code in an assembler that initializes caches and the MMU, etc.

Now what can this have to do with you:

1. The first stage of testing MIPSfpga at three universities in the US and UK has been successfully completed. Now the product will be beta tested in a large number of universities in the United States, Europe and Asia. If you work at a university and have sufficient expertise in Verilog or VHDL to work with the package, then you can participate as an early adopter and gain an advantage over other universities in its use.

2. On May 13-14, a seminar organized by Imagination Technologies with Xilinx will take place in Los Angeles, where Harvey Mudd College professors and application engineers from Imagination will train professors from various universities to use MIPSfpga. If you or any of your familiar Universitetle teachers want to participate in it and can come to Los Angeles at this time, please contact either the educational program manager Robert Owen (his coordinates at imgtec.com/mipsfpga ) or me ( yuri.panchul@imgtec.com).

3. By the time of the workshop in Los Angeles, MIPSfpga will be officially announced, and upon completion (1) will be made publicly available. Therefore, if you do not have the opportunity to participate as an early adopter, you can nevertheless be able to start working with the product in the summer.

The ability to use industrial processor cores on the chain for educational purposes and without buying a commercial license will allow a large number of young developers in the academia to prototype innovative solutions in the field of on-chip systems and microarchitecture extensions, with the direct path to commercialization - creating their own chips for the Internet of things and others applications.

Yuri Panchul

Senior Hardware Design Engineer, MIPS processors

Imagination Technologies

Here is a link to a seminar report on May 13-14 near Los Angeles, where Imagination and Xilinx will show a new product called MIPSfpga to representatives of academia - imgtec.com/mipsfpga

In fact, MIPSfpga is a free license for the basic configuration of the economical MIPS microAptiv UP processor core, which is provided in the source code in the Verilog hardware description language. This is the same core that is sold to commercial customers for hundreds of thousands of dollars. MIPS microAptiv UP is a simple design with five stages of a serial pipeline (as in computer architecture textbooks), but it has caches and TLB MMUs. TLB MMU allows you to even use Linux on it.

')

Kernel Description: www.imgtec.com/mips/aptiv/microaptiv.asp

The most widely known example of using the MIPS microAptiv UP kernel is the Microchip PIC32MZ 32-bit microcontroller, which was launched last year. And from the most recent examples of use: On April 10, the Electronic Engineering Times published an article about the South Korean start-up Standing Egg, which licensed the MIPS M5100 core (actually MIPS microAptiv without caches and MMU, but with an added extension for virtualization) to create a platform for MEMS sensors, With applications for Internet of Things:

www.eetimes.com/document.asp?doc_id=1326327

Microchip developers with MIPS microAptiv UP use the standard for the last 20 years electronic design methodology called Register Transfer Level (RTL, register transfer level). According to this methodology, a design is written in Verilog, after which a special program (logic synthesis) turns the design into a graph of wires and logic elements, another program (static timing analysis) informs the developer whether it fits into the speed budget, and the third program (place -and-route) lays out this design on the chip site.

When the design goes through all the stages: coding on the chain, debugging, verification, synthesis, static timing analysis, floorplanning, place-n-route, parasitics extraction, etc. - it turns out a file called GDSII, which is sent to the factory, where the chips are made. The most famous factories of this type are owned by Taiwan Semiconductor Manufacturing Company or TSMC. At the same time, nothing prevents the production of microcircuits with the MIPS microAptiv UP core in the Russian factories Mikron and Angstrom.

An alternative to manufacturing a chip in a factory is to implement a design on user-programmable arrays of logic elements (Field Programmable Gate Array - FPGA), which is used for educational purposes in the new MIPSfpga product.

Although the MIPSfpga package is sharpened for synthesis for FPGA (for example, MIPSfpga has a memory implementation inside the caches, using macros for Xilinx Artix-7 and Altera Cyclone IV), but basically these are the same sources that are used for synthesis in ASIC. In other words, undergraduate and graduate students can experiment with the core on low-cost FPGA boards, come up with some interesting solution (say, a multi-core SoC from small incoherent cores, or a combination of the MIPS microAptiv UP core with a specialized student DSP processor) without investing money investors, after which, when the idea is proven, find investors, purchase a commercial license and make a microchip at the factory - ASIC.

I note that in the case of MIPSfpga, this is not about a limited educational subset of MIPS (there are quite a lot of such subsets from other sources) and not about an open-source core like OpenRISC or Leon4, but about a commercially successful modern industrial core that licensed several for the money dozens of companies.

The competing company ARM also has a soft core for educational experimentation on FPGAs, but their core is not in open source (i.e., students cannot connect wires to internal registers and modify the verilo), the ARM core ARM Cortex M0 in the competing The product has no caches, debugger interface and TLB MMU. MIPSfpga has all this.

Additional details:

Now MIPSfpga runs on two Digilent Nexys-4 boards with Xilinx Artix-7 and Altera DE2-115 with Cyclone IV E. The first one has an academic price of $ 180 / commercial, $ 320, and the second has an academic price of $ 300 / commercial, $ 600. It is quite easy to transfer it to other boards (provided that it fits together) - you need to replace some of the memory macros and connect the top-module to the board-specific external verilog wrapper. In particular, you can try to transfer it to a cheap Digilent Basys-3 board from Xilinx Artix-7 (academic $ 80 / commercial $ 150), as well as to boards that are designed or manufactured in Russia.

As a toolchain, the Codescape MIPS SDK is offered, which contains a debugger and the GCC toolchain. The connection between the debugger and the Nexys-4 board is done using EJTAG, BusBlaster probe and OpenOCD. On the Altera DE2 115 a debugging interface is used which stands directly on the board, i.e. BusBlaster is not needed. Also included is a boot code in an assembler that initializes caches and the MMU, etc.

Now what can this have to do with you:

1. The first stage of testing MIPSfpga at three universities in the US and UK has been successfully completed. Now the product will be beta tested in a large number of universities in the United States, Europe and Asia. If you work at a university and have sufficient expertise in Verilog or VHDL to work with the package, then you can participate as an early adopter and gain an advantage over other universities in its use.

2. On May 13-14, a seminar organized by Imagination Technologies with Xilinx will take place in Los Angeles, where Harvey Mudd College professors and application engineers from Imagination will train professors from various universities to use MIPSfpga. If you or any of your familiar Universitetle teachers want to participate in it and can come to Los Angeles at this time, please contact either the educational program manager Robert Owen (his coordinates at imgtec.com/mipsfpga ) or me ( yuri.panchul@imgtec.com).

3. By the time of the workshop in Los Angeles, MIPSfpga will be officially announced, and upon completion (1) will be made publicly available. Therefore, if you do not have the opportunity to participate as an early adopter, you can nevertheless be able to start working with the product in the summer.

The ability to use industrial processor cores on the chain for educational purposes and without buying a commercial license will allow a large number of young developers in the academia to prototype innovative solutions in the field of on-chip systems and microarchitecture extensions, with the direct path to commercialization - creating their own chips for the Internet of things and others applications.

Yuri Panchul

Senior Hardware Design Engineer, MIPS processors

Imagination Technologies

Source: https://habr.com/ru/post/256223/

All Articles