Gikporn 5 or why open the chip

Guess the author by name? And here and there, unlike BarsMonster, we will open the microcircuit not out of sports interest and not even to see how it works. We will look for why it does not work. Sometimes this happens, especially if the technology of making crystals is under development and the projects launched can only be experimental. And a similar trouble happened with us. In our case, the obtained samples turned out to be inoperable (the yield is close to zero). The study of the functioning and electrical parameters pointed to the technological problems of manufacturing crystals, which we are to discover.

The chip is made using the 180 nm technology. With special features that allow to place on the same chip digital logic with high density and typical power supply 1.8V and analog component with operating voltages up to 200V. And in a compartment with working temperatures up to 150-170 it makes this technology very popular in industrial and automotive electronics.

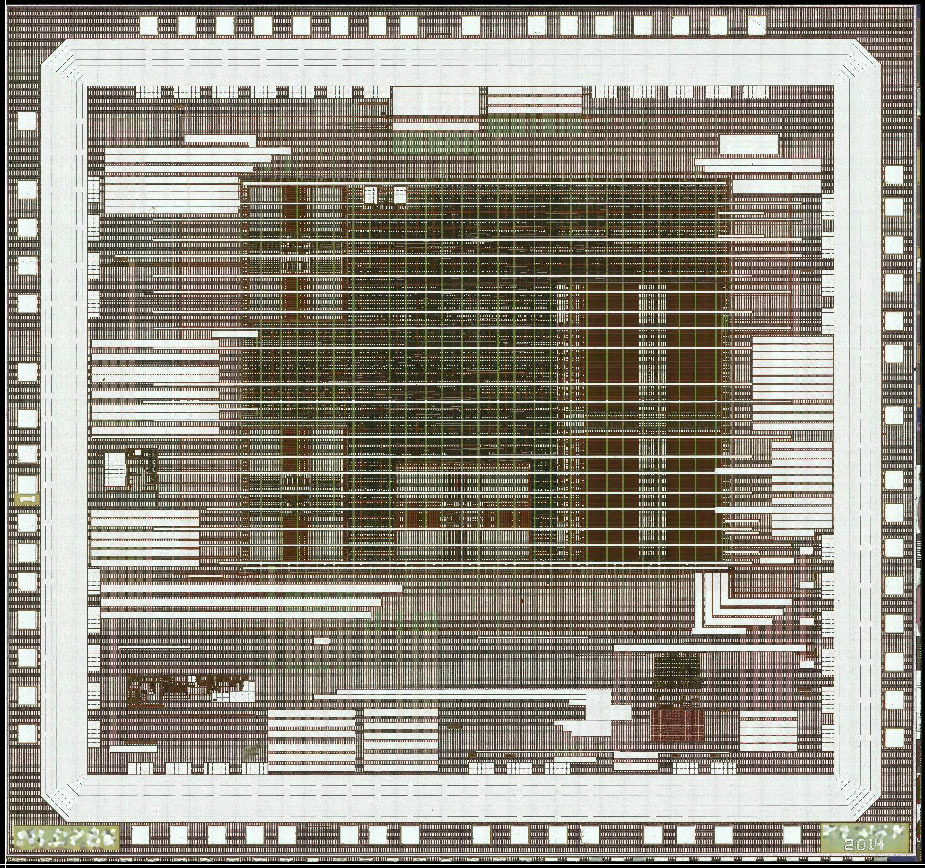

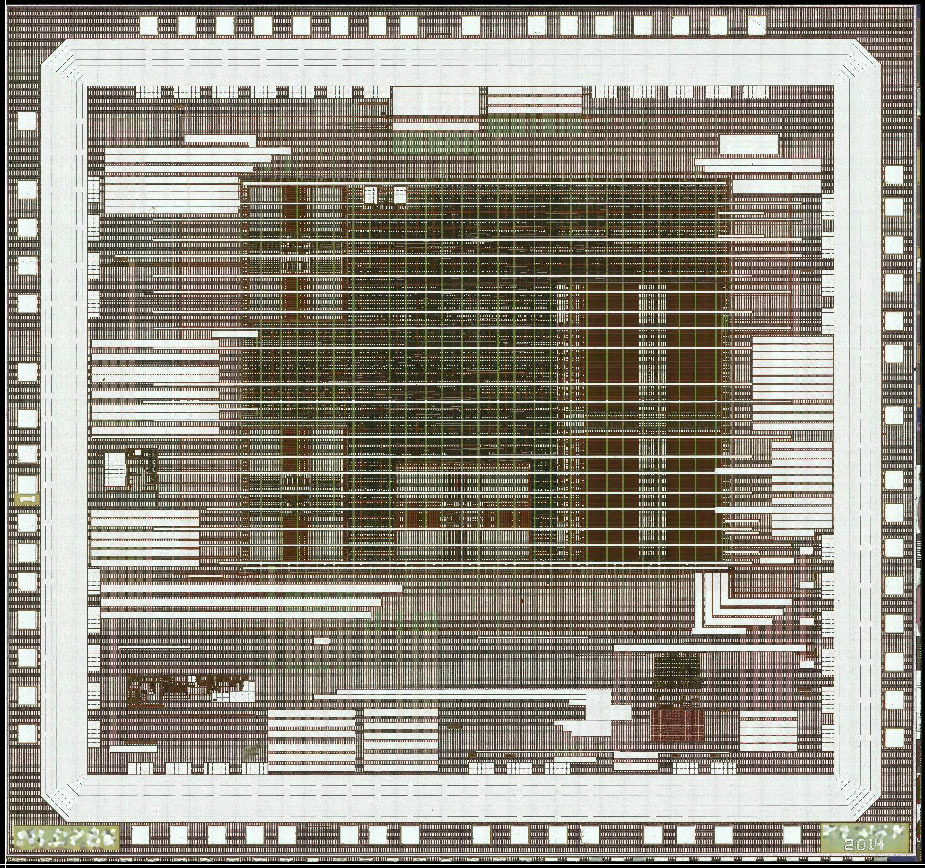

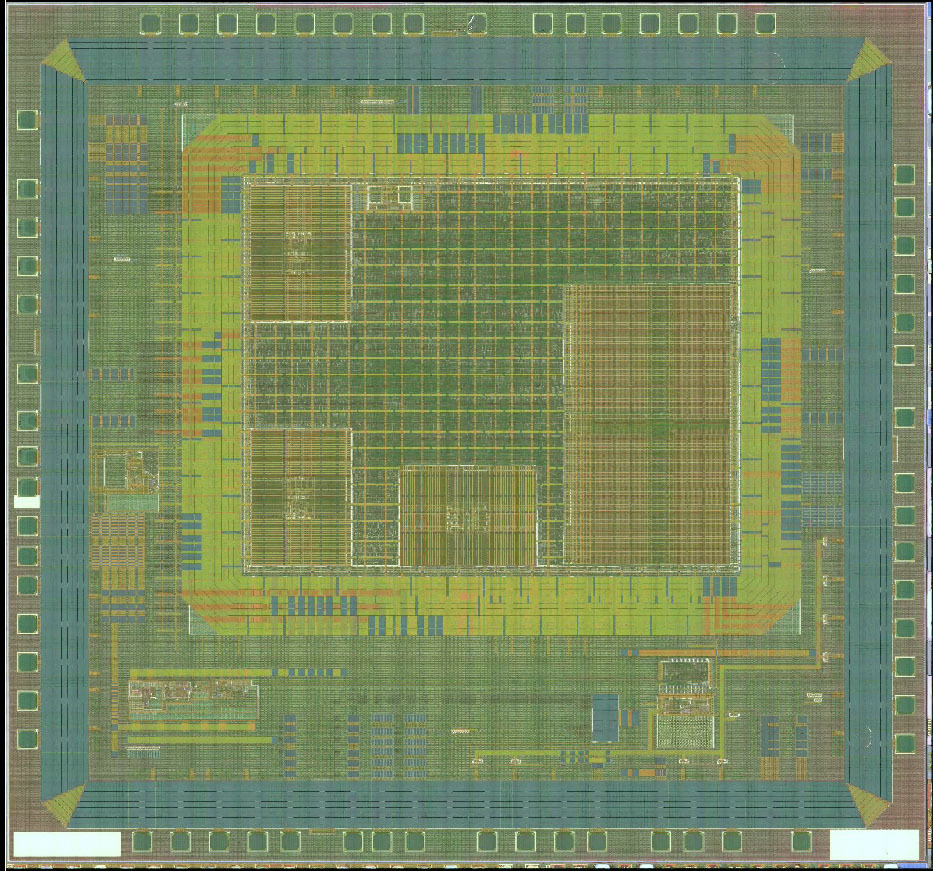

To begin with, we carried out layer-by-layer etching of crystals with a halt and full photographing at each technological level. The level of the sixth metal MET6 (some elements of the photos are hidden).

')

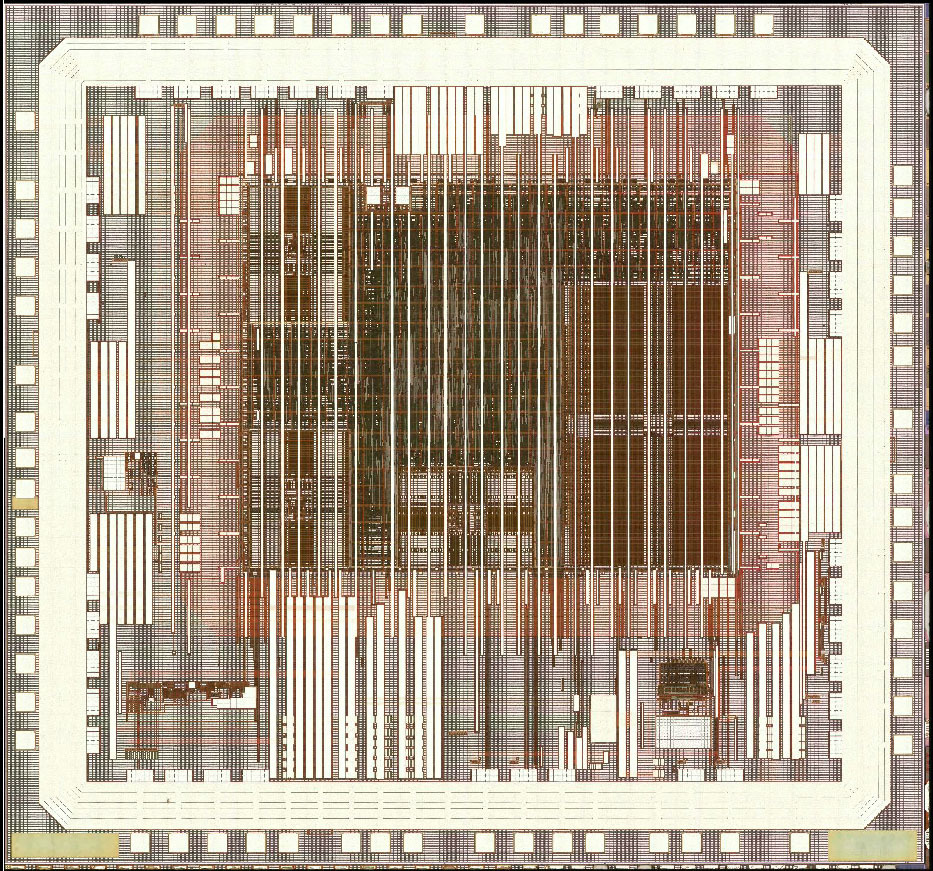

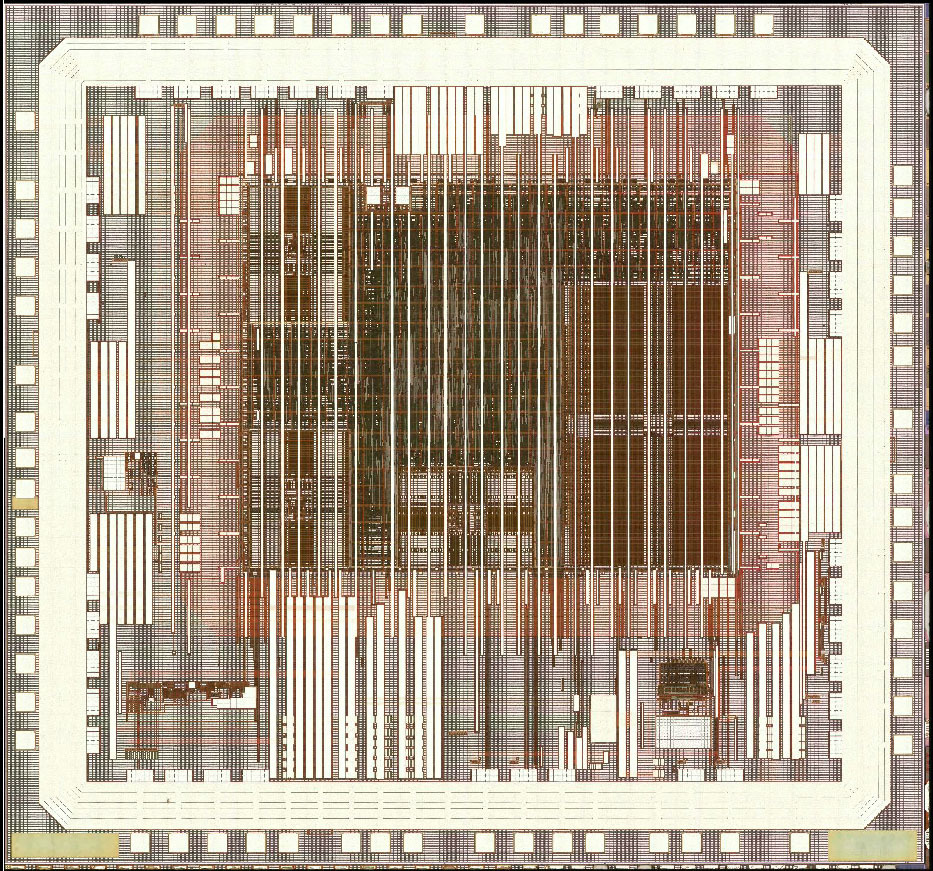

The level of the fifth metal MET5:

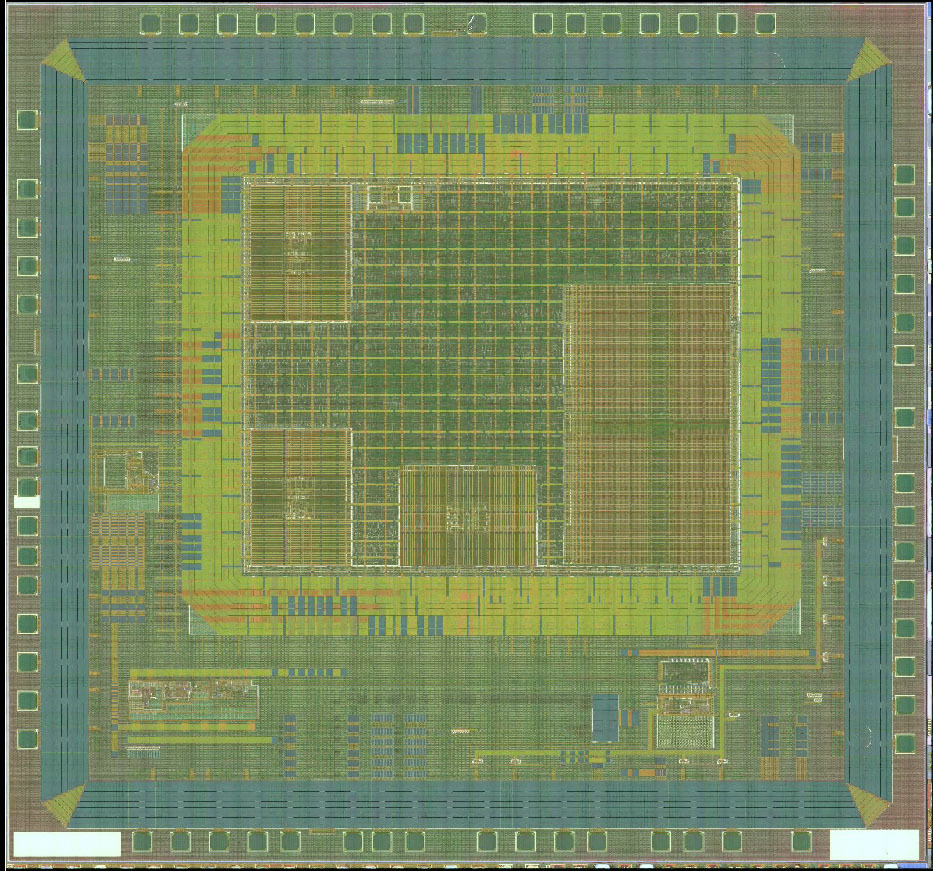

Jumper level between fifth and fourth metals VIA4:

Well, and so on, we got about 5 GB photos in total.

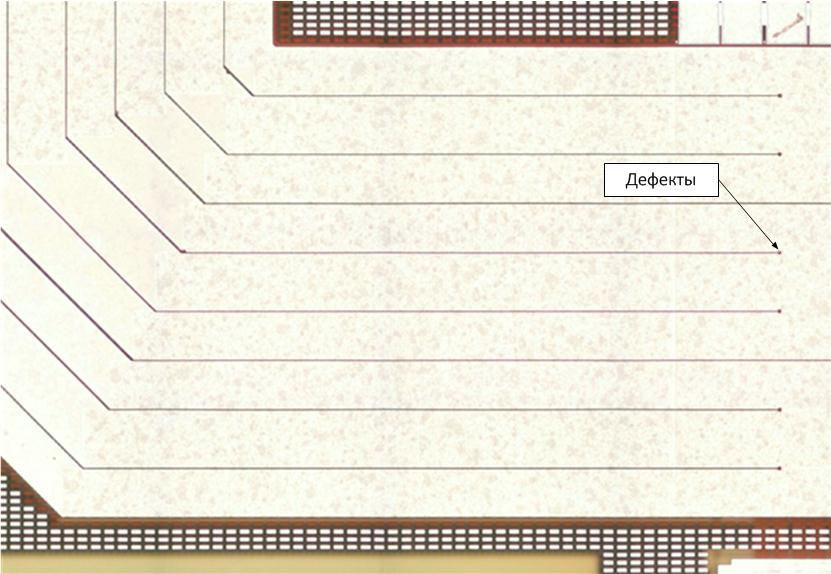

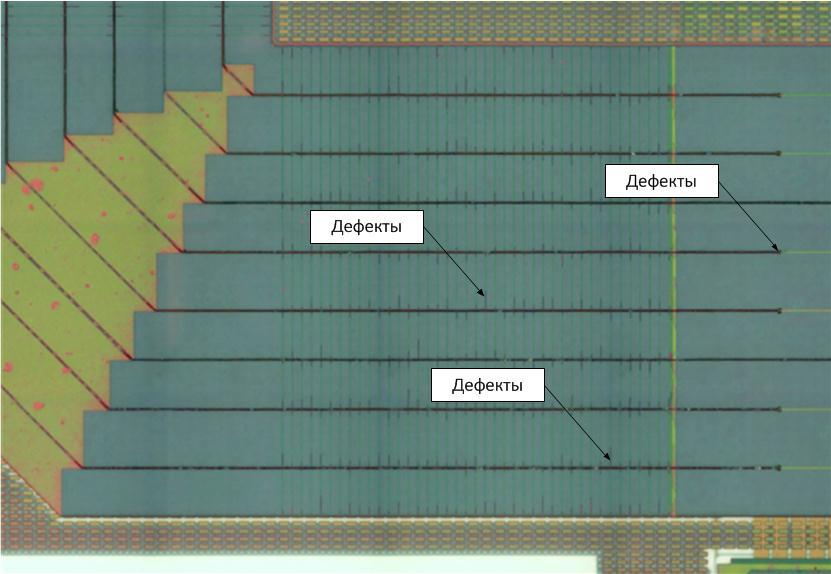

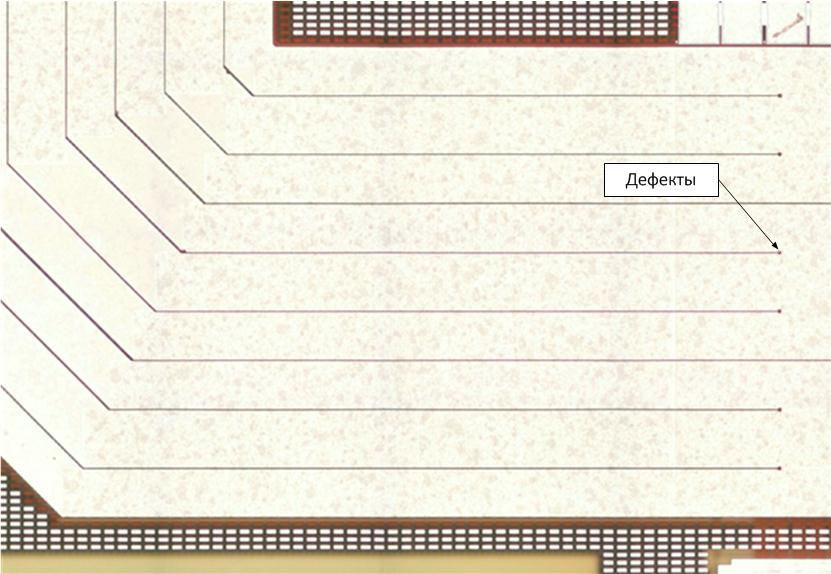

Unfortunately, even very neat layer-by-layer etching causes various destructions of crystal structures. And it is very difficult to determine that this is a technological defect of production or the result of preparation. Typically, the criterion is repeatability, if the effects are similar on several samples, then these are technological problems, if the effects are unique for each sample studied, then this is the result of preparation. For example, defects were found in the area of the power rings. At the level of the sixth metal, they are not visible, but since the fifth metal they began to appear:

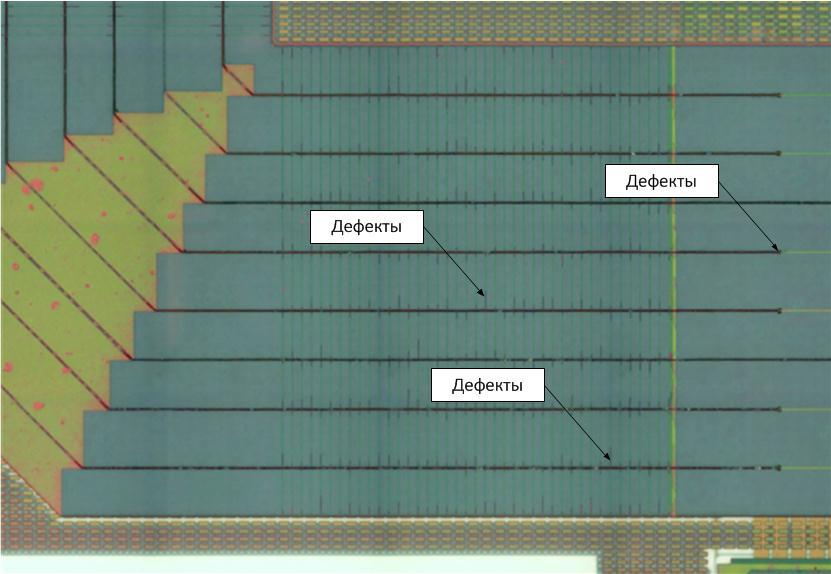

At the level of jumpers between the fifth and fourth metals became even more noticeable:

At the level of the third metal are already clearly visible:

But defects are unique for each sample and so far assigned to the problems of the etching process.

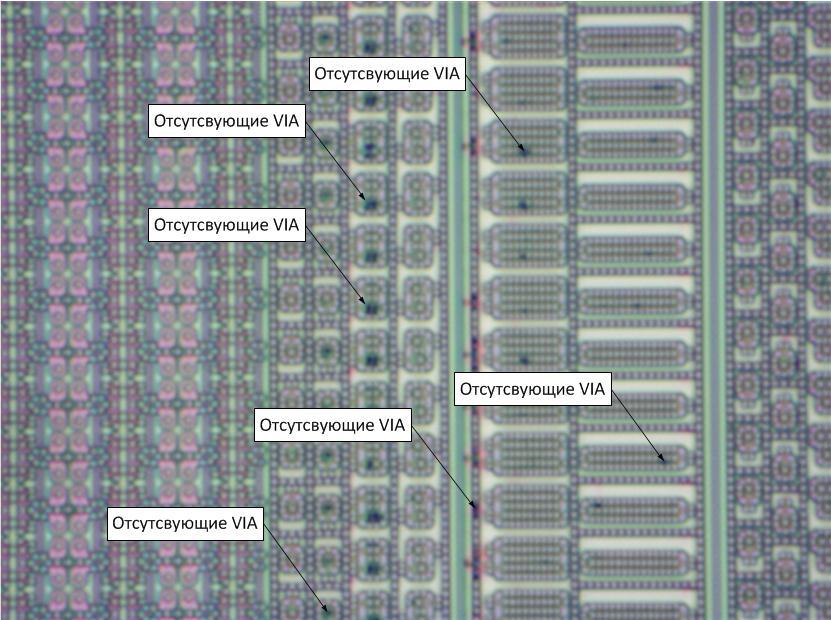

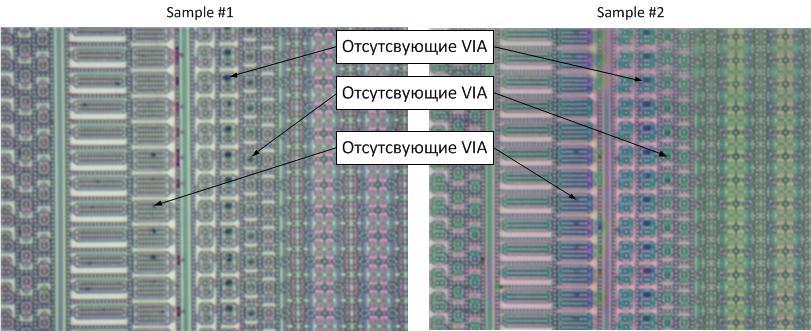

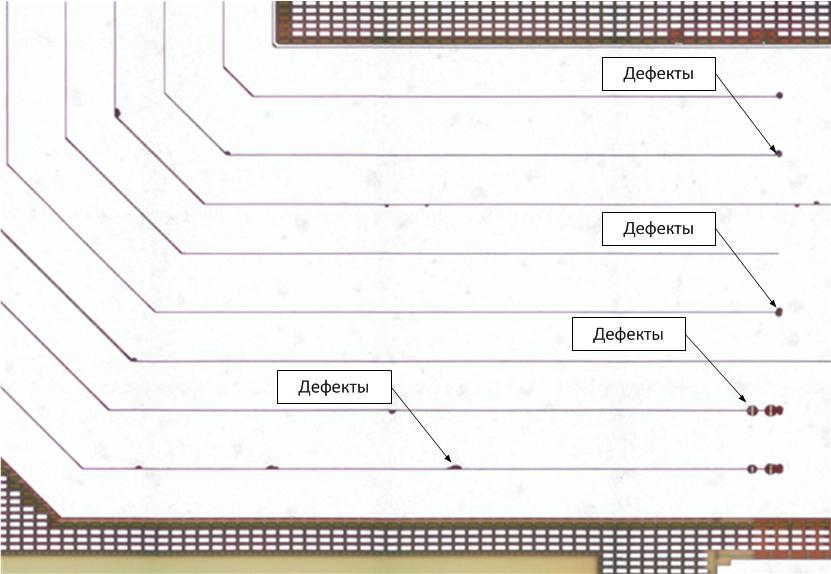

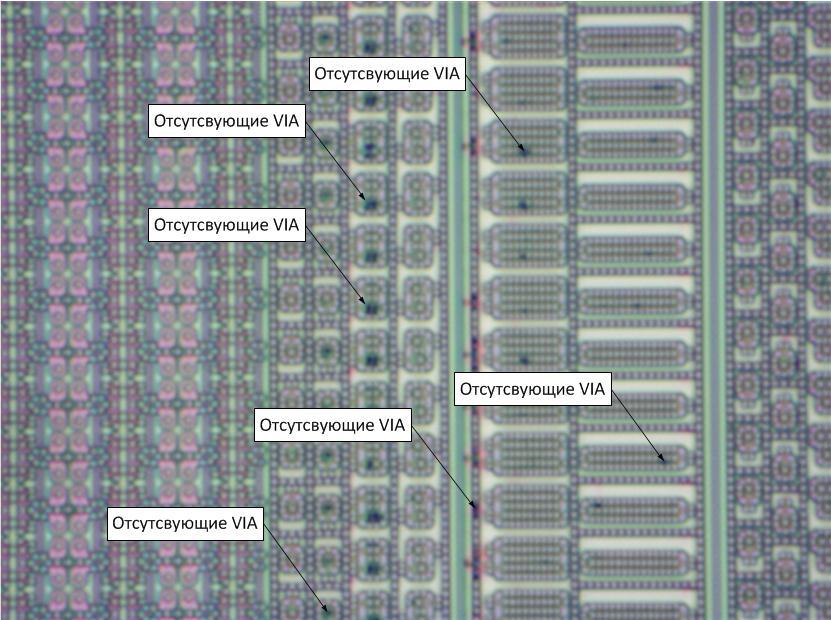

At the level of bridges between polysilicon and the first metal, missing or incompletely formed vias were detected, unfortunately the resolutions of the optical microscope are already at the limit and are seen as dark spots:

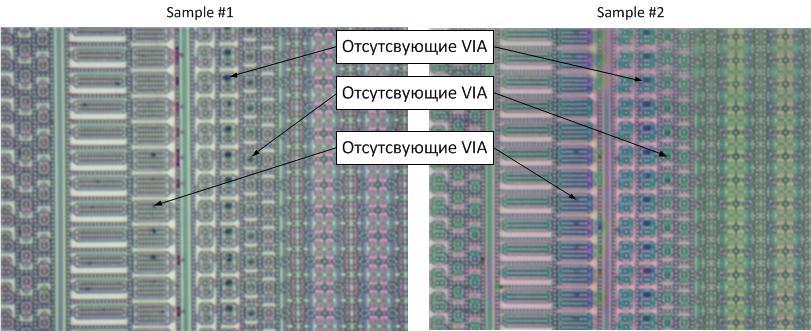

These defects with large correlations were repeated on several samples:

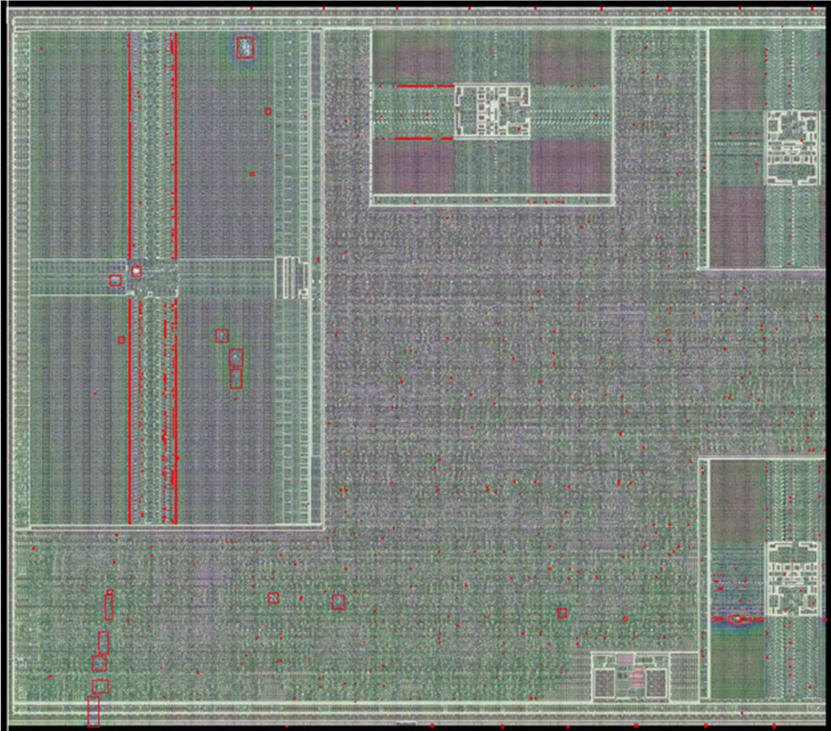

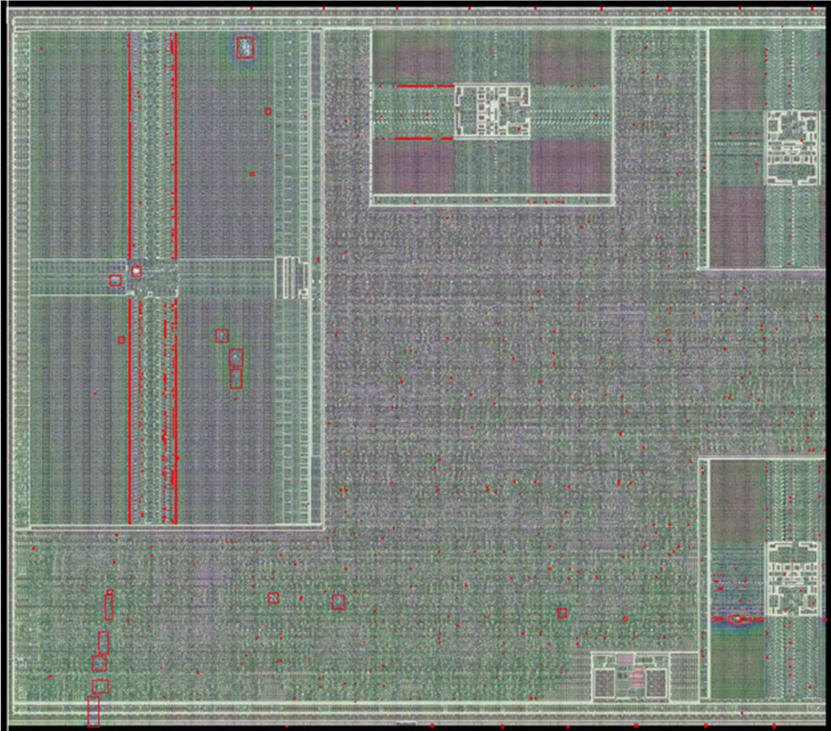

On the crystal there were a lot of such “escaped” vias, mostly they were in the area of the digital core and memory blocks. In the following illustration, they are marked with red dots, red rectangles indicate areas damaged during etching:

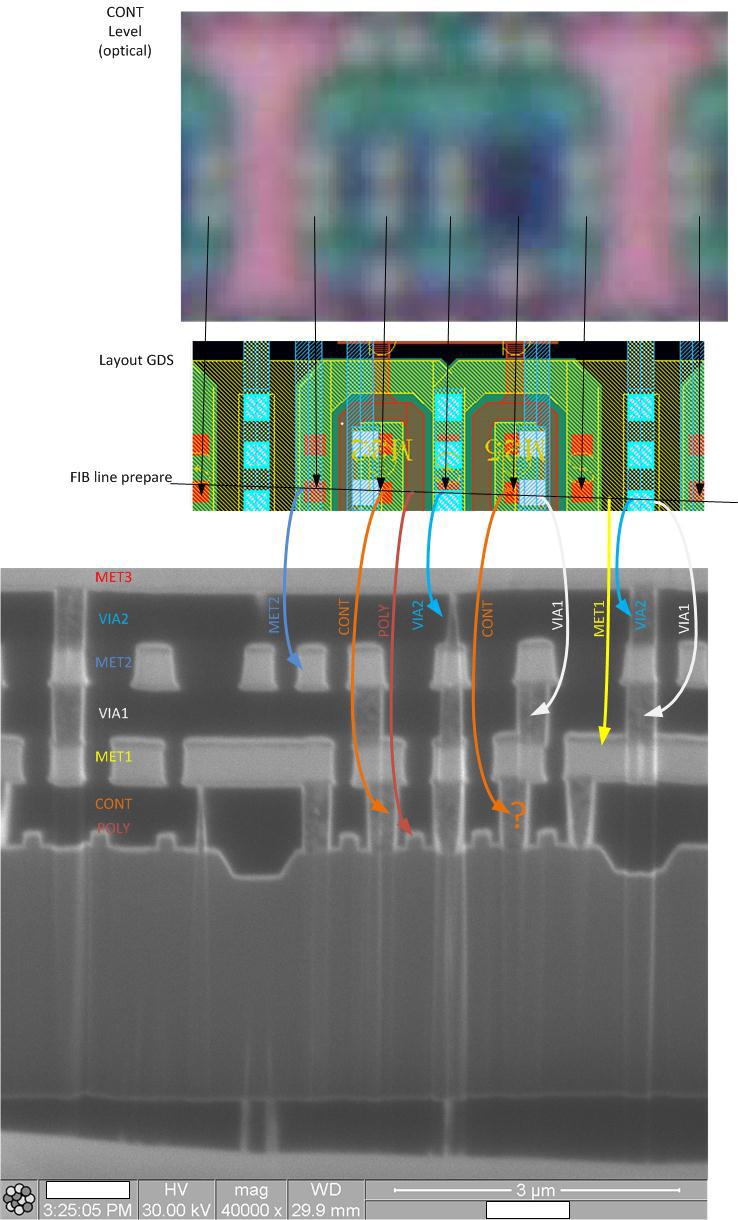

As noted earlier, optical microscopy does not allow for a visual assessment of the condition, and we had to use an electron microscope, and where the electron microscope is, it is not far from the FIB installation (Focused Ions Beam). FIB allows a directed ion beam with nanometer precision to cut the crystal elements or, on the contrary, to apply new layers on it, for example, to connect adjacent conductors.

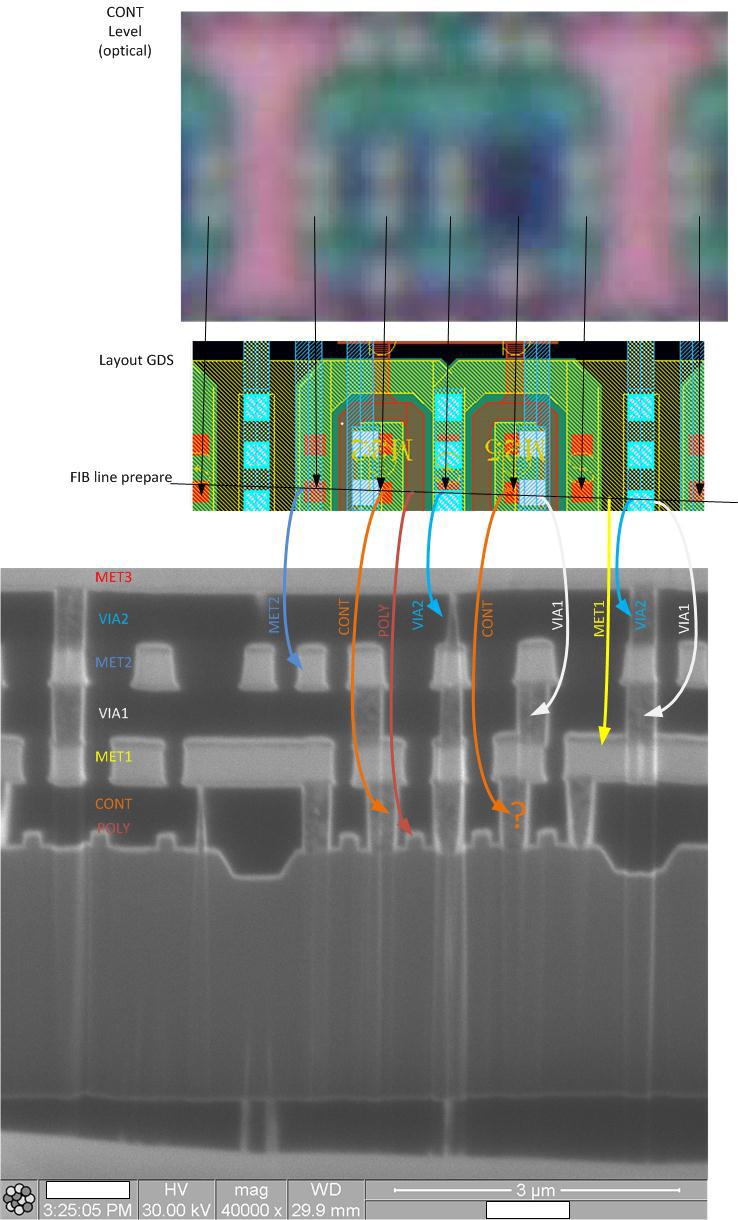

We conducted a cut of the crystal in the region where the intensity of the “emitted” VIA was maximum:

And it seems that they found a problem; indeed, the VIA did not correspond to the cut (in this process, they are designated as CONT). But the technologists and topologists of the scheme expressed doubt that we were in the right place. So the comments of technologists boiled down to the fact that there should have been at least something, and there was a pure insulator. And topologists indicated that although the cut is very similar to the topology, it differs from it. In particular, in the figure of the topology, the transition VIA1 and CONT are not coaxial, but on the cut they are located strictly one above the other, and this cannot be attributed to the technological variation.

In a more detailed analysis, it was found that the area is completely suitable for a given slice in the same area, but with an indent of about 2 microns, and there is really no such transition between the first metal and polysilicon in it. We just got the wrong place.

When re-cutting, we were able to get into the required area, and there were no more complaints about the transition windows:

As you can see, now the whole photo of the slice completely repeats the topology and the VIA between the different layers is spaced apart. All vias are fully formed. And the reason for the inoperability of the crystals has not been found.

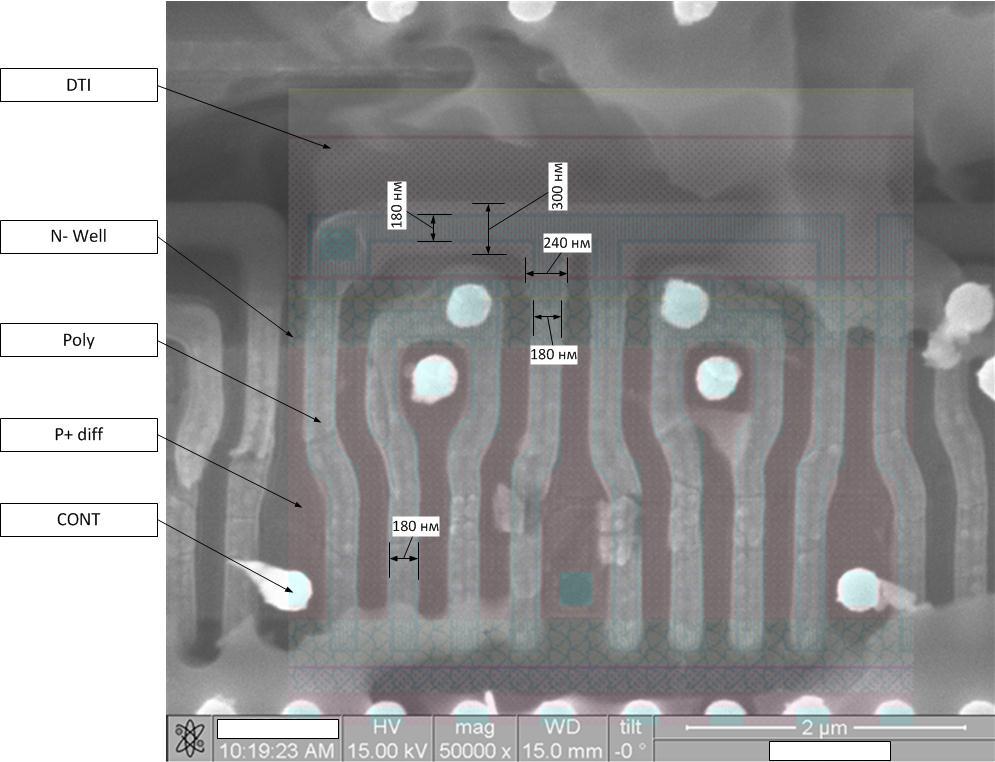

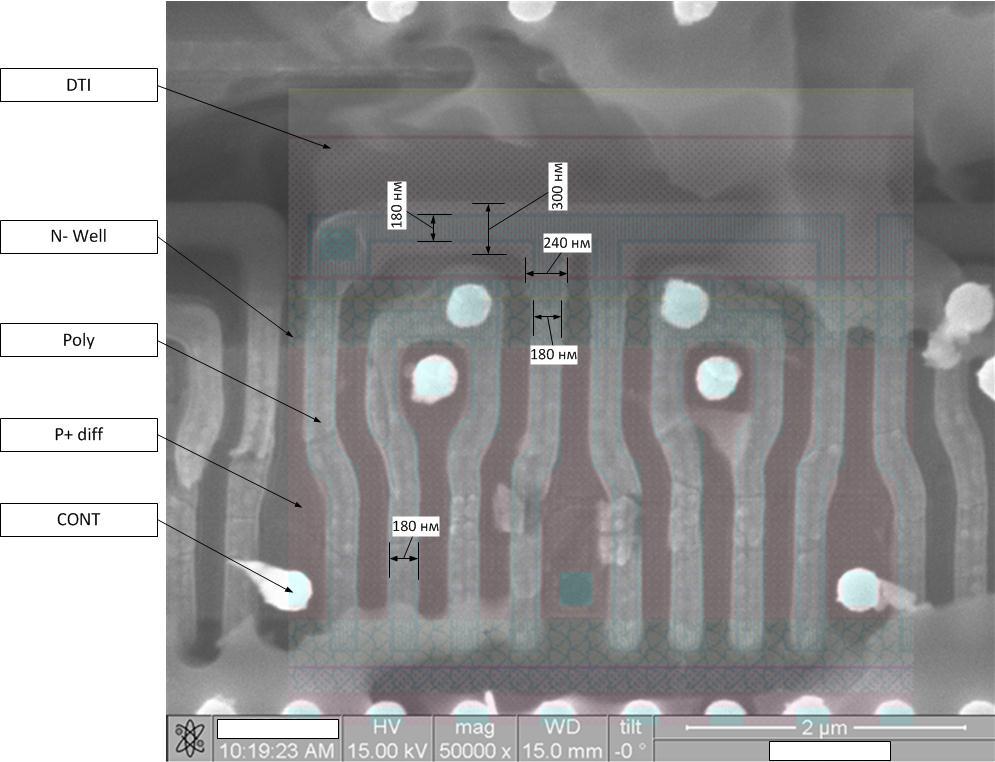

When viewed through an electron microscope the level of polysilicon (labeled POLY), it was noticed that in the area of separation of P-channel and N-channel transistors using a deep dielectric (indicated in the DTI figures), polysilicon has some thickening.

The photograph has a topology drawing for clarity. But at the same time, there are no gaps or “short-circuits” between different polysilicon tires. But in any case, we decided to see what was going on there with polysilicon.

But first, let's understand what polysilicon (POLY) is and what it is for. Polysilicon compounds are the trace resource of the lowest crystal level. The main compounds in the crystal are provided through the metals of the upper layers. But the neighboring transistors of one valve can be connected using polysilicon. In order for polysilicon to become electrically conductive, it is alloyed (by adding impurities of fluorine, boron, or arsenic), sometimes all the polysilicon in the crystal is doped, sometimes not. In the case when polysilicon is not doped, its conductivity is achieved by depositing a layer of silicide on top of it (this is a silicon compound with metals). .

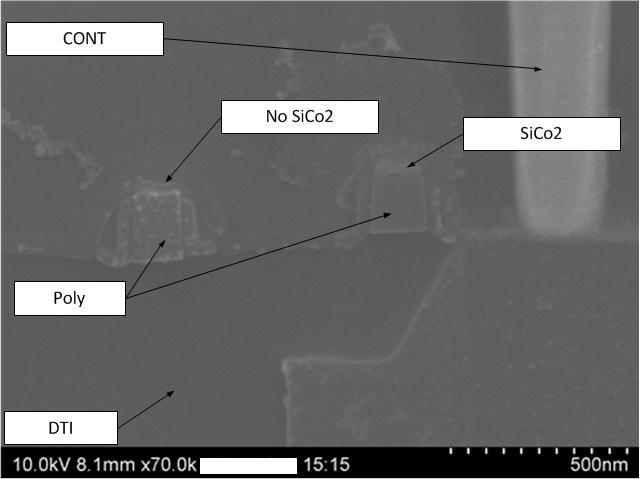

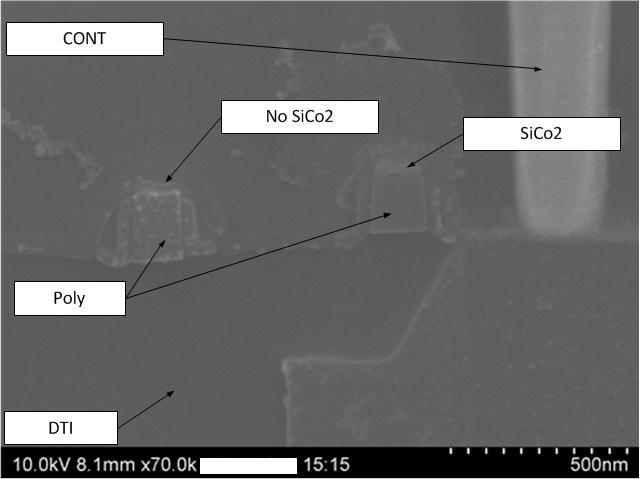

For this, we have made another cut, which allows us to see the structure of polysilicon over deep and shallow dielectrics.

Already in this photo, it is clear that a white silicide “cap” is visible above polysilicon, which is located to the right of DTI, but not above polysilicon directly above DTI.

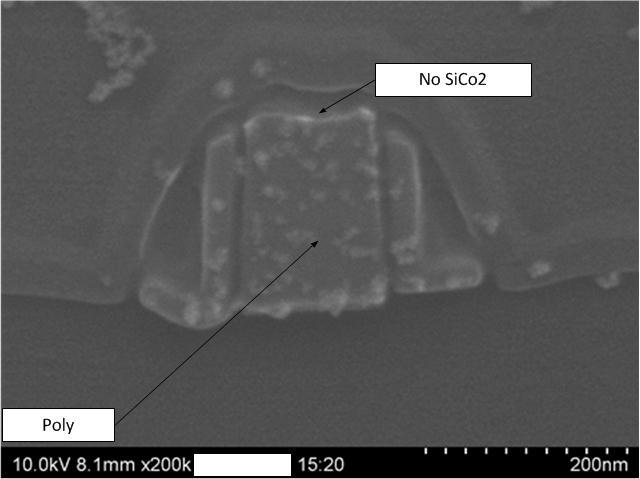

Approaching:

Approaching:

And now separately, polysilicon to the right of DTI with silicide:

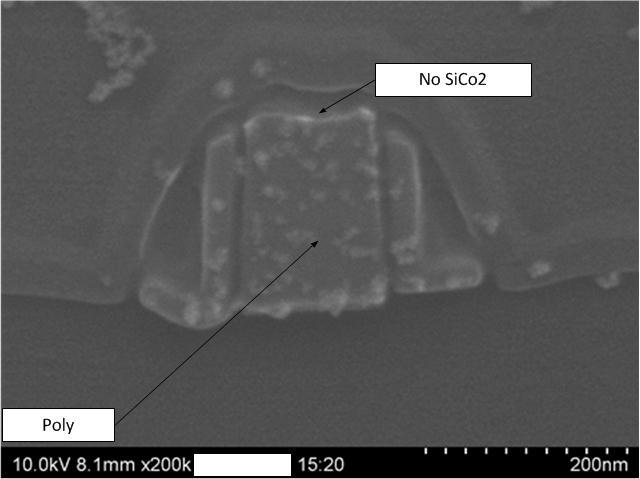

And polysilicon over DTI without silicide:

Now we have found the problem, at least it fits into the crystal failure model. Due to the absence of silicide over polysilicon, there is an increase in the resistance of the connections between neighboring transistors to hundreds of kΩ or even MOhm, they begin to work very slowly and unpredictably. And although the problem we found, it is necessary to find a solution to this problem. To do this, we analyzed another part of the scheme, where the polysilicon width over the DTI is more than 180 nm (the minimum resolved and for which we have found the problem). Such a region is found, the width of polysilicon in this place is 500 nm. Also at the same time we will define how CONT jumpers behave to polysilicon if they are located above the DTI.

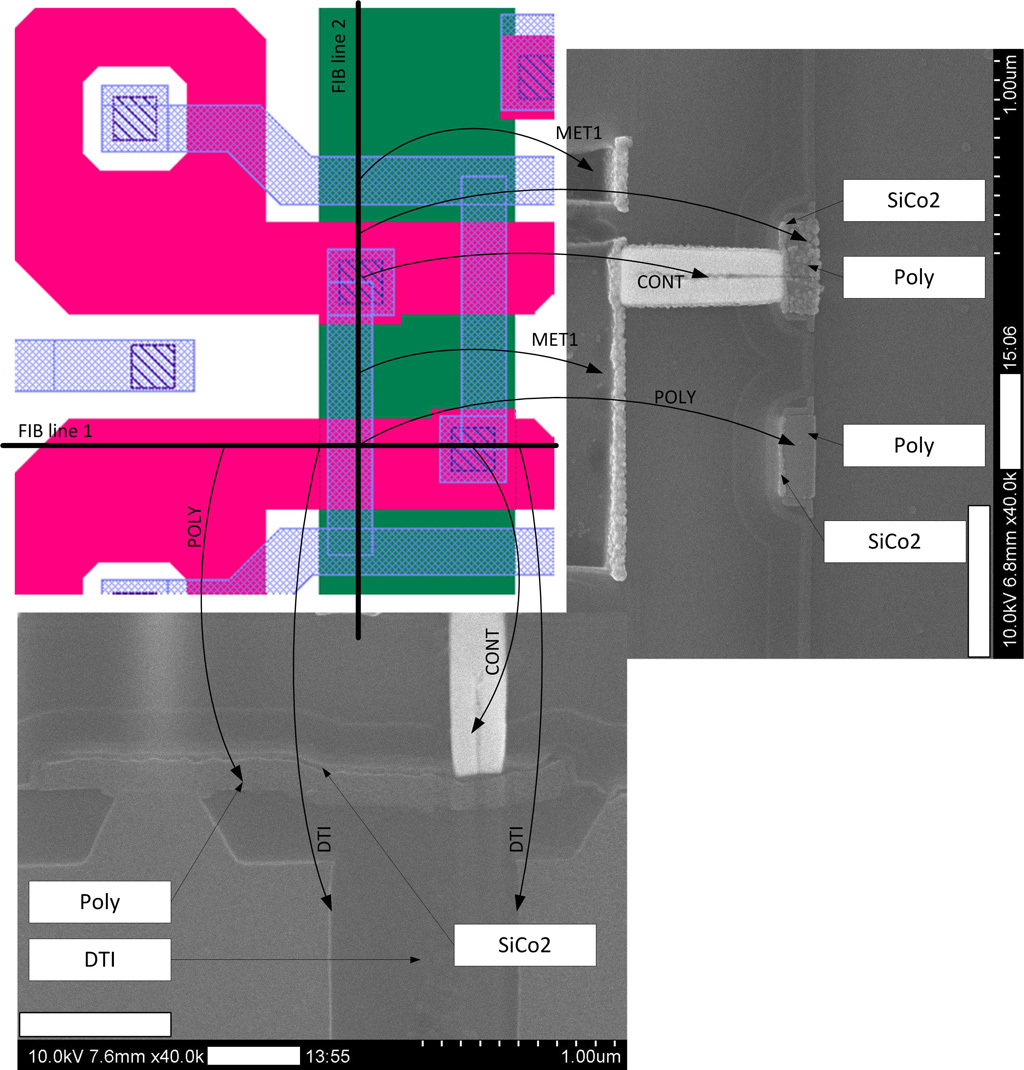

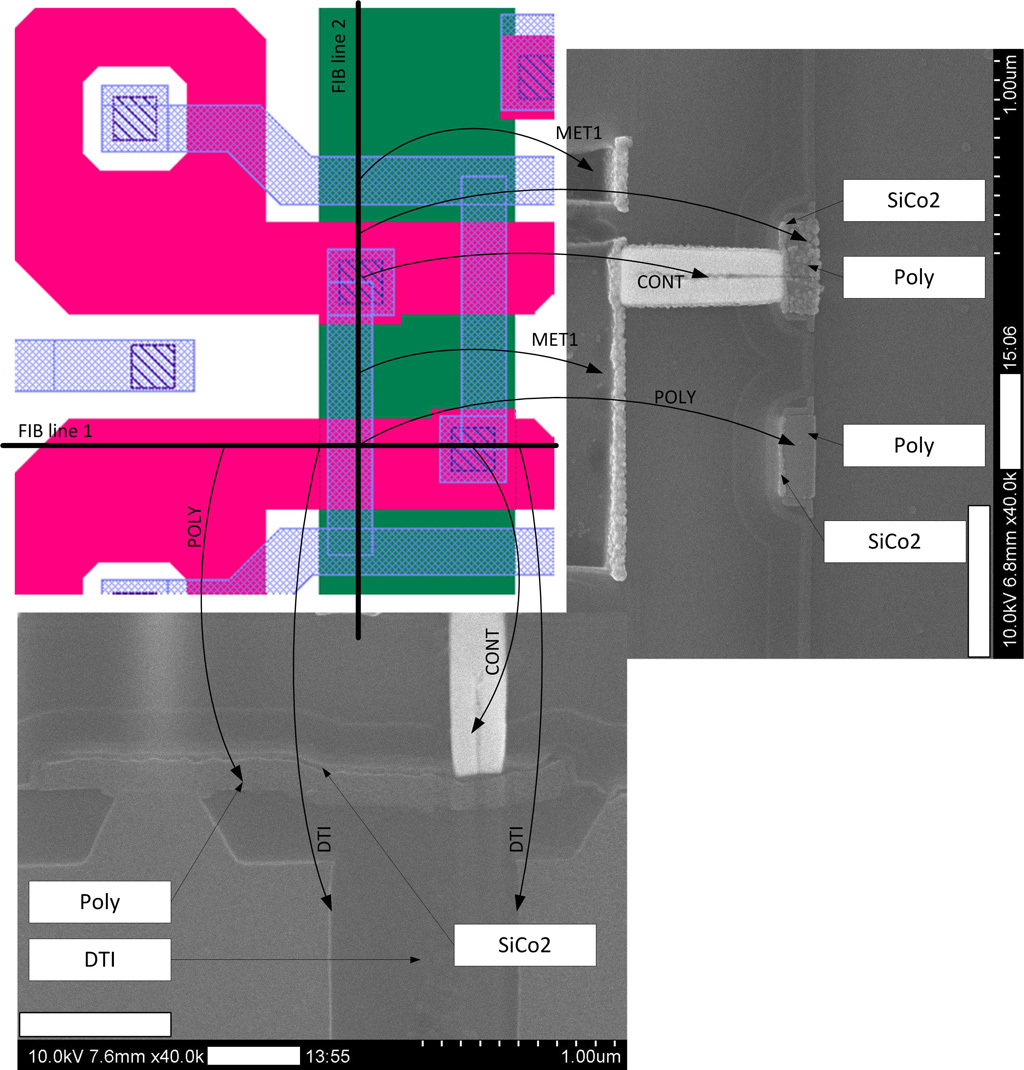

When cutting the FIB, two perpendicular cuts were specially obtained, which allow to obtain a complete picture of the state of silicide over polysilicon over DTI.

The photo shows that CONT connects to POLY without any problems. And silicide was formed over polysilicon in full. On the horizontal cut of FIB Line 1, the silicide did not stain white due to the fact that its longitudinal depth (for the electron flux of the microscope) is ~ 250 nm and has a weak reflection, unlike the vertical cut of the FIB Line2, there the silicide depth is up to 2000 nm and he turned white. But on the horizontal section the layer of silicide is still clearly visible. We, as crystal developers, do not undertake to judge why silicide does not form over polysilicon over DTI, if its width is 180 nm. The crystal manufacturer factory also came to a similar conclusion, and as a solution to the problem, prohibited polysilicon conductors with a width of less than 1 micron from being led over DTI.

The chip is made using the 180 nm technology. With special features that allow to place on the same chip digital logic with high density and typical power supply 1.8V and analog component with operating voltages up to 200V. And in a compartment with working temperatures up to 150-170 it makes this technology very popular in industrial and automotive electronics.

To begin with, we carried out layer-by-layer etching of crystals with a halt and full photographing at each technological level. The level of the sixth metal MET6 (some elements of the photos are hidden).

')

The level of the fifth metal MET5:

Jumper level between fifth and fourth metals VIA4:

Well, and so on, we got about 5 GB photos in total.

Unfortunately, even very neat layer-by-layer etching causes various destructions of crystal structures. And it is very difficult to determine that this is a technological defect of production or the result of preparation. Typically, the criterion is repeatability, if the effects are similar on several samples, then these are technological problems, if the effects are unique for each sample studied, then this is the result of preparation. For example, defects were found in the area of the power rings. At the level of the sixth metal, they are not visible, but since the fifth metal they began to appear:

At the level of jumpers between the fifth and fourth metals became even more noticeable:

At the level of the third metal are already clearly visible:

But defects are unique for each sample and so far assigned to the problems of the etching process.

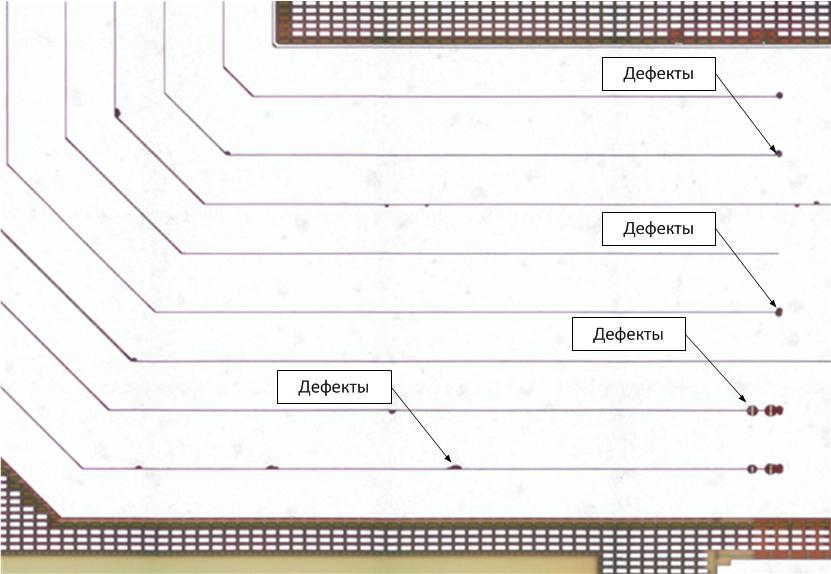

At the level of bridges between polysilicon and the first metal, missing or incompletely formed vias were detected, unfortunately the resolutions of the optical microscope are already at the limit and are seen as dark spots:

These defects with large correlations were repeated on several samples:

On the crystal there were a lot of such “escaped” vias, mostly they were in the area of the digital core and memory blocks. In the following illustration, they are marked with red dots, red rectangles indicate areas damaged during etching:

As noted earlier, optical microscopy does not allow for a visual assessment of the condition, and we had to use an electron microscope, and where the electron microscope is, it is not far from the FIB installation (Focused Ions Beam). FIB allows a directed ion beam with nanometer precision to cut the crystal elements or, on the contrary, to apply new layers on it, for example, to connect adjacent conductors.

We conducted a cut of the crystal in the region where the intensity of the “emitted” VIA was maximum:

And it seems that they found a problem; indeed, the VIA did not correspond to the cut (in this process, they are designated as CONT). But the technologists and topologists of the scheme expressed doubt that we were in the right place. So the comments of technologists boiled down to the fact that there should have been at least something, and there was a pure insulator. And topologists indicated that although the cut is very similar to the topology, it differs from it. In particular, in the figure of the topology, the transition VIA1 and CONT are not coaxial, but on the cut they are located strictly one above the other, and this cannot be attributed to the technological variation.

In a more detailed analysis, it was found that the area is completely suitable for a given slice in the same area, but with an indent of about 2 microns, and there is really no such transition between the first metal and polysilicon in it. We just got the wrong place.

When re-cutting, we were able to get into the required area, and there were no more complaints about the transition windows:

As you can see, now the whole photo of the slice completely repeats the topology and the VIA between the different layers is spaced apart. All vias are fully formed. And the reason for the inoperability of the crystals has not been found.

When viewed through an electron microscope the level of polysilicon (labeled POLY), it was noticed that in the area of separation of P-channel and N-channel transistors using a deep dielectric (indicated in the DTI figures), polysilicon has some thickening.

The photograph has a topology drawing for clarity. But at the same time, there are no gaps or “short-circuits” between different polysilicon tires. But in any case, we decided to see what was going on there with polysilicon.

But first, let's understand what polysilicon (POLY) is and what it is for. Polysilicon compounds are the trace resource of the lowest crystal level. The main compounds in the crystal are provided through the metals of the upper layers. But the neighboring transistors of one valve can be connected using polysilicon. In order for polysilicon to become electrically conductive, it is alloyed (by adding impurities of fluorine, boron, or arsenic), sometimes all the polysilicon in the crystal is doped, sometimes not. In the case when polysilicon is not doped, its conductivity is achieved by depositing a layer of silicide on top of it (this is a silicon compound with metals). .

For this, we have made another cut, which allows us to see the structure of polysilicon over deep and shallow dielectrics.

Already in this photo, it is clear that a white silicide “cap” is visible above polysilicon, which is located to the right of DTI, but not above polysilicon directly above DTI.

Approaching:

Approaching:

And now separately, polysilicon to the right of DTI with silicide:

And polysilicon over DTI without silicide:

Now we have found the problem, at least it fits into the crystal failure model. Due to the absence of silicide over polysilicon, there is an increase in the resistance of the connections between neighboring transistors to hundreds of kΩ or even MOhm, they begin to work very slowly and unpredictably. And although the problem we found, it is necessary to find a solution to this problem. To do this, we analyzed another part of the scheme, where the polysilicon width over the DTI is more than 180 nm (the minimum resolved and for which we have found the problem). Such a region is found, the width of polysilicon in this place is 500 nm. Also at the same time we will define how CONT jumpers behave to polysilicon if they are located above the DTI.

When cutting the FIB, two perpendicular cuts were specially obtained, which allow to obtain a complete picture of the state of silicide over polysilicon over DTI.

The photo shows that CONT connects to POLY without any problems. And silicide was formed over polysilicon in full. On the horizontal cut of FIB Line 1, the silicide did not stain white due to the fact that its longitudinal depth (for the electron flux of the microscope) is ~ 250 nm and has a weak reflection, unlike the vertical cut of the FIB Line2, there the silicide depth is up to 2000 nm and he turned white. But on the horizontal section the layer of silicide is still clearly visible. We, as crystal developers, do not undertake to judge why silicide does not form over polysilicon over DTI, if its width is 180 nm. The crystal manufacturer factory also came to a similar conclusion, and as a solution to the problem, prohibited polysilicon conductors with a width of less than 1 micron from being led over DTI.

Source: https://habr.com/ru/post/241947/

All Articles