A word about DSP Builder

To my surprise, I did not find a single article about DSP Builder on Habré (maybe I was looking bad?). And it’s strange, because DSP Builder is a real revolution in the field of FPGA construction almost unnoticed by anyone. In my opinion, this situation was created for two reasons.

The first is a somewhat contemptuous attitude of the harsh pleaters to this product. For some reason, it is considered that DSP Builder is “for students”. The situation is just like with Delphi. Moreover, this attitude towards DSP Builder is especially unclear against the background of enthusiastic reviews in the direction of shells like Active HDL. True, this may in part be apparently explained by the fact that it is quite rare for specialists to be well-versed in both pleus and signal processing. Such experts are single and have three-digit sn. The rest are either in one or the other. And the first ones cannot understand why they need this “builder” (and here’s some kind of Simulink!), And the second sculpt the algorithms and declare “and their implementation is not my business!” (The real picture is from one well-known domestic office).

The second reason is a bunch of three very heterogeneous programs and environments. With the ensuing dancing with the incompatibility of versions and some completely strange inconsistencies. Especially touches when DSP Builder does not notice the established Matlab point-blank, and at least what you are doing!

')

But the author himself found a very stable bundle. Therefore, I will only talk about the version that comes with the 11.0th Quartus. She, fortunately, finds without problems and clings to Matlab, dearly beloved by the author, version 7.9 (in the author's opinion, the best after the famous version 6.5). After successful installation, two libraries should appear in Simulinka: Altera DSP Builder Blockset and Altera DSP Builder Advanced Blockset. And the corresponding section in the Matlab help and examples links. The examples, I must say, are very obvious and cover almost all typical tasks encountered in the plisovodam.

If your DSP Builder was bundled with Quartus and before installing megafunctions (and this is probably the case), then megafunctions should be picked up. We type the alt_dspbuilder_setup_megacore command in the Matlab command window and get:

"

"

The team will definitely work with an error, this is due to the fact that an extremely limited number of megafunctions support (and at the same time correctly support) the clinging to Simulink. Most likely, except for the six shown in Fig. blocks, nothing else to pick up and fail. If you still have the feeling that someone else supports Simulink, then you can simply manually transfer the files to the temporary directory from the <where Quartus> \ libraries subdirectory and run alt_dspbuilder_setup_megacore again and again. There is a chance that something else clings.

The use of these blocks is somewhat specific to the Simula. The fact is that at the beginning Simulin does not know which parameters you would like to choose for the mega-function used, so at first it will look like a “black box” in your model:

After that, you click on it and the standard configuration window for this mega-function drops out, which you saw a hundred times in the Mega Wizard Plug-In Manager. But now, after selecting the parameters, “Manager” knows that you also want to generate files for Simula. And, about a miracle, now your block becomes a normal simulinkovsky block:

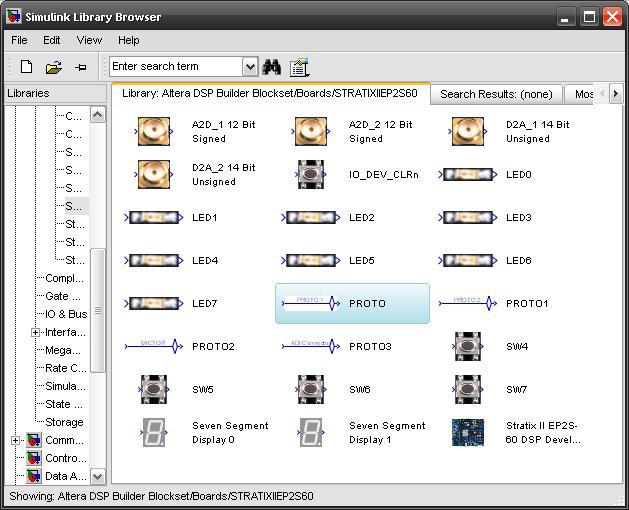

DSPbuilder initially supports a certain number of “starter whales”. This support boils down to the fact that DSPbuilder “knows” where you have connected lights, where are the buttons, and where (even!) Hangs sma. To the surprise of the author, there is even a familiar 4th Stratix board in the list. But the list is extremely limited. For example, the author is currently working with a DE2-115 board with a stone from the Cyclone IVE series. And she, alas, this version is not supported.

The question arises: is it possible to add a description of your board with your hands? We will answer. Well, first of all, nobody needs it. And, secondly, it is done very simply.

We climb into the <where_DSPbuilder> \ lib \ boardsupport \ boards directory and see files with the .board extension. Next, copy any of the files that describes the most related to us fee (in my case - this is Cyclone_III_EP3C120.board), open and edit it. The file format is so clear that it is even funny. But if it is still not clear, then open the DSP Builder Handbook, Volume 2: DSP Builder Standard Blockset p.137 and read.

Despite the fact that everything is clear, the description of the new board must be done very carefully, so that later not scribbling messages in conferences like: “help, dspbuilder gives an error ...”. You can even change the board image in the same directory. Next, you need to inform DSPbuilder of the new board. This is done by the alt_dspbuilder_createComponentLibrary command. After it has been worked out (and it will probably fly out with an error, but you need to score for it), you will happily see your board in the “libraries” sub-library. By the way, in a similar way a new binary component can be screwed to the board. For example, a non-standard indicator, joystick button, rail switch, external bus, etc.

The main advantage of DSP Builder is not only the preparation of projects for FPGAs, but also the ability to upload and check them in the “live gland” without leaving Simulink. The method of preparing the initial contents of the RAM and ROM directly from the Matlab variables, and not with the help of crookedly written utilities, confusing to the bit depths and encodings, also relates to this. And, not least, check the work of the project using the very convenient graphical toolkit Simulinka, rather than scribbling text "workbenches" on dozens of pages for the constantly falling "Modelsima" (although this is possible in DSP Builder'e).

DSP Builder offers two tools for testing. The first is “HIL” (Hardware-in-the-loop, which in Russian can be translated as “real hardware inside the model”). Here, you must first assemble a project of the system under study, and then create a “covering” model, where your system will be a HIL-subsystem, separated from the model space by inputs and outputs, input and output, respectively. It sounds difficult, but open the FreqSweep example from the Tutorials and everything will become clear.

By the way, some pleasovods think that HIL uses SignalTap. Actually, SignalTap has nothing to do with the HIL methodology. But SignalTap can also be used with DSP Builder, and this is the second way. In order to enable SignalTap, you need to use the “SignalTap II Logic Analyzer” block from the “AltLab” library. There is a limitation when using SignalTap - only one clock signal (the rest are perceived as normal inputs). But, frankly, how often do we use several clock regions in SignalTap?

Regarding the optimality of the generated code. DSPbuilder is, in essence, a translator from Simulink's graphics to the selected HDL code. Open the generated project and see the main file. You will see that DSPbuilder simply verbally "described" the connection of blocks in your simulinkovsky project. Similarly, you would have done when manually transferring to the HDL code. It follows that the level of optimality of the project depends only on you. Use mega-function for, for example, CIC-filter - one result, too lazy to read the description, or do not want to get involved in commercial bark and decide to write with your hands - another result. All the same!

In conclusion, briefly about connecting their blocks. As the author mentioned at the beginning, in his opinion DSPbuilder is a revolution unnoticed by anyone. A good tone, therefore, is considered a style when you don’t crawl out of DSPbuilder at all and gradually forget that there are any AHDLs and Verilogs, Quartuses and Synplicity. With such an approach, in theory, evenmiserable mathematicians will be able to create the firmware (and in our case, the leaders of IT firms stubbornly believe that only people after Math must work on algorithms, although, according to the author’s experience, mathematicians are never able to algorithms!), which the chips only in the picture before seen.

By the way, DSPbuilder allows you to completely control the project settings from the Simulin frame. For this, there are corresponding blocks in the AltLab sub-library. From DSPbuilder, you can work perfectly with SOPC Builder (well, if someone likes to insert a processor with very little features into an expensive plisin). But, the author hears the right question: how can one not leave the environment at all, when, after all, we need to dock with the outside world? With the same Ethernet Ethernet, com-port, etc. etc. In fact, for this you need to write the corresponding component yourself. Here you can act in three ways.

The first, the most difficult and almost impracticable, is to create your own mega-function, go through the IP Certifications process (in my opinion not for free, who knows, correct), and then read above. By the way, not such a fantastic way. The author spent some time creating a new mega-function for one of the CAD manufacturers for FPGAs. But then you only have to do this and nothing else.

The second way is to write a new block using Simula. But, a true pleisovod sniffs contemptuously at such a method.

Well, the third way is to drag your HDL code into the framework of Simulink. For this case in the DSPbuilder'e block provides «HDL Import». This is a whole process that the author can describe later in a separate post, but this is the most realistic way that, believe me, it’s worth spending time once.

The first is a somewhat contemptuous attitude of the harsh pleaters to this product. For some reason, it is considered that DSP Builder is “for students”. The situation is just like with Delphi. Moreover, this attitude towards DSP Builder is especially unclear against the background of enthusiastic reviews in the direction of shells like Active HDL. True, this may in part be apparently explained by the fact that it is quite rare for specialists to be well-versed in both pleus and signal processing. Such experts are single and have three-digit sn. The rest are either in one or the other. And the first ones cannot understand why they need this “builder” (and here’s some kind of Simulink!), And the second sculpt the algorithms and declare “and their implementation is not my business!” (The real picture is from one well-known domestic office).

The second reason is a bunch of three very heterogeneous programs and environments. With the ensuing dancing with the incompatibility of versions and some completely strange inconsistencies. Especially touches when DSP Builder does not notice the established Matlab point-blank, and at least what you are doing!

')

But the author himself found a very stable bundle. Therefore, I will only talk about the version that comes with the 11.0th Quartus. She, fortunately, finds without problems and clings to Matlab, dearly beloved by the author, version 7.9 (in the author's opinion, the best after the famous version 6.5). After successful installation, two libraries should appear in Simulinka: Altera DSP Builder Blockset and Altera DSP Builder Advanced Blockset. And the corresponding section in the Matlab help and examples links. The examples, I must say, are very obvious and cover almost all typical tasks encountered in the plisovodam.

If your DSP Builder was bundled with Quartus and before installing megafunctions (and this is probably the case), then megafunctions should be picked up. We type the alt_dspbuilder_setup_megacore command in the Matlab command window and get:

The team will definitely work with an error, this is due to the fact that an extremely limited number of megafunctions support (and at the same time correctly support) the clinging to Simulink. Most likely, except for the six shown in Fig. blocks, nothing else to pick up and fail. If you still have the feeling that someone else supports Simulink, then you can simply manually transfer the files to the temporary directory from the <where Quartus> \ libraries subdirectory and run alt_dspbuilder_setup_megacore again and again. There is a chance that something else clings.

The use of these blocks is somewhat specific to the Simula. The fact is that at the beginning Simulin does not know which parameters you would like to choose for the mega-function used, so at first it will look like a “black box” in your model:

After that, you click on it and the standard configuration window for this mega-function drops out, which you saw a hundred times in the Mega Wizard Plug-In Manager. But now, after selecting the parameters, “Manager” knows that you also want to generate files for Simula. And, about a miracle, now your block becomes a normal simulinkovsky block:

DSPbuilder initially supports a certain number of “starter whales”. This support boils down to the fact that DSPbuilder “knows” where you have connected lights, where are the buttons, and where (even!) Hangs sma. To the surprise of the author, there is even a familiar 4th Stratix board in the list. But the list is extremely limited. For example, the author is currently working with a DE2-115 board with a stone from the Cyclone IVE series. And she, alas, this version is not supported.

The question arises: is it possible to add a description of your board with your hands? We will answer. Well, first of all, nobody needs it. And, secondly, it is done very simply.

We climb into the <where_DSPbuilder> \ lib \ boardsupport \ boards directory and see files with the .board extension. Next, copy any of the files that describes the most related to us fee (in my case - this is Cyclone_III_EP3C120.board), open and edit it. The file format is so clear that it is even funny. But if it is still not clear, then open the DSP Builder Handbook, Volume 2: DSP Builder Standard Blockset p.137 and read.

Despite the fact that everything is clear, the description of the new board must be done very carefully, so that later not scribbling messages in conferences like: “help, dspbuilder gives an error ...”. You can even change the board image in the same directory. Next, you need to inform DSPbuilder of the new board. This is done by the alt_dspbuilder_createComponentLibrary command. After it has been worked out (and it will probably fly out with an error, but you need to score for it), you will happily see your board in the “libraries” sub-library. By the way, in a similar way a new binary component can be screwed to the board. For example, a non-standard indicator, joystick button, rail switch, external bus, etc.

The main advantage of DSP Builder is not only the preparation of projects for FPGAs, but also the ability to upload and check them in the “live gland” without leaving Simulink. The method of preparing the initial contents of the RAM and ROM directly from the Matlab variables, and not with the help of crookedly written utilities, confusing to the bit depths and encodings, also relates to this. And, not least, check the work of the project using the very convenient graphical toolkit Simulinka, rather than scribbling text "workbenches" on dozens of pages for the constantly falling "Modelsima" (although this is possible in DSP Builder'e).

DSP Builder offers two tools for testing. The first is “HIL” (Hardware-in-the-loop, which in Russian can be translated as “real hardware inside the model”). Here, you must first assemble a project of the system under study, and then create a “covering” model, where your system will be a HIL-subsystem, separated from the model space by inputs and outputs, input and output, respectively. It sounds difficult, but open the FreqSweep example from the Tutorials and everything will become clear.

By the way, some pleasovods think that HIL uses SignalTap. Actually, SignalTap has nothing to do with the HIL methodology. But SignalTap can also be used with DSP Builder, and this is the second way. In order to enable SignalTap, you need to use the “SignalTap II Logic Analyzer” block from the “AltLab” library. There is a limitation when using SignalTap - only one clock signal (the rest are perceived as normal inputs). But, frankly, how often do we use several clock regions in SignalTap?

Regarding the optimality of the generated code. DSPbuilder is, in essence, a translator from Simulink's graphics to the selected HDL code. Open the generated project and see the main file. You will see that DSPbuilder simply verbally "described" the connection of blocks in your simulinkovsky project. Similarly, you would have done when manually transferring to the HDL code. It follows that the level of optimality of the project depends only on you. Use mega-function for, for example, CIC-filter - one result, too lazy to read the description, or do not want to get involved in commercial bark and decide to write with your hands - another result. All the same!

In conclusion, briefly about connecting their blocks. As the author mentioned at the beginning, in his opinion DSPbuilder is a revolution unnoticed by anyone. A good tone, therefore, is considered a style when you don’t crawl out of DSPbuilder at all and gradually forget that there are any AHDLs and Verilogs, Quartuses and Synplicity. With such an approach, in theory, even

By the way, DSPbuilder allows you to completely control the project settings from the Simulin frame. For this, there are corresponding blocks in the AltLab sub-library. From DSPbuilder, you can work perfectly with SOPC Builder (well, if someone likes to insert a processor with very little features into an expensive plisin). But, the author hears the right question: how can one not leave the environment at all, when, after all, we need to dock with the outside world? With the same Ethernet Ethernet, com-port, etc. etc. In fact, for this you need to write the corresponding component yourself. Here you can act in three ways.

The first, the most difficult and almost impracticable, is to create your own mega-function, go through the IP Certifications process (in my opinion not for free, who knows, correct), and then read above. By the way, not such a fantastic way. The author spent some time creating a new mega-function for one of the CAD manufacturers for FPGAs. But then you only have to do this and nothing else.

The second way is to write a new block using Simula. But, a true pleisovod sniffs contemptuously at such a method.

Well, the third way is to drag your HDL code into the framework of Simulink. For this case in the DSPbuilder'e block provides «HDL Import». This is a whole process that the author can describe later in a separate post, but this is the most realistic way that, believe me, it’s worth spending time once.

Source: https://habr.com/ru/post/238821/

All Articles