Dialectics of the SATA Revolution

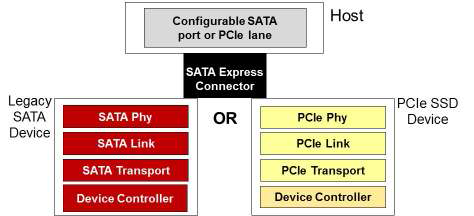

The decision was made: starting with the 9th series chipset, hard drives are connected directly to the PCI Express bus , bypassing the SATA controller. As a result, the performance of the disk subsystem increases one and a half to two times in compliance with all the requirements of the AHCI standard, i.e. without loss of software compatibility:

The decision was made: starting with the 9th series chipset, hard drives are connected directly to the PCI Express bus , bypassing the SATA controller. As a result, the performance of the disk subsystem increases one and a half to two times in compliance with all the requirements of the AHCI standard, i.e. without loss of software compatibility:

Such is the tip of the iceberg. What are the long-term consequences associated with innovation? Referring to the NVM Express specification, which regulates the logic of the solid-state drive on the PCIe bus.

')

A few words about Non-Volatile Memory Host Controller Interface Specification

The place of the NVMe interface is perfectly illustrated by the article by Dale Landsman from SanDisk "AHCI and NVMe as Interfaces for SATA".

The place of the NVMe interface is perfectly illustrated by the article by Dale Landsman from SanDisk "AHCI and NVMe as Interfaces for SATA".It will be useful for all those interested to learn that “ AHCI has been slowing down the media-based storage subsystem . Such an interface has some inherent devices where it can be much more DRAM than spinning media . ”

In other words, the AHCI controller was developed under the rule of electromechanical drives in order to optimize their interaction with the system. In particular, changing the sequence of data transfer commands to minimize the mechanical movements of the block of magnetic heads, as well as optimal synchronization of the processes of reading and writing with the rotation of the disk. Obviously, for solid-state drives that use other principles of information storage and operating at high speeds, the use of AHCI architecture is a temporary solution dictated by compatibility requirements. Full disclosure of the speed potential of SSD drives, as well as support for modern virtualization technologies will become possible only when using a controller optimized for this type of drives.

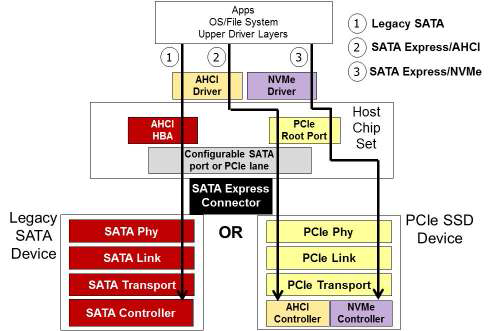

The above illustrates three possible methods for connecting a storage device:

- Legacy SATA - traditional SATA drive;

- SATA Express / AHCI - a drive with a physical SATA Express interface and an integrated controller compatible with the AHCI standard;

- SATA Express / NVMe - a drive with a physical SATA Express interface and an integrated controller with NVMe architecture.

SR-IOV as a mirror of the hardware revolution

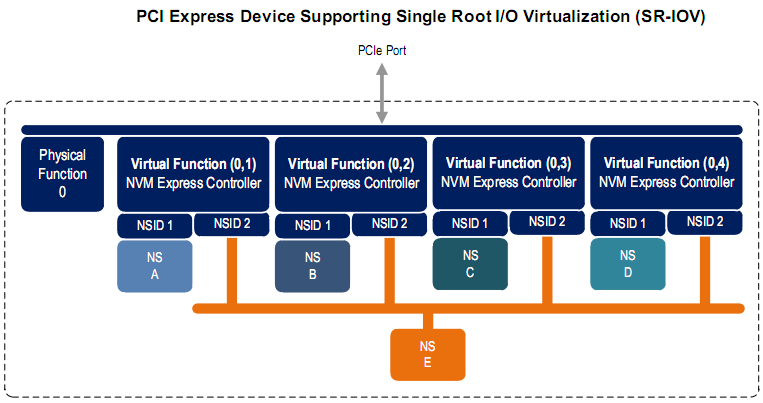

Let's return to the NVMe specification. When developing it, the possibility of supporting Single-Root Input-Output Virtualization was initially taken into account:

Those who are unfamiliar with the SR-IOV concept will say in a nutshell that this is the essence of the further development of the idea of virtualization that has come to the periphery. A physical device with the help of SR-IOV is represented as a set of virtual devices with all the ensuing consequences: access control, performance enhancement, etc. Currently, virtualization of the VT-x central processor is used, address space virtualization is used for bus-master VT-d devices, but progress towards the virtualization of peripheral devices is still difficult. Or rather this: the market is already full of network adapters that support SR-IOV, but

There is, however, one "but." Since the NVMe controller becomes part of the hard disk, and the drive itself is connected as a PCI Express device, SR-IOV support will depend not only on the chipset and platform, but also on the drive. This means a further divergence of amateur (office) and professional (server) equipment. These are the prospects for the future, in our opinion.

Used Books

- AHCI and NVMe as Interfaces for SATA Express Devices . Dave Landsman, SanDisk

- SATA Express PCIe Client Storage . Paul Wassenberg, SATA-IO

- PCIe SSD 101 : An Overview of Standards, Markets and Performance. Eden Kim, Tom Coughlin, Walt Hubis, Chuck Paridon, Doug Voigt, Paul von Behren, Jack Hollins, Paul Wassenberg, Kristen Hopper, Doug Rollins, Jim Handy, Tony Roug, Marty Czekalski, PCIe SSD Committee

- Specification NVM Express , Rev.1.1b

Source: https://habr.com/ru/post/229819/

All Articles