JTAG interface? - It's very simple

Many are familiar with the word "JTAG", but familiarity is most likely superficial. In this article, I want to take you to a new level, so to speak, “in a friendly zone”. Perhaps for many I will not reveal anything new, but I hope those who have long wanted to familiarize themselves will be interested in reading. So, from the screw.

In 1985, a group of electronics manufacturers, the JTAG (Joint Test Action Group), was formed. To solve the problems of testing in 1990, an industry standard was put forward - the IEEE Std 1149.1-1990 specification (IEEE Standard Test Access Port and Boundary-Scan Architecture). In the same year, Intel released the first processor with the JTAG - 80486. Since then, the standard is constantly being modified and, at the moment, the latest version dates back to 2013.

"And what are the problems with testing?", - you ask. Well, of course! It is not enough fun to jump with an oscilloscope on the conclusions of the chip, especially if there are a lot more than two! The standard makes it possible to significantly simplify life by embedding a special architecture in modern chips, which provides access to outputs (more precisely, to special I / O units) using a 4-wire serial interface. This architecture allows not only to control their state, but also to manage them. Thus, you can do without bulky probes with physical contact and enjoy the beauty of the debugging stage of digital circuits or circuit board level devices.

The standard is used both for in-circuit programming and debugging programs, as well as when working with packaged microcircuits. It is also used to check the quality of the soldering of the microcircuits to the board, interboard and intra-articular mounting of boards and blocks. You also need to thank him for restoring the mobile devices, zakirpichchennyh carelessly.

')

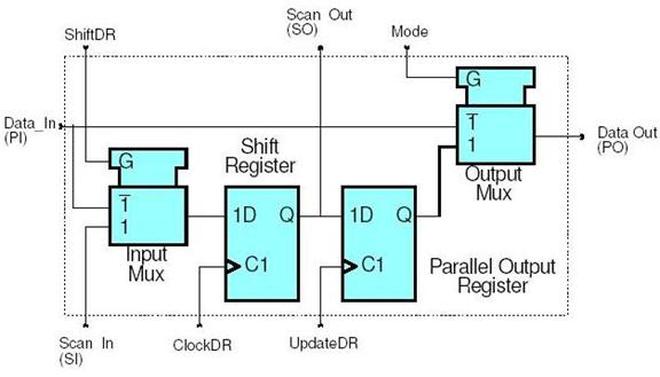

The mechanism of boundary scanning is concluded only in a shift register (Boundary Scan), connected between the outputs of the chip and the core, and a multiplexer that connects this register at the right moment. The so-called “cells” correspond to each specific conclusion.

The cell includes one trigger register of boundary scanning and data multiplexing multiplexer. Cells can be of different types depending on the output of the chip and interface commands, i.e. depends on the manufacturer of a particular chip. Manufacturers do not adhere strictly to the standard and, therefore, divorced many modifications.

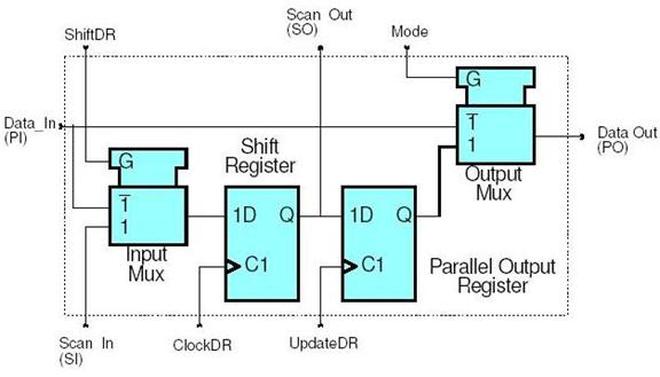

The figure shows one of the varieties of the cell. PI, PO - parallel input and output, SI, SO - sequential.

The signals to the microcircuit register go through a multiplexer that allows you to read both the states of the microcircuit's pins (INTEST instruction) and data coming from outside to the shift register (EXTEST instruction). Varieties of instructions and their functionality again vary from the wishes of the manufacturer, but there are so-called mandatory:

As mentioned above, the JTAG interface has the following signal lines:

JTAG is a synchronous interface, signals are received on the leading edge of sync pulses with low bits forward and only during the states of the TAP - Shift-DR \ Shift-IR controller. The output is pushed forward.

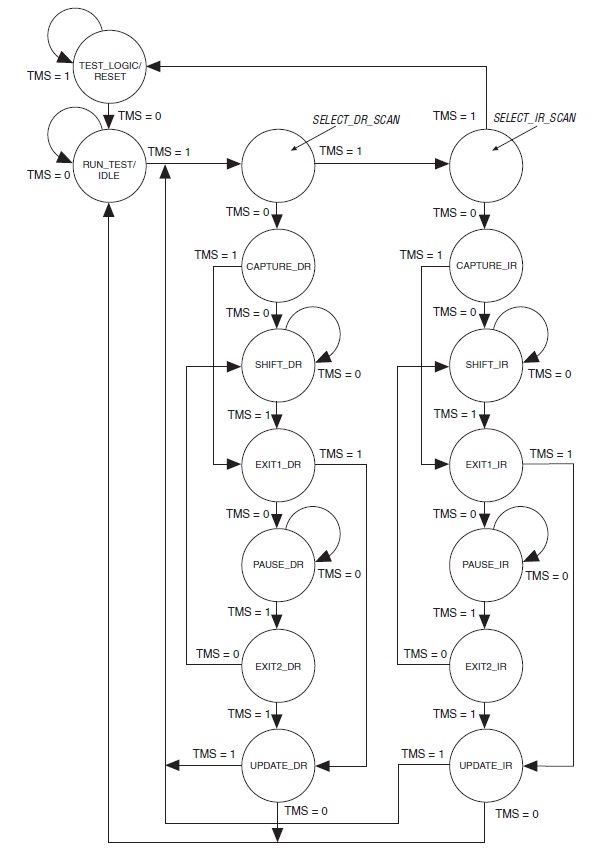

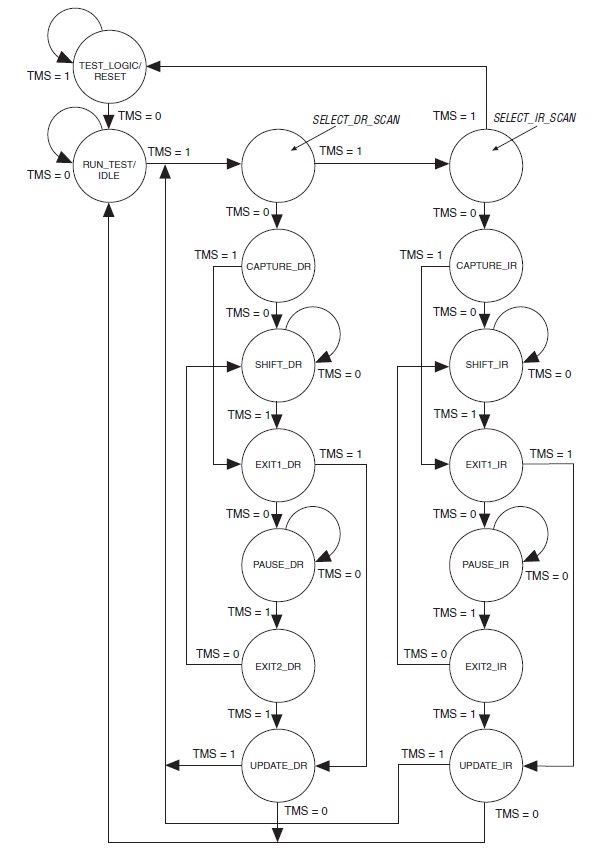

We got to the very essence of JTAG, namely, the machine manager. With its help, everything actually lives around. The machine has 16 states. The interface is controlled by affecting the machine through a TMS signal. Transitions occur on the leading edge of the TCK signal. Reading and writing data occur simultaneously. Below is an illustration of the work, taken from the documentation of Altera microcircuits.

Transition diagram of the automaton controlling TAP modes

Transition diagram states:

The initial state in which the automaton is located after switching on is Test-Logic Reset. As long as the TMS signal is “log.1”, the state of the automaton remains unchanged. In this state, by default, an IDCODE or BYPASS statement is selected.

The TRST reset signal is not mandatory, therefore, the following procedure is used to reset the automaton to its initial state. It is necessary to apply a high level signal to the TMS input and hold it for at least 5 TCK clock cycles. If the TMS signal is set to low by the host, the machine will go to the Run-Test / Idle state (active state in which nothing happens). Usually, from this state, you can go to the Select-IR state in order to load a new instruction into the controller. But if the TMS signal input is not affected by the signal from the host, but by a low level interference, then, as in the previous case, the machine will go into Run-Test / Idle state. If the short-term interference (with a duration of no more than one period of the synchronization frequency) stops, then the machine will return to its original state after three cycles - Test-Logic Reset.

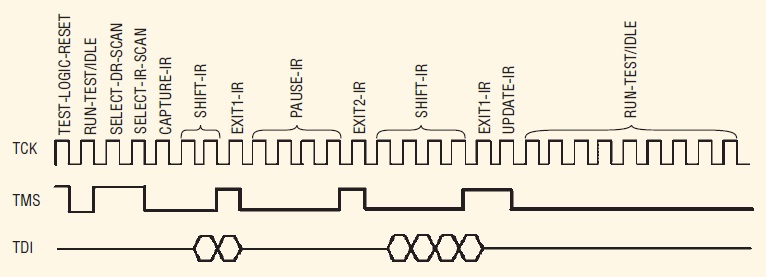

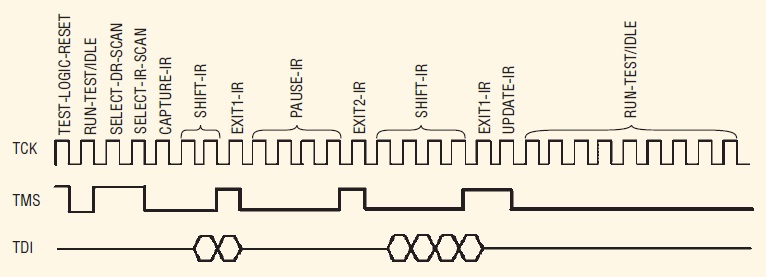

To load a new command into the controller, from the Run-Test / Idle state it is necessary to transfer the machine to the Select-IR, Capture-IR, Shift-IR state. Then it is necessary to “push” the new command into the data chain, and then transfer the machine through the states Exit1-IR, Update-IR and again into Run-Test / Idle. The logic of working with data is the same. It should be borne in mind that the high level signal during the transition from the Shift-IR \ DR states is fed along with the last bit of information.

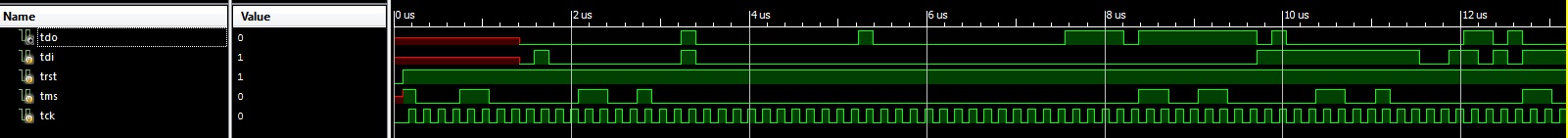

Signal diagram when performing transitions to load a command

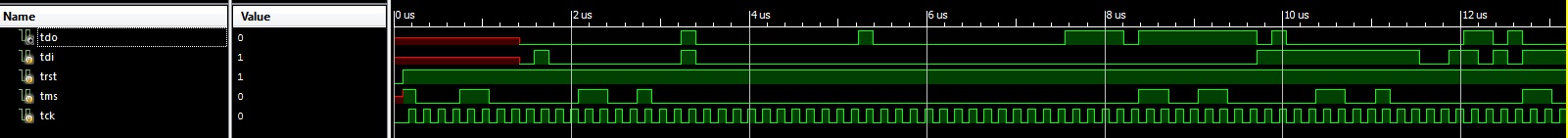

If using specialized CAD software to write the JTAG code for Verilog, the resulting diagram will look something like this:

Dropbox link, full size picture

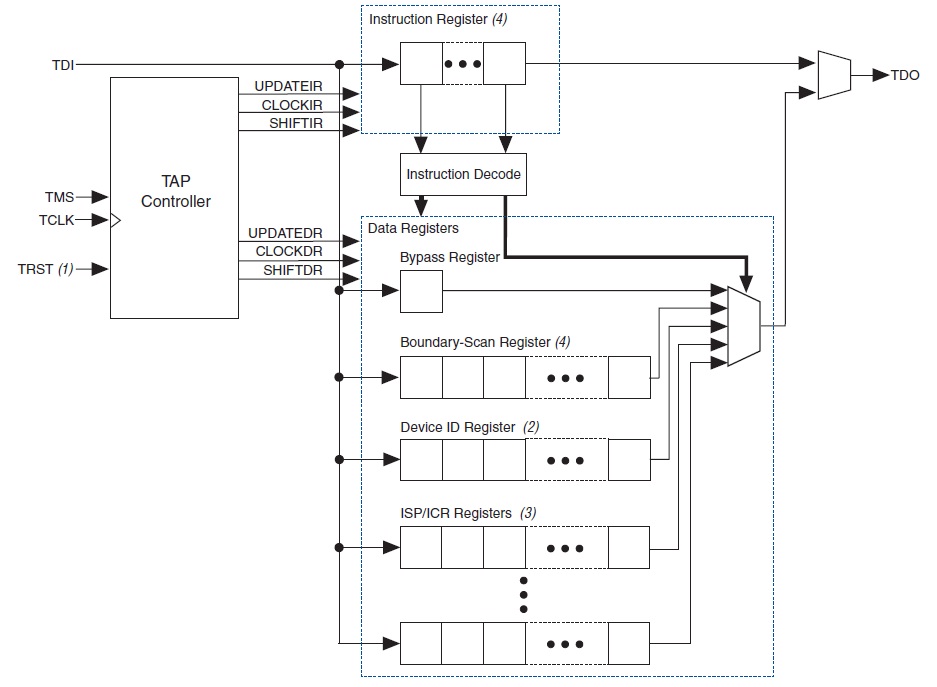

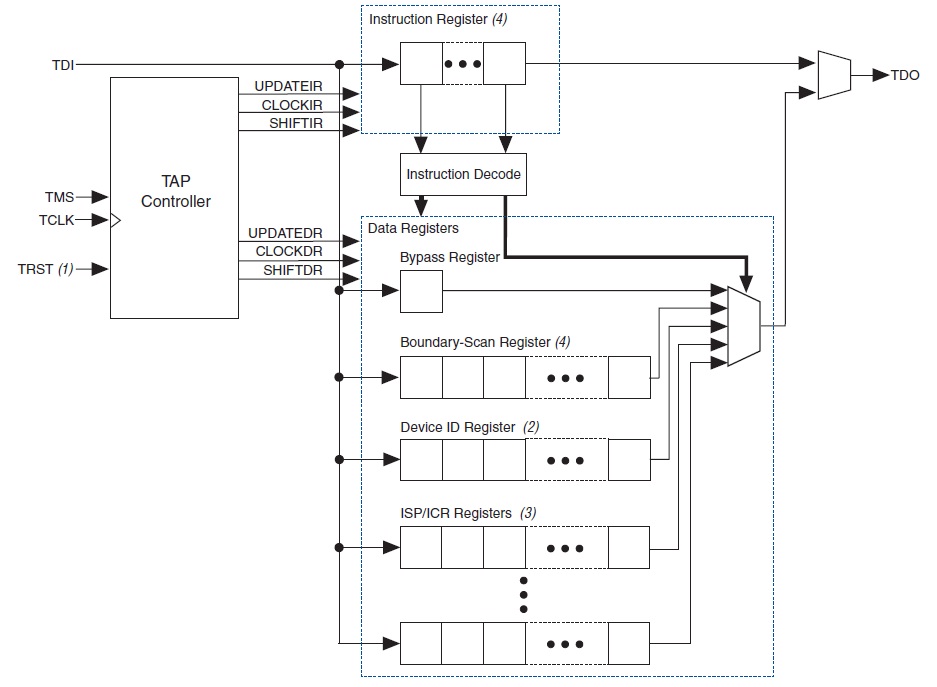

Finally, you can show the complete block diagram of a JTAG device and you should understand it completely:

Using JTAG and edge scanning technology in a chip, on a board, or in a device adds value and increases project development time. But, nevertheless, these costs easily pay for themselves during testing, which is provided at each stage of the product life cycle. What was originally developed as a production test tool is used prior to production, during mass production and after production, that is, during the operation phase by the end user. In addition to directly boundary testing, designers use JTAG technology to perform self-testing (BIST) (in those components where it is implemented) and load internal values into device registers or program ROM chips. Tests that were developed and used at the design stage can be transferred to production in order to provide an additional reduction in the cost and time to check the products at the output control. improved "coverage" of the test product when searching for errors and diagnosing and improved test performance while reducing test time.

The use of boundary scanning in the operation of the product also has a certain positive effect. Operational failures often occur due to structural failures, which are caused by elevated temperature, humidity, and vibration. Using boundary scanning, technicians are able to quickly check the product for structural errors down to the component level without time-consuming research or returning the board to the manufacturer at the factory.

Literature:

Wiki

Boundary-scan in Altera devices

off IEEE 1149.1 working group page

1149.1-2013 - IEEE Standard for Test Access and Boundary-Scan Architecture

Good habro article that touches JTAG testing

release of EEVblog about Killy JTAG

The article used some data from the magazine "Modern Electronics" issue №2 2007.

Introduction

In 1985, a group of electronics manufacturers, the JTAG (Joint Test Action Group), was formed. To solve the problems of testing in 1990, an industry standard was put forward - the IEEE Std 1149.1-1990 specification (IEEE Standard Test Access Port and Boundary-Scan Architecture). In the same year, Intel released the first processor with the JTAG - 80486. Since then, the standard is constantly being modified and, at the moment, the latest version dates back to 2013.

"And what are the problems with testing?", - you ask. Well, of course! It is not enough fun to jump with an oscilloscope on the conclusions of the chip, especially if there are a lot more than two! The standard makes it possible to significantly simplify life by embedding a special architecture in modern chips, which provides access to outputs (more precisely, to special I / O units) using a 4-wire serial interface. This architecture allows not only to control their state, but also to manage them. Thus, you can do without bulky probes with physical contact and enjoy the beauty of the debugging stage of digital circuits or circuit board level devices.

The standard is used both for in-circuit programming and debugging programs, as well as when working with packaged microcircuits. It is also used to check the quality of the soldering of the microcircuits to the board, interboard and intra-articular mounting of boards and blocks. You also need to thank him for restoring the mobile devices, zakirpichchennyh carelessly.

')

And how does it work?

The mechanism of boundary scanning is concluded only in a shift register (Boundary Scan), connected between the outputs of the chip and the core, and a multiplexer that connects this register at the right moment. The so-called “cells” correspond to each specific conclusion.

The cell includes one trigger register of boundary scanning and data multiplexing multiplexer. Cells can be of different types depending on the output of the chip and interface commands, i.e. depends on the manufacturer of a particular chip. Manufacturers do not adhere strictly to the standard and, therefore, divorced many modifications.

The figure shows one of the varieties of the cell. PI, PO - parallel input and output, SI, SO - sequential.

The signals to the microcircuit register go through a multiplexer that allows you to read both the states of the microcircuit's pins (INTEST instruction) and data coming from outside to the shift register (EXTEST instruction). Varieties of instructions and their functionality again vary from the wishes of the manufacturer, but there are so-called mandatory:

- EXTEST is a manual that allows you to check external circuits directly related to the component under test by setting logical values on the working contacts of electronic components.

- INTEST - instruction provides the ability to set the logical values inside the chip, that is, at the inputs of the kernel, thereby checking it.

- SAMPLE_PRELOAD - allows you to test the core of an electronic element in a static mode, setting the values of logic levels on the border of its output buffers.

- BYPASS is an instruction in which our boundary scan register “collapses” into one trigger. At the same time, data from the input (TDI) to the output (TDO) is transmitted with a delay of one clock frequency of the interface synchronization frequency (TCK). This mode allows you to effectively use the capabilities of the serial interface when organizing long sequentially joined chains.

- IDCODE - the instruction pushes the output value of the built-in 32-bit register with the identifiers of the manufacturer, model and version of the device.

Interface signal lines

As mentioned above, the JTAG interface has the following signal lines:

- TDI - Test Data Input - the data signal to the input, the data is pushed on the leading edge of the TCK.

- TDO - Test Data Output - the output of the serial data JTAG, pushed on the trailing edge of the TCK, must be in the third state - Z - when the data is not transmitted.

- TMS - Test Mode Select - control signal TAP - controller.

- TRST - Test Reset - is not always there, since the reset can be achieved by holding TMS = 1 for some time, the active signal level is 0.

- TCK - Test Clock - clock frequency.

JTAG is a synchronous interface, signals are received on the leading edge of sync pulses with low bits forward and only during the states of the TAP - Shift-DR \ Shift-IR controller. The output is pushed forward.

TAP - controller

We got to the very essence of JTAG, namely, the machine manager. With its help, everything actually lives around. The machine has 16 states. The interface is controlled by affecting the machine through a TMS signal. Transitions occur on the leading edge of the TCK signal. Reading and writing data occur simultaneously. Below is an illustration of the work, taken from the documentation of Altera microcircuits.

Transition diagram of the automaton controlling TAP modes

Transition diagram states:

- Test-Logic-Reset - the initial state;

- Run-Test / Idle - the transition state of the controller when running tests or waiting for the next

- teams;

- Select-IR, Select-DR - the state after which the commands and data will be tested;

- Capture-IR, Capture-DR - the state of receiving commands, data;

- Shift-IR, Shift-DR - the state of the shift commands, data;

- Exit1-IR, Exit2-IR - exit from the mode of working with commands;

- Exit1-DR, Exit2-DR - exit from the data mode;

- Pause-IR, Pause-DR - pause state;

- Update-IR, Update-DR - the state of overwriting data in the output registers.

The initial state in which the automaton is located after switching on is Test-Logic Reset. As long as the TMS signal is “log.1”, the state of the automaton remains unchanged. In this state, by default, an IDCODE or BYPASS statement is selected.

The TRST reset signal is not mandatory, therefore, the following procedure is used to reset the automaton to its initial state. It is necessary to apply a high level signal to the TMS input and hold it for at least 5 TCK clock cycles. If the TMS signal is set to low by the host, the machine will go to the Run-Test / Idle state (active state in which nothing happens). Usually, from this state, you can go to the Select-IR state in order to load a new instruction into the controller. But if the TMS signal input is not affected by the signal from the host, but by a low level interference, then, as in the previous case, the machine will go into Run-Test / Idle state. If the short-term interference (with a duration of no more than one period of the synchronization frequency) stops, then the machine will return to its original state after three cycles - Test-Logic Reset.

To load a new command into the controller, from the Run-Test / Idle state it is necessary to transfer the machine to the Select-IR, Capture-IR, Shift-IR state. Then it is necessary to “push” the new command into the data chain, and then transfer the machine through the states Exit1-IR, Update-IR and again into Run-Test / Idle. The logic of working with data is the same. It should be borne in mind that the high level signal during the transition from the Shift-IR \ DR states is fed along with the last bit of information.

Signal diagram when performing transitions to load a command

If using specialized CAD software to write the JTAG code for Verilog, the resulting diagram will look something like this:

Dropbox link, full size picture

Finally, you can show the complete block diagram of a JTAG device and you should understand it completely:

… In conclusion...

Using JTAG and edge scanning technology in a chip, on a board, or in a device adds value and increases project development time. But, nevertheless, these costs easily pay for themselves during testing, which is provided at each stage of the product life cycle. What was originally developed as a production test tool is used prior to production, during mass production and after production, that is, during the operation phase by the end user. In addition to directly boundary testing, designers use JTAG technology to perform self-testing (BIST) (in those components where it is implemented) and load internal values into device registers or program ROM chips. Tests that were developed and used at the design stage can be transferred to production in order to provide an additional reduction in the cost and time to check the products at the output control. improved "coverage" of the test product when searching for errors and diagnosing and improved test performance while reducing test time.

The use of boundary scanning in the operation of the product also has a certain positive effect. Operational failures often occur due to structural failures, which are caused by elevated temperature, humidity, and vibration. Using boundary scanning, technicians are able to quickly check the product for structural errors down to the component level without time-consuming research or returning the board to the manufacturer at the factory.

Literature:

Wiki

Boundary-scan in Altera devices

off IEEE 1149.1 working group page

1149.1-2013 - IEEE Standard for Test Access and Boundary-Scan Architecture

Good habro article that touches JTAG testing

release of EEVblog about Killy JTAG

The article used some data from the magazine "Modern Electronics" issue №2 2007.

Source: https://habr.com/ru/post/190012/

All Articles