Solving problems with naming conventions in Quartus II using Schematic

Hello, Habrosoobschestvo.

I would like to share with you the solution of one problem I encountered and solved for quite some time. And a bunch of different radio electronics (to whom I turned for help and advice), as well as 2 domestic and 1 foreign radio electronics forums, could not help solve this problem.

I want to make it so that the one who reads this will never “stand up for a rake”, to which I stood up and with whom I suffered for a long time.

')

The problem was that I could not use more than 1 pin on one IDC connector. If the connector used more than 1 pin (2 or more) - then when checking the oscilloscope connector was silent.

As it turned out now - the problem was the naming rules in Quartus II using Schematic.

To all those to whom it will be useful or interesting - I ask for cat.

Faced with this problem and on the target (handmade) devices. But for clarity, I would like to demonstrate Altera DE1 on a whale (Figure 1).

Fig. 1 - Altera DE1 Development and Education Board

I uploaded the file “Altera_DE1_pin_assignments.csv” with the pin assignments of the FPGA (Name in the project - Pin number of the FPGA) that I took from the disk from the whale to Quartus II.

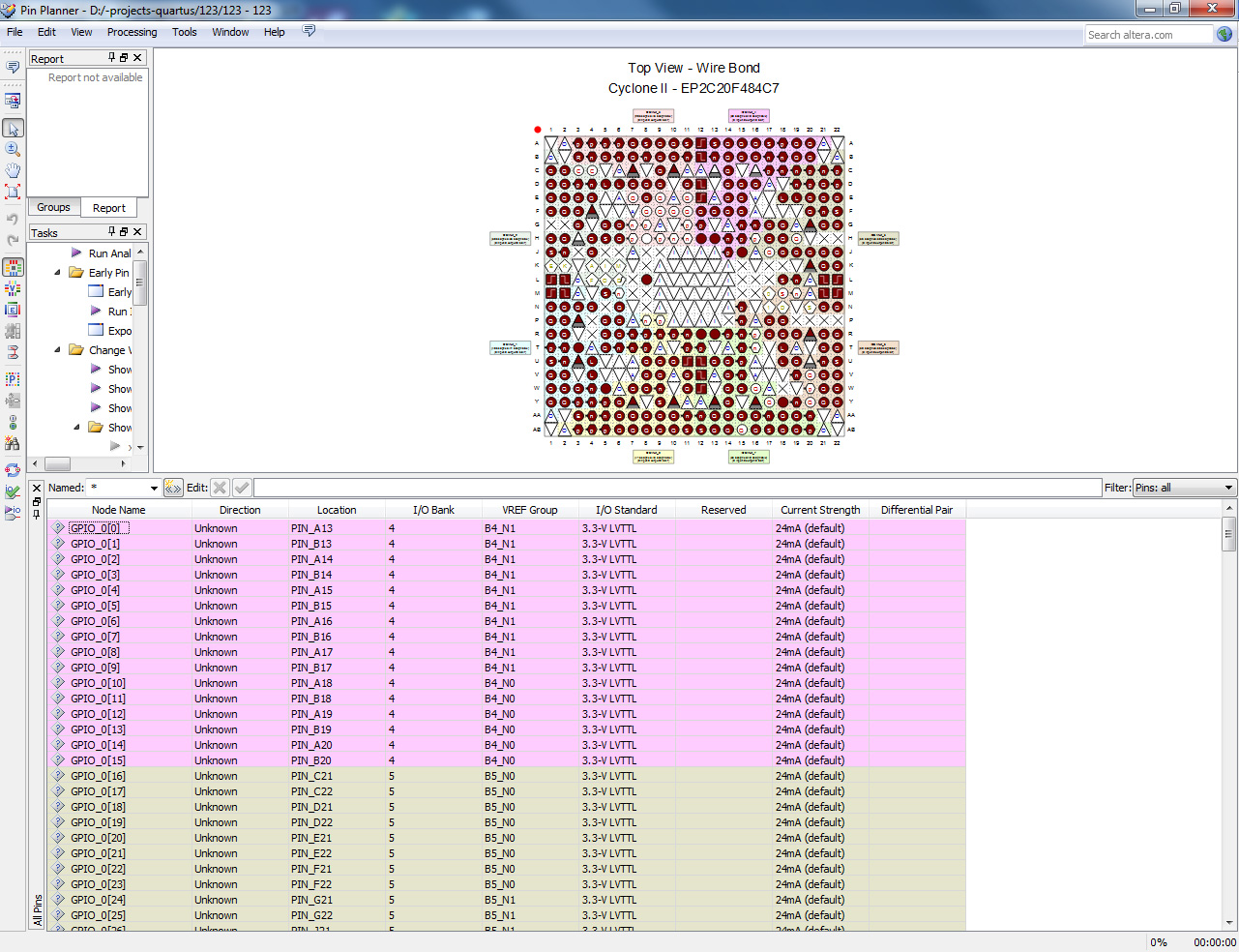

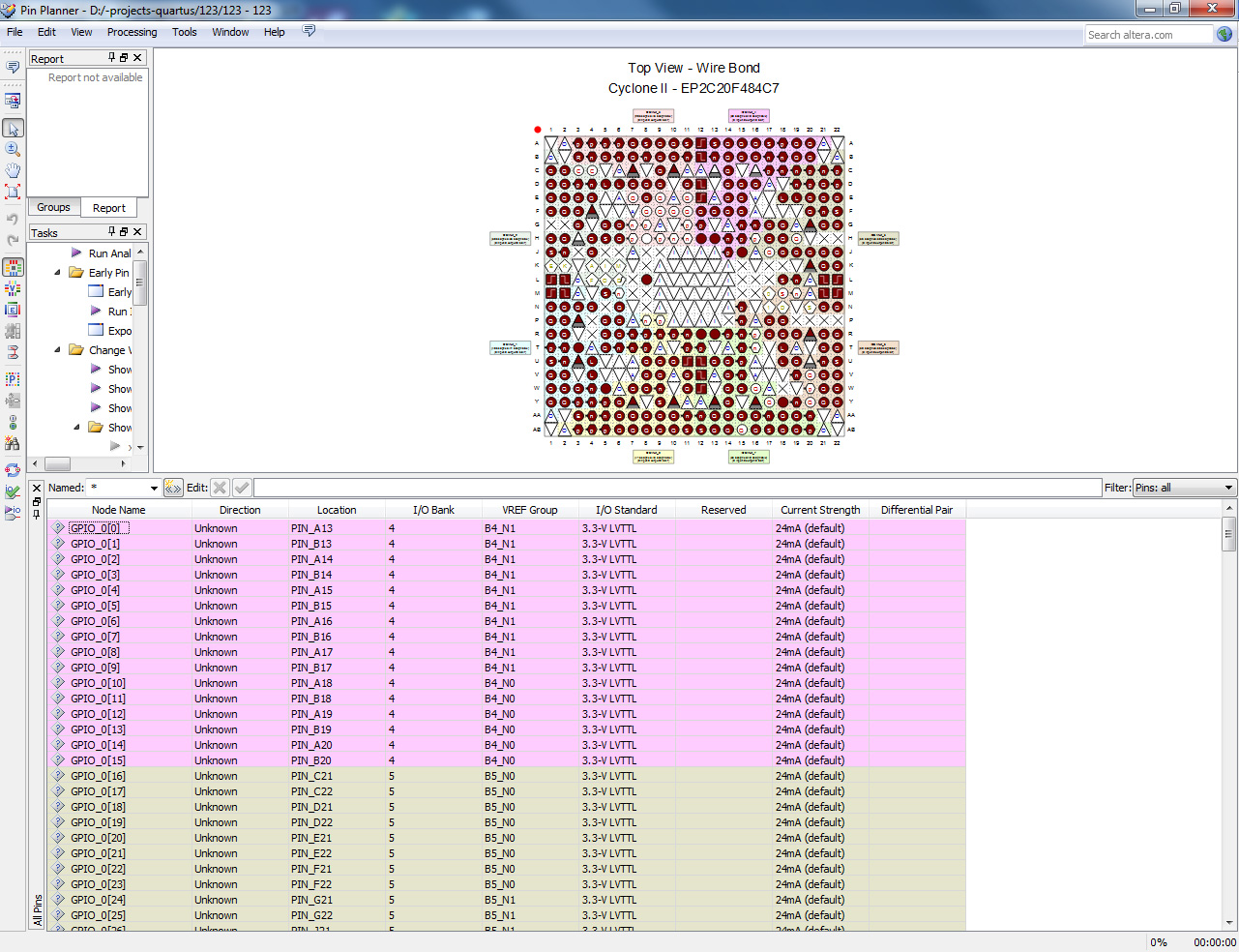

In Figure 2 you can see the names of the forty-pin IDC pins of the “GPIO_0” connector in the Pin Planner.

Fig. 2 - Quartus II Pin Planner for Altera DE1

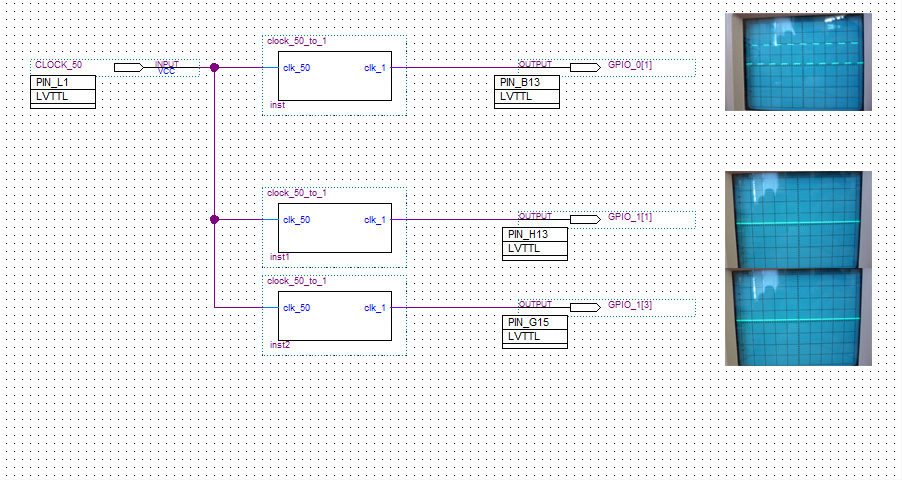

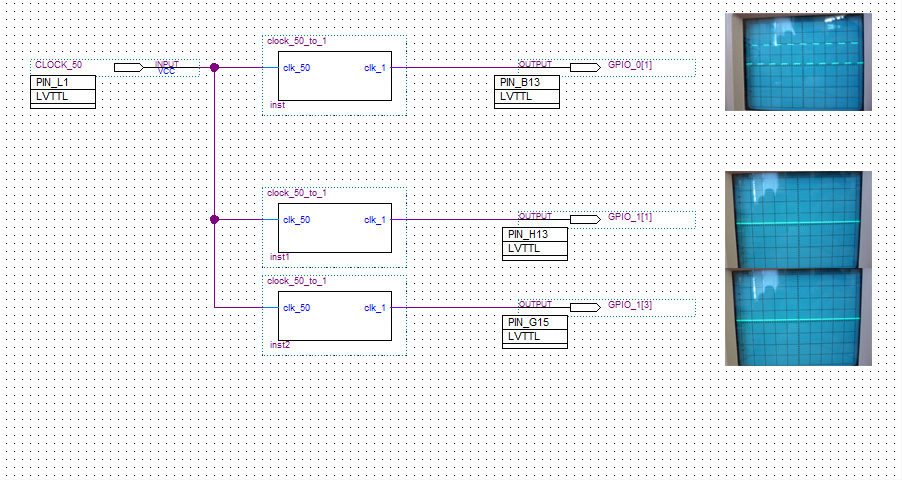

For clarity, I will describe the problem in more detail on the project shown in Figure 3. A pin of 50 MHz comes from the CLOCK_50 pin (from the clock generator on the whale, which is connected to a specific FPGA pin). “Clock_50_to_1” is a handwritten module in the Verilog language, which converts a 50 MHz clock into 1 MHz by means of a counter (similar problems were observed when using the ALTPLL mega-function built into Quartus II). The converted shred is output to 2 IDC connectors - GPIO_0 and GPIO_1. On the GPIO_0 connector, 1 pin ([1]) is used and everything works, on the GPIO_1 connector, 2 pins ([1], [3]) are used and there is no signal.

Fig. 3 - Screenshot of Quartus II and oscilloscope photos

One of the users of the Altera Forum , noticed “out of the corner of the eye” some strange warnings when compiling a project (shown in Figure 3) in Quartus II, and said: “I haven’t come across this, I don’t know what to do, but I advise you to do the top-level module of the project is not in schematic, but in Verilog or VHDL ”

In short, after analyzing the warnings, it became clear that Quartus II renames

“GPIO_1 [1]” in “GPIO_11”

“GPIO_1 [3]” in “GPIO_13”

And for the names GPIO_11 and GPIO_13, specific FPGA pins are not assigned.

So we found out that there are two renaming schemes - Max + Plus II and Quartus II.

For a project, you can explicitly switch these naming rule schemes:

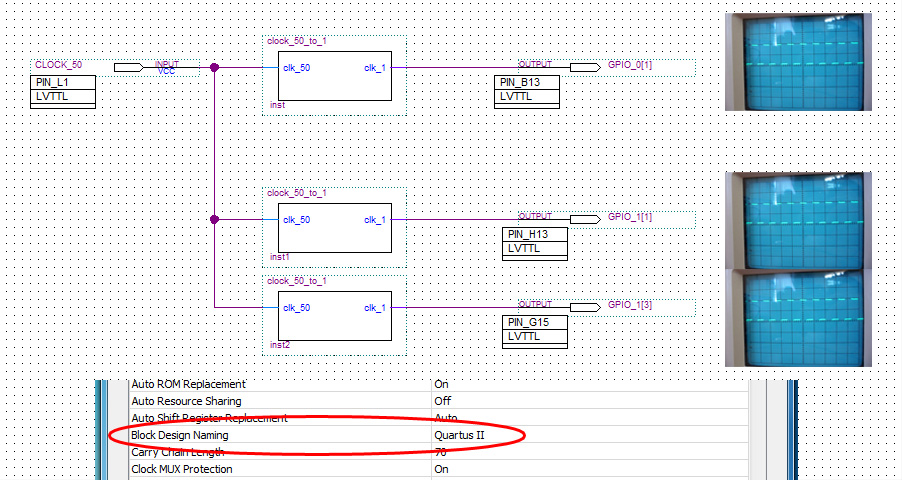

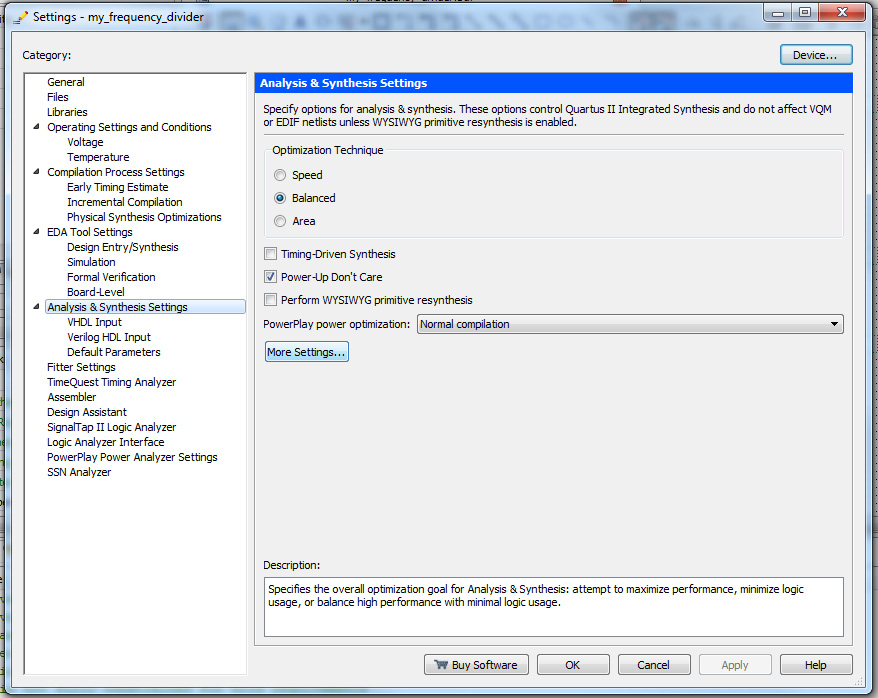

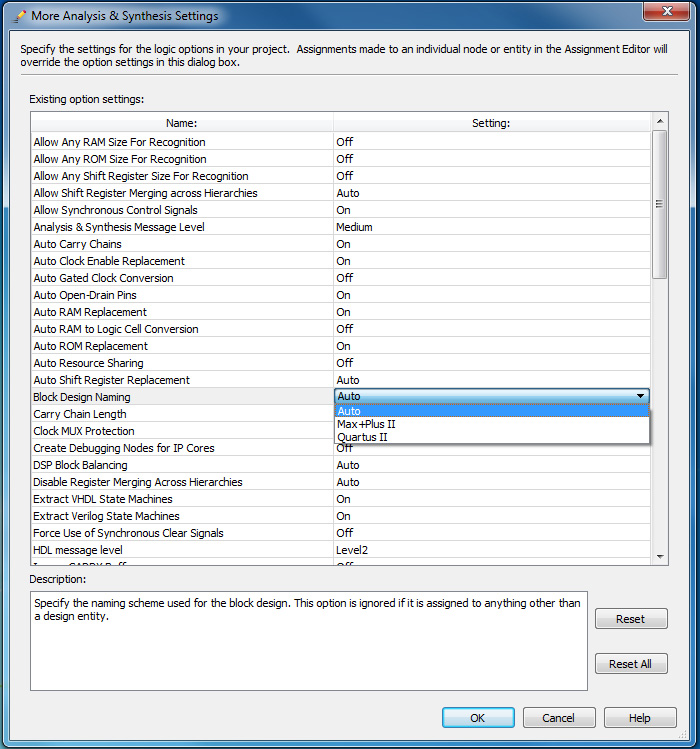

Assignments => Settings => Analysis & Synthesis Settings => More Settings => Block Design Naming

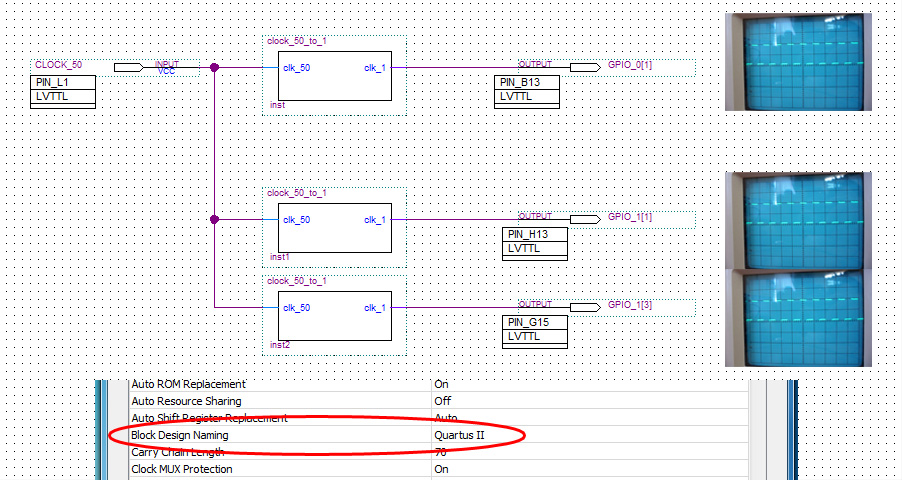

As can be seen from Figure 4, if you explicitly switch the renaming scheme to Quartus II, then the problem is solved.

Fig. 4 - Screenshot of Quartus II and oscilloscope photos

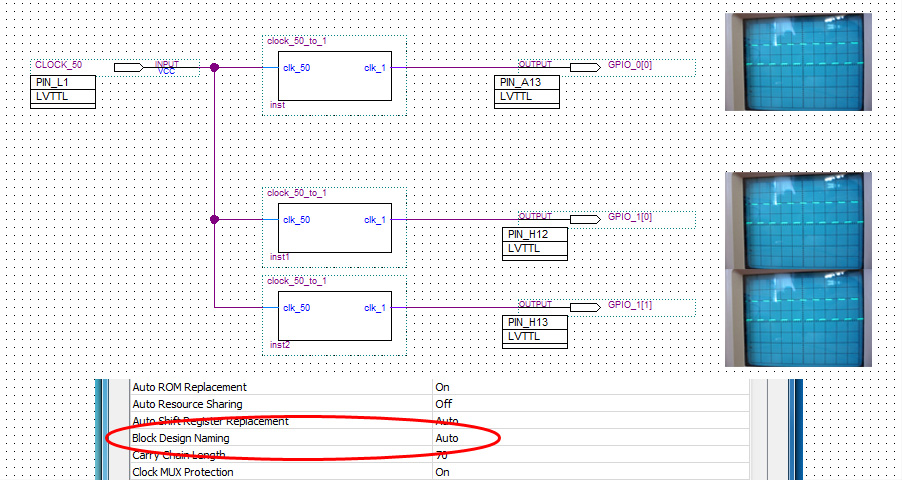

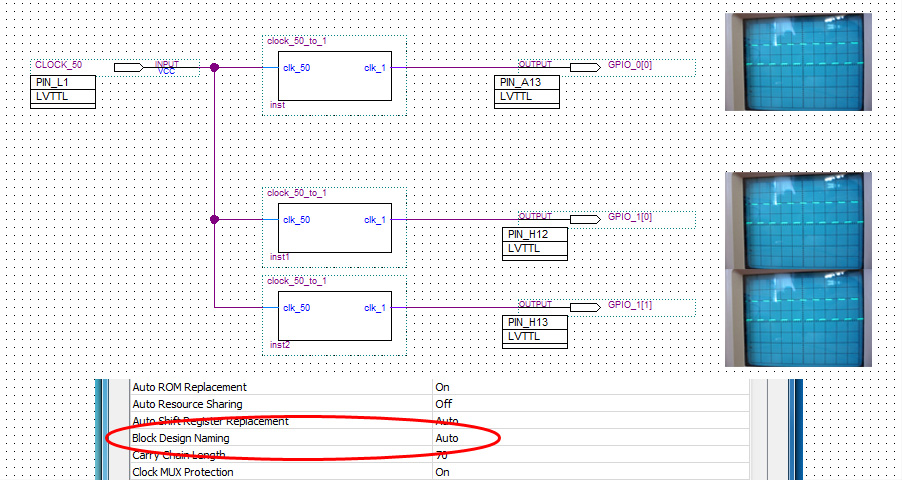

If you start using the IDC pins of the connector in order (from 0 to n), then even with the Auto renaming scheme set, Quartus II will not rename anything.

Fig. 5 - Screenshot of Quartus II and oscilloscope photos

PS I will be very happy if I can make life easier for someone and save his time.

I would like to share with you the solution of one problem I encountered and solved for quite some time. And a bunch of different radio electronics (to whom I turned for help and advice), as well as 2 domestic and 1 foreign radio electronics forums, could not help solve this problem.

I want to make it so that the one who reads this will never “stand up for a rake”, to which I stood up and with whom I suffered for a long time.

')

The problem was that I could not use more than 1 pin on one IDC connector. If the connector used more than 1 pin (2 or more) - then when checking the oscilloscope connector was silent.

As it turned out now - the problem was the naming rules in Quartus II using Schematic.

To all those to whom it will be useful or interesting - I ask for cat.

Demonstration of the problem

Faced with this problem and on the target (handmade) devices. But for clarity, I would like to demonstrate Altera DE1 on a whale (Figure 1).

Fig. 1 - Altera DE1 Development and Education Board

I uploaded the file “Altera_DE1_pin_assignments.csv” with the pin assignments of the FPGA (Name in the project - Pin number of the FPGA) that I took from the disk from the whale to Quartus II.

In Figure 2 you can see the names of the forty-pin IDC pins of the “GPIO_0” connector in the Pin Planner.

Fig. 2 - Quartus II Pin Planner for Altera DE1

For clarity, I will describe the problem in more detail on the project shown in Figure 3. A pin of 50 MHz comes from the CLOCK_50 pin (from the clock generator on the whale, which is connected to a specific FPGA pin). “Clock_50_to_1” is a handwritten module in the Verilog language, which converts a 50 MHz clock into 1 MHz by means of a counter (similar problems were observed when using the ALTPLL mega-function built into Quartus II). The converted shred is output to 2 IDC connectors - GPIO_0 and GPIO_1. On the GPIO_0 connector, 1 pin ([1]) is used and everything works, on the GPIO_1 connector, 2 pins ([1], [3]) are used and there is no signal.

Fig. 3 - Screenshot of Quartus II and oscilloscope photos

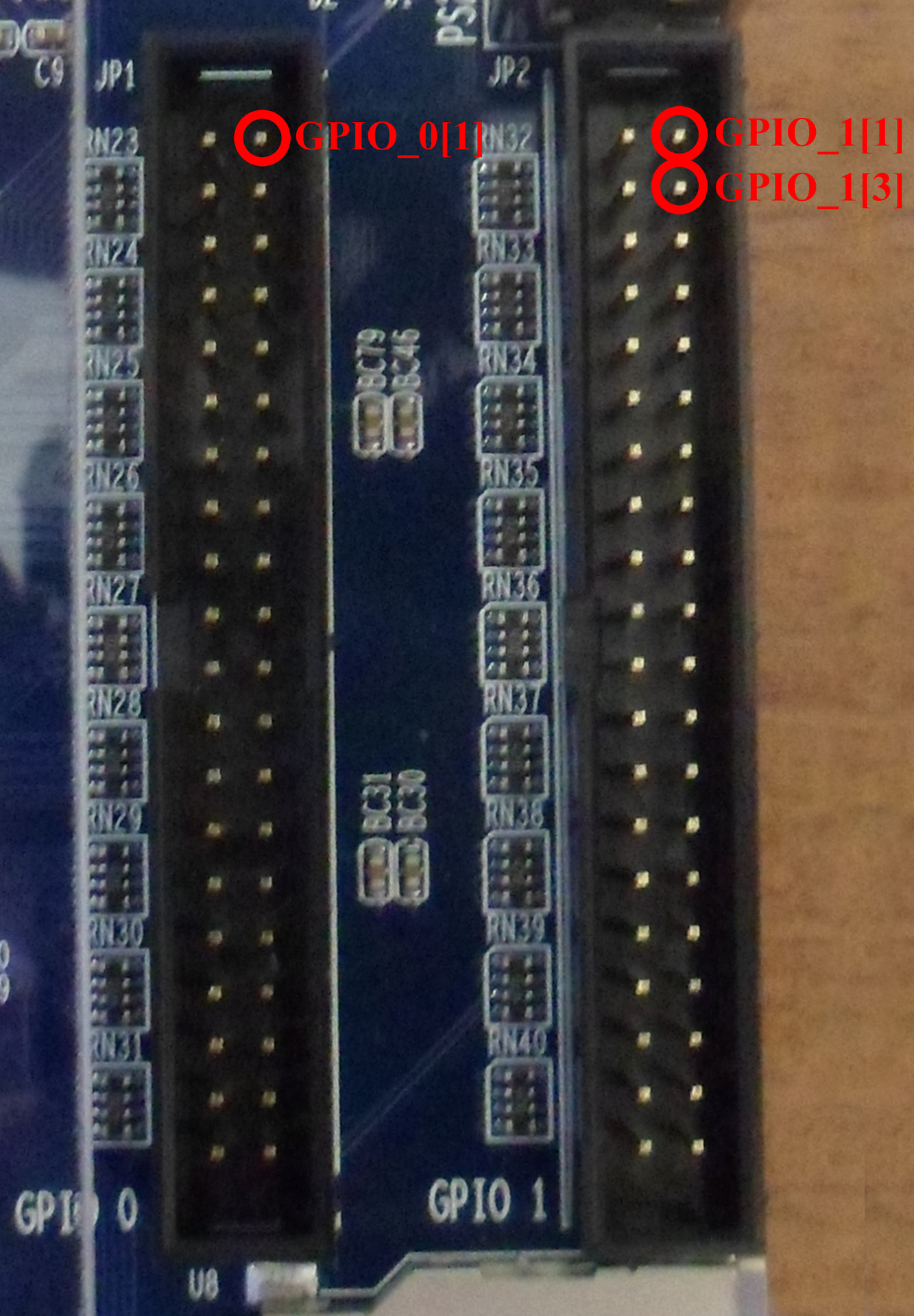

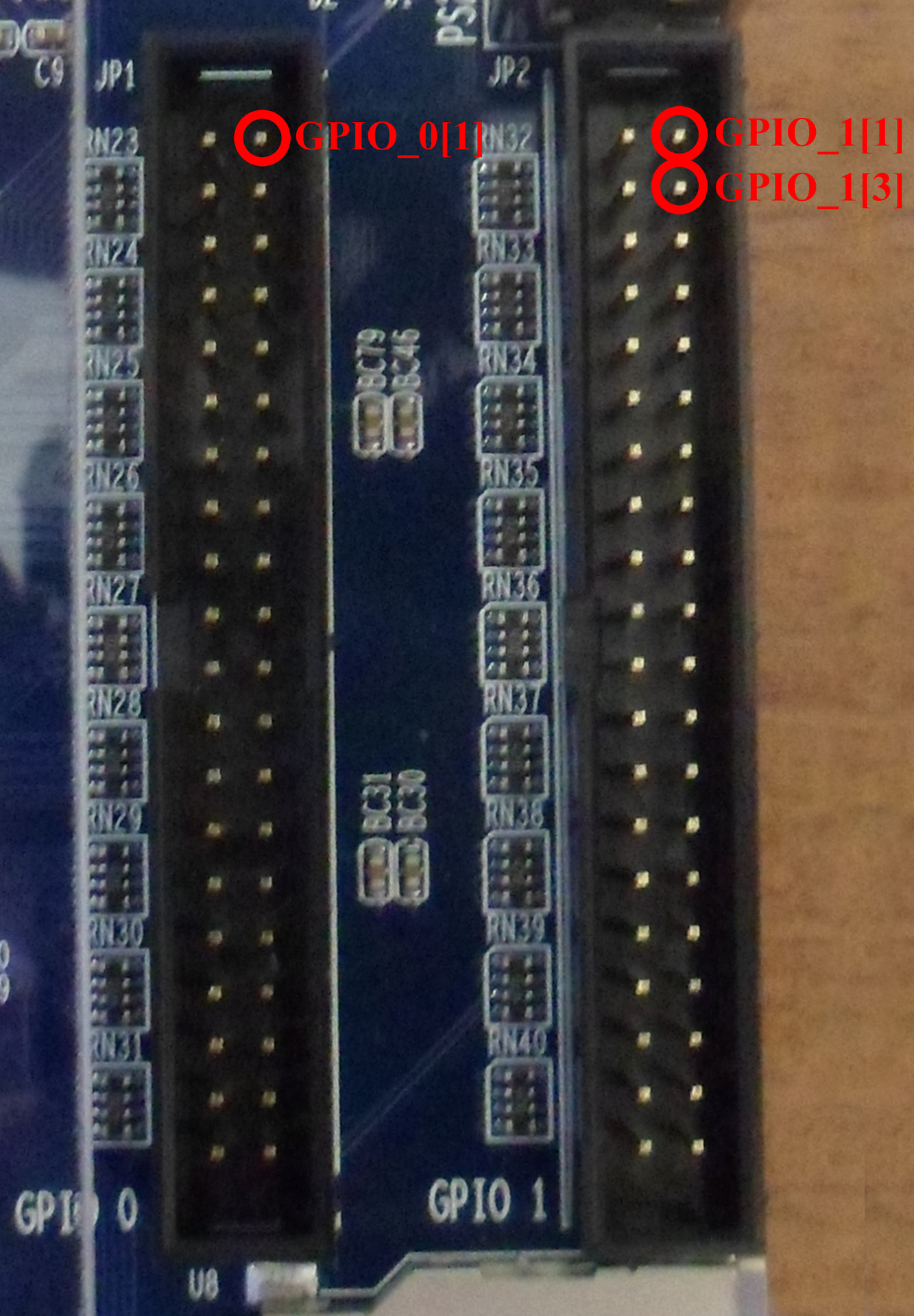

For clarity, the picture in the spoiler is a picture of the connectors:

Cause of the problem

One of the users of the Altera Forum , noticed “out of the corner of the eye” some strange warnings when compiling a project (shown in Figure 3) in Quartus II, and said: “I haven’t come across this, I don’t know what to do, but I advise you to do the top-level module of the project is not in schematic, but in Verilog or VHDL ”

The warning text is as follows:

Warning (275080): Converted elements in bus name "GPIO_1" using legacy naming rules. Make any assignments on the original names.

Warning (275080): The transformed elements in the tire named “GPIO_1” use inherited naming rules. Make any assignments for new names, not for original names.

- Warning (275081): Converted element name (s) from “GPIO_1 [1]” to “GPIO_11”

- Warning (275081): Converting the element name from “GPIO_1 [1]” to “GPIO_11”

- Warning (275081): Converted element name (s) from "GPIO_1 [3]" to "GPIO_13"

- Warning (275081): Converting the element name from “GPIO_1 [3]” to “GPIO_13”

Critical Warning (169085): No exact pin location assignment (s) for 2 pins of 4 total pins

Special Importance Warning (169085): No pin (s) assigned to 2 pins from 4 pins in total

- Info (169086): Pin GPIO_11 not assigned to an exact location on the device

- Information (169086): The exact location of the GPIO_11 pin on the device is not assigned

- Info (169086): Pin GPIO_13 not assigned to an exact location on the device

- Information (169086): The exact location of the GPIO_13 pin on the device is not assigned

Warning (275080): The transformed elements in the tire named “GPIO_1” use inherited naming rules. Make any assignments for new names, not for original names.

- Warning (275081): Converted element name (s) from “GPIO_1 [1]” to “GPIO_11”

- Warning (275081): Converting the element name from “GPIO_1 [1]” to “GPIO_11”

- Warning (275081): Converted element name (s) from "GPIO_1 [3]" to "GPIO_13"

- Warning (275081): Converting the element name from “GPIO_1 [3]” to “GPIO_13”

Critical Warning (169085): No exact pin location assignment (s) for 2 pins of 4 total pins

Special Importance Warning (169085): No pin (s) assigned to 2 pins from 4 pins in total

- Info (169086): Pin GPIO_11 not assigned to an exact location on the device

- Information (169086): The exact location of the GPIO_11 pin on the device is not assigned

- Info (169086): Pin GPIO_13 not assigned to an exact location on the device

- Information (169086): The exact location of the GPIO_13 pin on the device is not assigned

In short, after analyzing the warnings, it became clear that Quartus II renames

“GPIO_1 [1]” in “GPIO_11”

“GPIO_1 [3]” in “GPIO_13”

And for the names GPIO_11 and GPIO_13, specific FPGA pins are not assigned.

What about this is stated in the Altera knowledge base:

Max + Plus II software has limited support for bus names in the schematics and will sometimes rename the items in the bus to work within these limits.

For example, the Max + Plus II software would rename the bus names a [1..0], b [1], b [0] to a1, a0, b1, b0, respectively.

Quartus II software initially retained this behavior for backward compatibility, but now supports a method that preserves the natural tire names (with square brackets) in your design.

However, to avoid changing software behavior for existing projects, Quartus II continues to use older naming conventions for inheriting BDF (Block Design File) and GDF (Graphic Design File) project files.

For the new schematics, the Quartus II software stores the real names (with square brackets) in the project at compile time.

Naming rules for Quartus II version 7.1 and earlier versions:

(SCHEME OF RENAMING Max + Plus II):

If the bus a [0..3] is divided into parts, then 4 pins are created: a0, a1, a2, a3

Naming rules for Quartus II version 7.2 and later:

(SCHEME OF RENAMING QUARTUS II):

If the bus a [0..3] is divided into parts, then 4 pins are created: a [0], a [1], a [2], a [3]

For example, the Max + Plus II software would rename the bus names a [1..0], b [1], b [0] to a1, a0, b1, b0, respectively.

Quartus II software initially retained this behavior for backward compatibility, but now supports a method that preserves the natural tire names (with square brackets) in your design.

However, to avoid changing software behavior for existing projects, Quartus II continues to use older naming conventions for inheriting BDF (Block Design File) and GDF (Graphic Design File) project files.

For the new schematics, the Quartus II software stores the real names (with square brackets) in the project at compile time.

Naming rules for Quartus II version 7.1 and earlier versions:

(SCHEME OF RENAMING Max + Plus II):

If the bus a [0..3] is divided into parts, then 4 pins are created: a0, a1, a2, a3

Naming rules for Quartus II version 7.2 and later:

(SCHEME OF RENAMING QUARTUS II):

If the bus a [0..3] is divided into parts, then 4 pins are created: a [0], a [1], a [2], a [3]

The way to solve problem №1

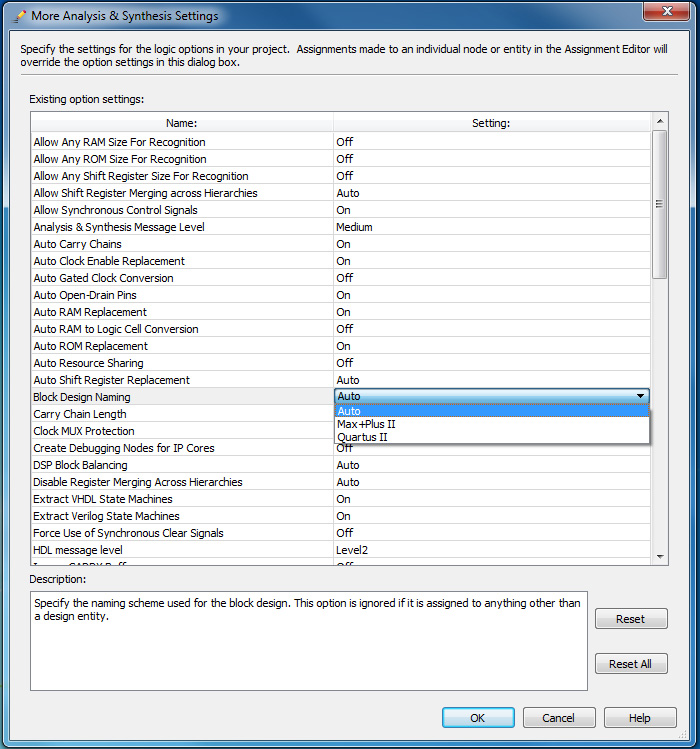

So we found out that there are two renaming schemes - Max + Plus II and Quartus II.

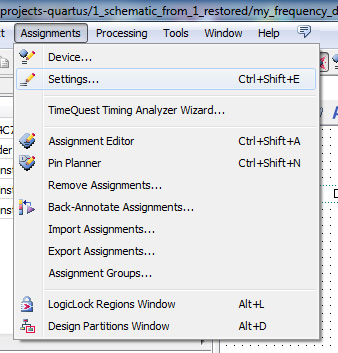

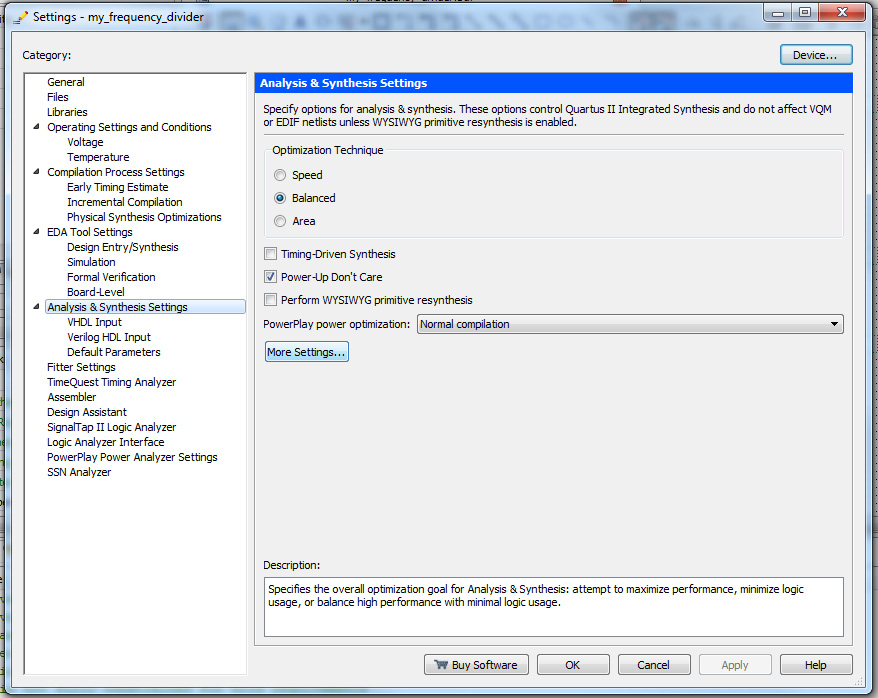

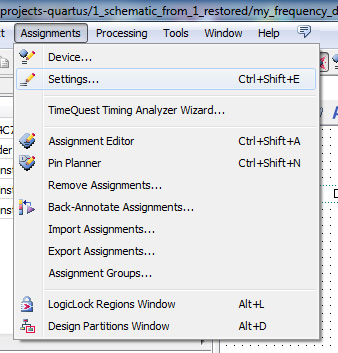

For a project, you can explicitly switch these naming rule schemes:

Assignments => Settings => Analysis & Synthesis Settings => More Settings => Block Design Naming

For clarity in the spoiler, screenshots of switching renaming rules by steps:

As can be seen from Figure 4, if you explicitly switch the renaming scheme to Quartus II, then the problem is solved.

Fig. 4 - Screenshot of Quartus II and oscilloscope photos

The solution to the problem number 2

If you start using the IDC pins of the connector in order (from 0 to n), then even with the Auto renaming scheme set, Quartus II will not rename anything.

Fig. 5 - Screenshot of Quartus II and oscilloscope photos

For clarity, the picture in the spoiler is a picture of the connectors:

PS I will be very happy if I can make life easier for someone and save his time.

Source: https://habr.com/ru/post/184032/

All Articles