Obtained photos of the crystal of the specialized bitcoin processor Avalon

2 months ago I wrote that the first customers began to receive specialized computers for mining / supporting the Bitcoin network - Avalon. I immediately wrote to the developer Avalon'a - Yifu Guo, and he agreed to send me a few chips for the autopsy. However, the parcel is bogged down in the depths of Russian sloppy mail.

2 months ago I wrote that the first customers began to receive specialized computers for mining / supporting the Bitcoin network - Avalon. I immediately wrote to the developer Avalon'a - Yifu Guo, and he agreed to send me a few chips for the autopsy. However, the parcel is bogged down in the depths of Russian sloppy mail.Fortunately, I was contacted by needbmw - it turned out that Avalon came to him with one damaged chip, he was soldered and given to me bypassing the mail. Now we can finally glance at the inside of the processor. This will be especially interesting to many who want to develop their Avalon with blackjack and mow millions.

Photo

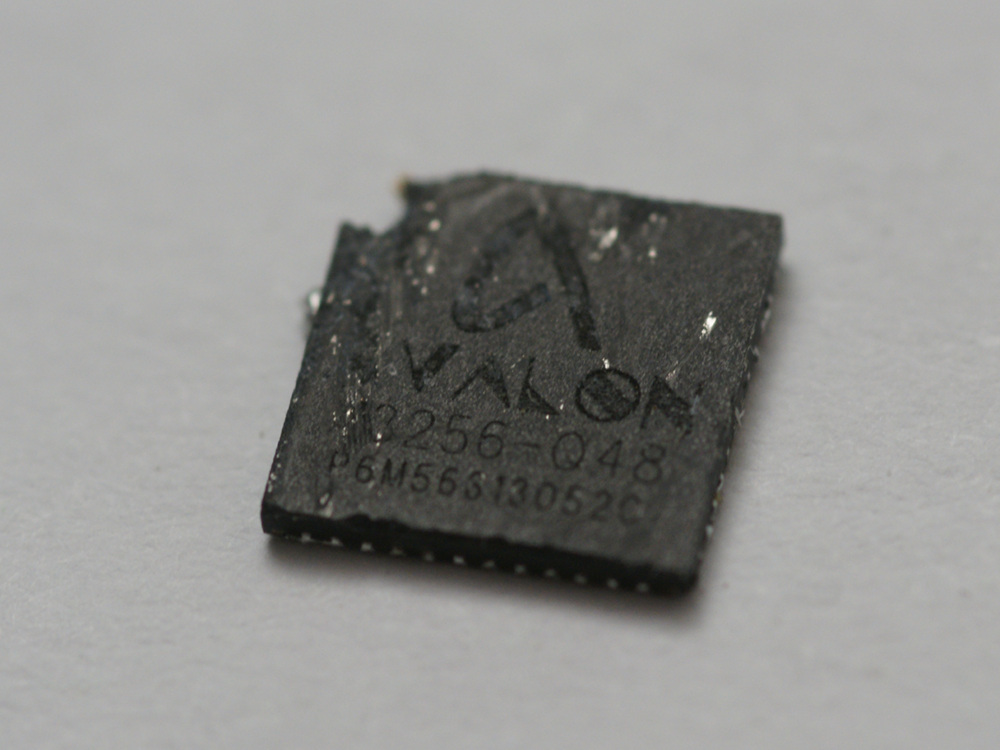

Damaged chip itself: (fortunately, theThis baby counts 282 Mhash / s (like an AMD 6970 graphics card), consuming ~ 2.5W.

')

From open sources it is known that the chip was manufactured at the TSMC factory using the 110nm process technology, 5 layers of metallization. Remarkably, the pads on the chip is much larger than the pins on the chip. Most of them are power / ground, respectively, one leg is connected to several pads on a microcircuit.

The size of the crystal - 4.06 * 4.12 mm.

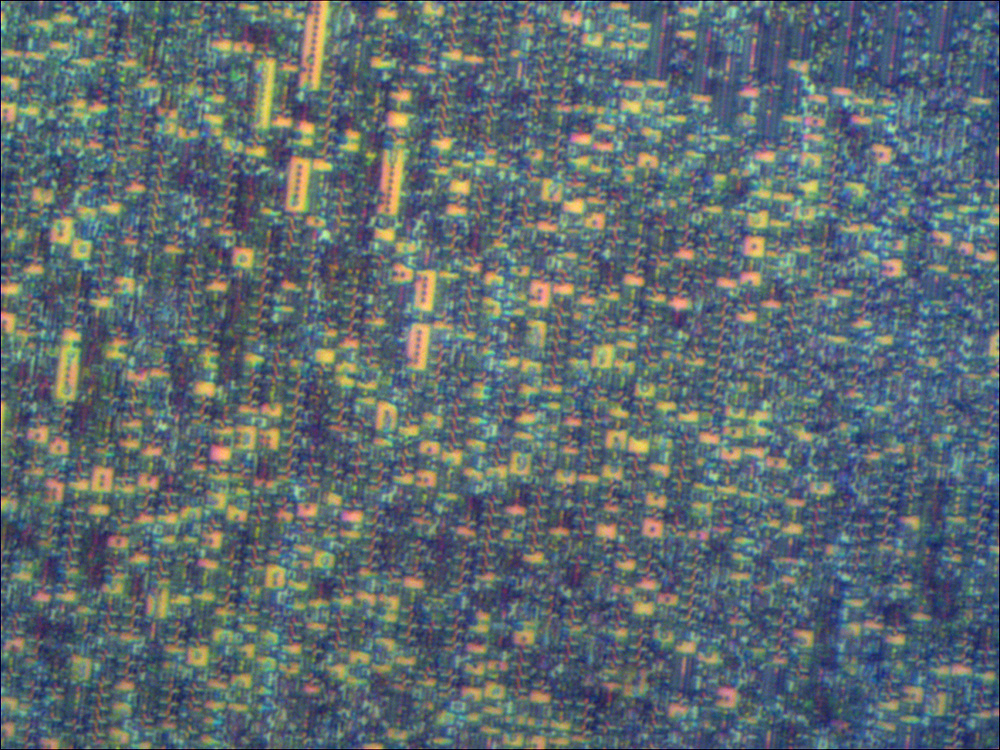

From above - we see only the power / ground distribution network, the whole "minced" - is hidden under the metal connections.

If you set off metallization, it is clear that Avalon is a huge monolithic piece of logic, no memory blocks, registers ... It is not a processor in the usual sense of the word. The square in the left part of the circuit is probably a PLL (external clock frequency multiplier) and auxiliary logic.

But the most interesting thing can be seen if you look at the chip under the maximum magnification (even despite the fact that all the details are not visible):

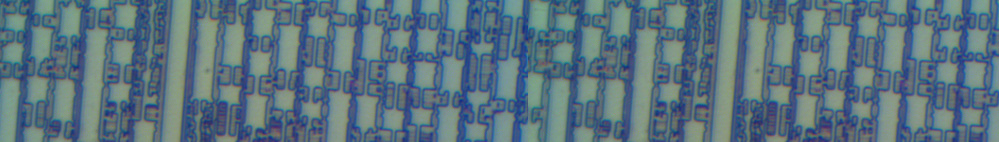

If you compare with a 180nm chip based on a library of standard cells scaled to 61%, we see that the logic of Avalon is much, much denser:

Summary

Avalon is real (not to be confused with ButterflyLabs, which have been feeding everyone with breakfast for over a year).Despite the fact that Yifu Guo assures everyone that everything is done in a hurry - the density of logic hints that at least some elements or blocks were drawn by hand.

So, if someone thinks to take a ready Verilog description of an opensource Bitcoin FPGA reader, and automatically synthesize your Avalon, it’s not so easy to create a competitive product, and an automatically synthesized version on the same process will be 2-4 times slower (at the same power consumption).

Source: https://habr.com/ru/post/182912/

All Articles