Plesiochronous digital hierarchy and E1 stream

Greetings, friends!

During the study of Digital transmission systems, as well as on the recommendation of a mentor, in order to better understand the material being studied and put everything on the shelves, I will try to explain this material to you, if I succeed in this, then we can assume that I learned it well. I hope you will be interested.

In the article I will tell briefly about the DSP and the features of their construction, PDH (PDH) and in more detail about the flow of E1 and its structure.

It will not be news for anyone that the main trend in the development of telecommunications worldwide is the digitalization of communication networks, which involves building a network based on digital transmission and switching methods. This is due to the following significant advantages of digital transfer methods over analog ones:

High noise immunity.

')

The requirements for DSPs are defined in the ITU-T G-series recommendations; this recommendation also presents two types of DSP hierarchies: plesiochronous digital hierarchy (PDH) and synchronous digital hierarchy (SDH). The primary signal for all types of DSPs is a digital stream with a transfer rate of 64 Kbps, called the main digital channel (BCC) [foreign sources: Basic Digital Circuit (BDC)] , Habré already described how the digitization of the PM channels is done in this article . The principle of time division multiplexing (WRC) [foreign sources: Time Division Multiply Access (TDMA), or Time Division Multiplexing (TDM)] is used to combine BCC signals into group high-speed digital signals.

The historically first plesiochronous digital hierarchy (PDH) [foreign sources: Plesiochronous Digital Hierarchy (PDH)] has European, North American, and Japanese varieties.

For digital streams, PDHI use the corresponding designations, for North American - T, Japanese - J (DS), European - E. Digital streams of the first level are designated as T1, E1, J1 of the second T2, E2, J2, etc ...

The European PDH has been adopted for use on Russian telecommunication networks.

The communication networks of the Russian Federation are operated by DSP PDH of domestic and foreign production. Domestic systems are called DSP with PCM (digital transmission systems with pulse code modulation). Instead of the hierarchy level, the system designation indicates the number of information BCCs of this system. Thus, the DSP of the first level of the hierarchy is designated ICM-30, the second - ICM-120, etc.

In the plesiochronous, “as if synchronous,” DSPs, the principle of the WRC is used, so correct restoration of the original signals at the reception is possible only with synchronous and in-phase operation of the generator equipment at the transmitting and receiving stations. For normal operation of a plesiochronous DSP, the following types of synchronization should be provided:

Clock synchronization ensures equal processing speeds of digital signals in linear and station regenerators, codecs and other DSP devices that process the signal with a clock frequency Ft.

There are several options for clock synchronization:

Loop synchronization is as follows. At the transmitting station, a digital synchronization signal (CC) is introduced into the group digital signal at the beginning of the cycle. At the receiving station, a clock signal receiver (PSS) is installed, which extracts the frame clock signal from the digital digital signal and thereby determines the start of the transmission cycle.

There are 3 types of flow E1:

Consider the frame structure of the transmission DSP PCM-30.

The E1 flow structure is defined in ITU-T Recommendation G.704. This stream is called the primary digital stream and is organized by combining 30 information BCC.

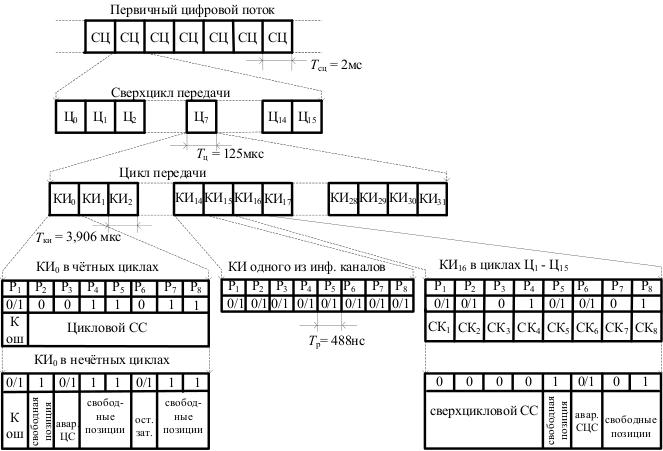

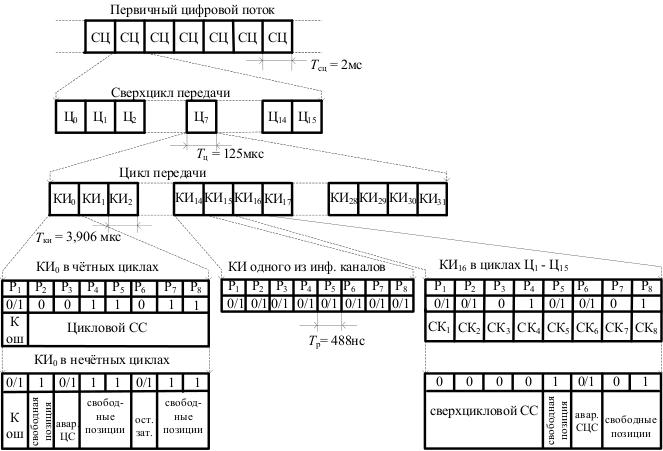

The linear signal of the system is built on the basis of superframes, cycles, channel and clock intervals, as shown in the figure above (0/1 designation corresponds to the transmission of a random signal in a given clock interval). The transmission super cycle (SC) corresponds to the minimum time interval for which one count of each of the 60 signaling channels (CK) and alarm transmission channels is transmitted (loss of frame or frame synchronization). Duration SC SC = 2ms. A supercycle consists of 16 transmission cycles (from Ts0 to Ts15). The cycle time TC = 125 µs and corresponds to the sampling interval of the channel of the PM with a frequency of 8 kHz. Each cycle is subdivided into 32 channel intervals (timeslot) with a duration Tq = 3.906 μs. Channel intervals KI1-KI15, KI17-KI31 are reserved for the transmission of information signals. KI0 and KI16 - under the transfer of proprietary information. Each channel interval consists of eight discharge intervals (P1-P8) with a duration of Tr = 488ns. Half of the discharge interval can be occupied by a rectangular pulse with a duration of Ti = 244 ns during transmission in a given discharge unit (there is no pulse in the discharge interval during transmission of zero). Intervals KI0 even-numbered cycles are intended to transmit the cyclic sync signal (DSS), having the form 0011011 and occupying the intervals P2 - P8. In the P1 interval of all cycles, the information of the permanent data transmission channel (DI) is transmitted. In odd cycles, the P3 and P6 CI0 intervals are used to transmit information about the loss of frame synchronization (Avar. CA - LOF) and reducing the residual attenuation of the channels to a value at which self-excitation may occur (OST). Intervals P4, P5, P7 and P8 are free, they are occupied by single signals to improve the operation of the clock frequency selectors. In the interval CI16 of the zero cycle (C0), a cyclic signal of the type 0000 (P1 - P4) is transmitted, as well as a signal on the loss of superframe synchronization (P6 - Avar. SDS - LOM). The remaining three bit intervals are free. In the channel interval CI16 of the remaining cycles (C1 - C15), the signals of the CC1 and CK2 service channels are transmitted, and the SC for the 1st and 16th channels of the PM are transmitted to the C1, in the C2 - for the 2nd and 17th, etc. . Intervals P3, P4, P6 and P7 are free. From the point of view of the transfer of the telephone channel: the telephone channel is an 8-bit count. The payload is a conversation between two subscribers. In addition, service information (dialing, hang up, etc.) - control and interaction signals (WMS) is transmitted. To transmit such signals, it is enough to repeat them 1 time in 15 cycles, and each SUV will occupy 4 bits (SUV for a particular channel). For these purposes, the 16th channel interval was chosen. In one channel are placed SUV for two telephone channels. Because only 30 channels, two channels are used in one conversation, then the cycle needs to be repeated 15 times, therefore, from Ts1 to Ts15, we transmit all the information about SUV. Thus, it is necessary to determine the cycle number. For these purposes, the zero cycle contains a superframe CC (“0000” in 1 four bytes –MFAS). In the 6th bit, the loss of the superframe (LOM) is transmitted.

I had to deal with people who, trying to explain the structure of the E1 stream, represented it as a pipe, where 32 smaller pipes (32 timeslots) were crammed in, this is quite obvious, but absolutely wrong. in PDH, data transfer is carried out sequentially, bit by bit, and not in parallel.

To control transmission errors, the first bit of the zero channel interval is used.

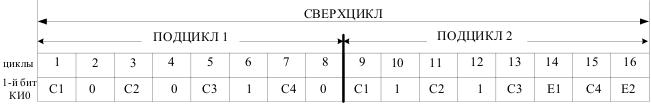

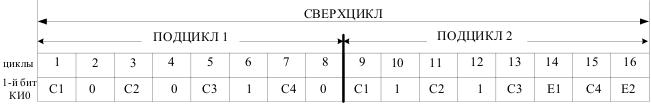

The contents of the first bit KI0 in various subcycles.

By the polynom x4 + x + 1, the presence of an error is determined. Bits C1, C2, C3, C4 is the remainder of dividing the subcycle (8 cycles) by the polynomial x4 + x + 1. The result is inserted into the next subcycle. Accept the value of the 1st subcycle, compare it with the 2nd. If there is a mismatch, an error message is displayed. Bits E1 and E2 are designed to send error messages to the transmitter side of the first and second cycles (E1 for the first, E2 for the second). For correct processing in even cycles (except 14 and 16), a cyclic (001011) clock signal is introduced for error control.

The physical layer includes a description of the electrical parameters of the interfaces and the parameters of the transmission signals, including the structure of the linear code. These parameters are described in ITU-T Recommendation G.703.

The following physical interfaces are defined for the PDH:

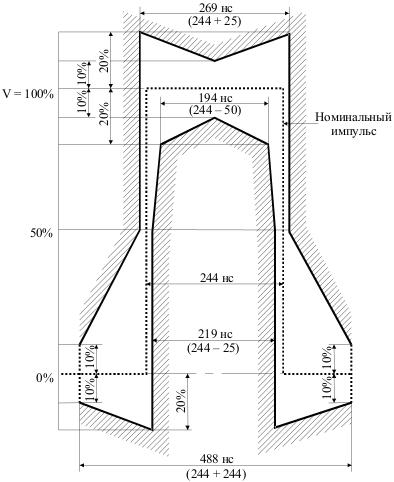

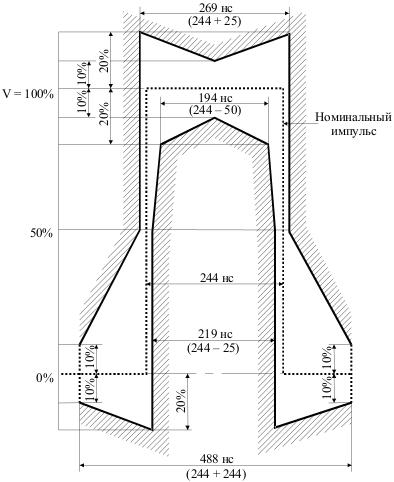

The pulse mask of the physical interface stream 2048 kbit / s.

On this, I think you can stop. Thank you all for your attention, I hope you were interested.Subscribe, put huskies ... In the article I tried to explain as much information as possible in the simplest possible way (I don’t know if I succeeded) without diving too deep into the details of DSP structures and in particular the E1 stream.

If you like the article, then I can try to write the same about the synchronous digital hierarchy (SDH) [foreign sources: Synchronous Digital Hierarchy (SDH)] and the synchronous transport module (STM) [foreign sources: Synchronous Transport Module (STM)] - STM- one.

Measurement technologies of the primary network - I.G. Cormorants;

Modern high-speed digital telecommunication systems - VN Gordienko.

UPD: Slightly supplemented the article with English terms and abbreviations.

During the study of Digital transmission systems, as well as on the recommendation of a mentor, in order to better understand the material being studied and put everything on the shelves, I will try to explain this material to you, if I succeed in this, then we can assume that I learned it well. I hope you will be interested.

In the article I will tell briefly about the DSP and the features of their construction, PDH (PDH) and in more detail about the flow of E1 and its structure.

Digital transmission systems

Features of building digital transmission systems

It will not be news for anyone that the main trend in the development of telecommunications worldwide is the digitalization of communication networks, which involves building a network based on digital transmission and switching methods. This is due to the following significant advantages of digital transfer methods over analog ones:

High noise immunity.

- Weak dependence of transmission quality on the length of the communication line.

- The stability of the parameters of DSP channels.

- The efficiency of the use of channel capacity for the transmission of discrete signals.

- The possibility of building a digital communication network.

- High technical and economic indicators.

')

The requirements for DSPs are defined in the ITU-T G-series recommendations; this recommendation also presents two types of DSP hierarchies: plesiochronous digital hierarchy (PDH) and synchronous digital hierarchy (SDH). The primary signal for all types of DSPs is a digital stream with a transfer rate of 64 Kbps, called the main digital channel (BCC) [foreign sources: Basic Digital Circuit (BDC)] , Habré already described how the digitization of the PM channels is done in this article . The principle of time division multiplexing (WRC) [foreign sources: Time Division Multiply Access (TDMA), or Time Division Multiplexing (TDM)] is used to combine BCC signals into group high-speed digital signals.

Plesiochronous digital hierarchy

The historically first plesiochronous digital hierarchy (PDH) [foreign sources: Plesiochronous Digital Hierarchy (PDH)] has European, North American, and Japanese varieties.

| Hierarchy level | Europe | North America | Japan | |||

| Mbit / s speed | Coeff. Multiplex. | Mbit / s speed | Coeff. Multiplex. | Mbit / s speed | Coeff. Multiplex. | |

| 0 | 0.064 | - | 0.064 | - | 0.064 | - |

| one | 2,048 | thirty | 1.554 | 24 | 1.554 | 24 |

| 2 | 8,448 | four | 6.312 | four | 6.312 | four |

| 3 | 34,368 | four | 44,736 | 7 | 32,064 | five |

| four | 139,264 | four | - | - | 97,728 | 3 |

For digital streams, PDHI use the corresponding designations, for North American - T, Japanese - J (DS), European - E. Digital streams of the first level are designated as T1, E1, J1 of the second T2, E2, J2, etc ...

The European PDH has been adopted for use on Russian telecommunication networks.

The communication networks of the Russian Federation are operated by DSP PDH of domestic and foreign production. Domestic systems are called DSP with PCM (digital transmission systems with pulse code modulation). Instead of the hierarchy level, the system designation indicates the number of information BCCs of this system. Thus, the DSP of the first level of the hierarchy is designated ICM-30, the second - ICM-120, etc.

The basic principles of synchronization

In the plesiochronous, “as if synchronous,” DSPs, the principle of the WRC is used, so correct restoration of the original signals at the reception is possible only with synchronous and in-phase operation of the generator equipment at the transmitting and receiving stations. For normal operation of a plesiochronous DSP, the following types of synchronization should be provided:

Clock synchronization ensures equal processing speeds of digital signals in linear and station regenerators, codecs and other DSP devices that process the signal with a clock frequency Ft.

There are several options for clock synchronization:

- Co-directional interface: additional transmission of clock signals is carried out along individual lines;

- Anti-directional interface: one unit (controlling) sets the other (subordinate) working clock frequency;

- Interface with centralized setting device (master oscillator): master oscillator performs clocking of all equipment units.

Loop synchronization is as follows. At the transmitting station, a digital synchronization signal (CC) is introduced into the group digital signal at the beginning of the cycle. At the receiving station, a clock signal receiver (PSS) is installed, which extracts the frame clock signal from the digital digital signal and thereby determines the start of the transmission cycle.

E1 flow

E1 flow structure.

There are 3 types of flow E1:

- Unstructured (there is no division into channel intervals KI [foreign sources: Time Slot] , the logical structure is not allocated; the data stream at a speed of 2048 Kbit / s); used when transferring data;

- Flow with cyclic structure (time slots are allocated, but control and interaction signals (WMS) are not transmitted) - PCM-31;

- The flow with a superframe structure (both cyclical and sufrequency structure is distinguished) - ICM-30.

Consider the frame structure of the transmission DSP PCM-30.

The E1 flow structure is defined in ITU-T Recommendation G.704. This stream is called the primary digital stream and is organized by combining 30 information BCC.

The linear signal of the system is built on the basis of superframes, cycles, channel and clock intervals, as shown in the figure above (0/1 designation corresponds to the transmission of a random signal in a given clock interval). The transmission super cycle (SC) corresponds to the minimum time interval for which one count of each of the 60 signaling channels (CK) and alarm transmission channels is transmitted (loss of frame or frame synchronization). Duration SC SC = 2ms. A supercycle consists of 16 transmission cycles (from Ts0 to Ts15). The cycle time TC = 125 µs and corresponds to the sampling interval of the channel of the PM with a frequency of 8 kHz. Each cycle is subdivided into 32 channel intervals (timeslot) with a duration Tq = 3.906 μs. Channel intervals KI1-KI15, KI17-KI31 are reserved for the transmission of information signals. KI0 and KI16 - under the transfer of proprietary information. Each channel interval consists of eight discharge intervals (P1-P8) with a duration of Tr = 488ns. Half of the discharge interval can be occupied by a rectangular pulse with a duration of Ti = 244 ns during transmission in a given discharge unit (there is no pulse in the discharge interval during transmission of zero). Intervals KI0 even-numbered cycles are intended to transmit the cyclic sync signal (DSS), having the form 0011011 and occupying the intervals P2 - P8. In the P1 interval of all cycles, the information of the permanent data transmission channel (DI) is transmitted. In odd cycles, the P3 and P6 CI0 intervals are used to transmit information about the loss of frame synchronization (Avar. CA - LOF) and reducing the residual attenuation of the channels to a value at which self-excitation may occur (OST). Intervals P4, P5, P7 and P8 are free, they are occupied by single signals to improve the operation of the clock frequency selectors. In the interval CI16 of the zero cycle (C0), a cyclic signal of the type 0000 (P1 - P4) is transmitted, as well as a signal on the loss of superframe synchronization (P6 - Avar. SDS - LOM). The remaining three bit intervals are free. In the channel interval CI16 of the remaining cycles (C1 - C15), the signals of the CC1 and CK2 service channels are transmitted, and the SC for the 1st and 16th channels of the PM are transmitted to the C1, in the C2 - for the 2nd and 17th, etc. . Intervals P3, P4, P6 and P7 are free. From the point of view of the transfer of the telephone channel: the telephone channel is an 8-bit count. The payload is a conversation between two subscribers. In addition, service information (dialing, hang up, etc.) - control and interaction signals (WMS) is transmitted. To transmit such signals, it is enough to repeat them 1 time in 15 cycles, and each SUV will occupy 4 bits (SUV for a particular channel). For these purposes, the 16th channel interval was chosen. In one channel are placed SUV for two telephone channels. Because only 30 channels, two channels are used in one conversation, then the cycle needs to be repeated 15 times, therefore, from Ts1 to Ts15, we transmit all the information about SUV. Thus, it is necessary to determine the cycle number. For these purposes, the zero cycle contains a superframe CC (“0000” in 1 four bytes –MFAS). In the 6th bit, the loss of the superframe (LOM) is transmitted.

I had to deal with people who, trying to explain the structure of the E1 stream, represented it as a pipe, where 32 smaller pipes (32 timeslots) were crammed in, this is quite obvious, but absolutely wrong. in PDH, data transfer is carried out sequentially, bit by bit, and not in parallel.

Transmission error control

To control transmission errors, the first bit of the zero channel interval is used.

The contents of the first bit KI0 in various subcycles.

By the polynom x4 + x + 1, the presence of an error is determined. Bits C1, C2, C3, C4 is the remainder of dividing the subcycle (8 cycles) by the polynomial x4 + x + 1. The result is inserted into the next subcycle. Accept the value of the 1st subcycle, compare it with the 2nd. If there is a mismatch, an error message is displayed. Bits E1 and E2 are designed to send error messages to the transmitter side of the first and second cycles (E1 for the first, E2 for the second). For correct processing in even cycles (except 14 and 16), a cyclic (001011) clock signal is introduced for error control.

Physical layer OSI model in PDH

The physical layer includes a description of the electrical parameters of the interfaces and the parameters of the transmission signals, including the structure of the linear code. These parameters are described in ITU-T Recommendation G.703.

The following physical interfaces are defined for the PDH:

- 0 - symmetrical pair (120 Ohm);

- 1 - coaxial cable (75 Ohm) or symmetrical pair (120 Ohm);

- E2, E3, E4 - coaxial cable (75 Ohm).

- E0 - AMI;

- E1, E2, E3 - HDB3;

- E4 - CMI.

The pulse mask of the physical interface stream 2048 kbit / s.

On this, I think you can stop. Thank you all for your attention, I hope you were interested.

If you like the article, then I can try to write the same about the synchronous digital hierarchy (SDH) [foreign sources: Synchronous Digital Hierarchy (SDH)] and the synchronous transport module (STM) [foreign sources: Synchronous Transport Module (STM)] - STM- one.

Literature

Measurement technologies of the primary network - I.G. Cormorants;

Modern high-speed digital telecommunication systems - VN Gordienko.

UPD: Slightly supplemented the article with English terms and abbreviations.

Source: https://habr.com/ru/post/141709/

All Articles