Itanium Poulson: what's new

In early 2011, Intel announced the upcoming release of the Itanium generation stone, codenamed “Poulson” at the Solid State Circuit, and more recently, during the HotChips conference held at Stanford University, Intel revealed the first details of this processor.

It can be interesting to watch the development of the Itanium line for those who use Intel Xeon-based solutions, since many developments are transferred from Itanium to new versions of Xeon's (such as QuickPath and Scalable Memory Interconnects, Intel 7500 Scalable Memory Buffer and the use of DDR3 ).

')

The key features of the processor are: a new architecture, twice the number of processor cores, twice the number of processing capabilities.

The new chip will carry eight processor cores on the substrate and will be manufactured using the 32-nm process technology, which will result in 3.1 billion transistors in the CPU area (for comparison, in the second-generation Core i7 about a billion semiconductors).

Having examined the new processor more closely, the following features can be noted, generally falling under the “RAS” direction: Reliability (availability), Availability (availability) and Serviceability (ability).

1. Increased fault tolerance of the processor due to the technology of re-execution of commands “Instruction Replay”, based on the new architecture of the command pipeline. About it in the blog on Habré the HP company which is also interested in improvement of technologies of fault tolerance wrote . The new Itanium will be the first processor to use this technology.

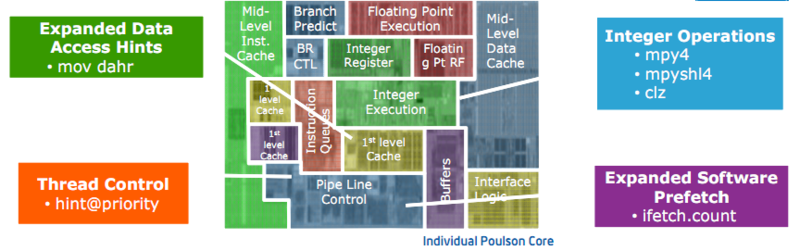

The changes will affect almost all the main structures in the Poulson architecture: LLC, MLI, MLD, IEU, FPU.

2. An improved command buffer implements Hyper-Threading multithreading capabilities, supporting the execution of command flows in two domains. The EPIC architecture used in IA64-based processors has always had extensive support for parallelization, and in Poulson this integration will become even more powerful due to support for Dual Domain Multithreading, which separately processes two command streams.

The main innovations of multi-threading are as follows: dual threaded register files, dual threaded data side Translation buffers (TLB).

3. New processor instructions: commands for working with integers (mpy4, mpyshl4, clz); commands on the technology of parallelization and multithreading Data Access Hints (mov dahr), Expanded Software Prefetch (ifetch.count) and Thread Control (hint @ priority). All of these innovations serve the same goal — to allow the Itanium architecture to grow naturally with future improvements.

The new Itanium has 54 MB of memory (50 MB of SRAM), and improved QPI and SMI work will bring a 33% increase in the performance of the entire system.

As you can see, most of the changes are connected with the desire to get the full return from 8 cores and the ability to execute up to 12 instructions per clock, due to the maximum number of parallel (and architectural - and perpendicular co) processes. Despite the increased power, Intel engineers were able to achieve lower CPU power consumption.

In parallel with the development of Poulson, Intel is occupied by another Itanium chip - Kittson. which will be presented officially later. Both new processors will be fully compatible with the current Itanium 9300 (Tukwila) series by software code, so owners of solutions based on these processors released in the past will be able to upgrade without problems for running applications.

Source: https://habr.com/ru/post/128425/

All Articles